Designing an Automotive Graphics Display Controller with Stratus HLS

Watch Video - Opens Video Player

overview

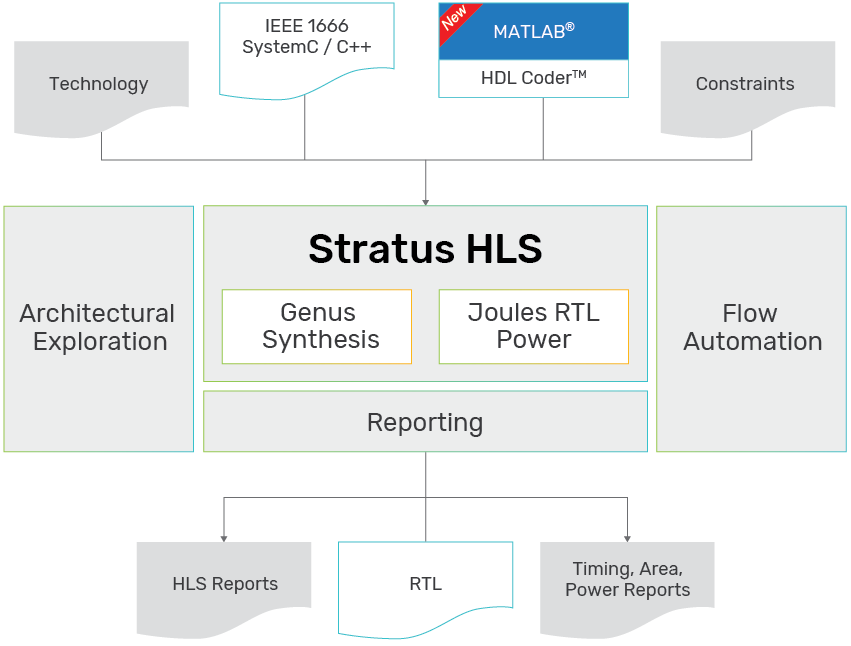

With Cadence® Stratus™ High-Level Synthesis (HLS), engineering teams can quickly design and verify high-quality RTL implementations from abstract SystemC™, C, or C++ models. The models can be easily created using the Stratus integrated design environment (IDE). Stratus synthesizable IP for SystemC provides simulation and synthesis models for common bus-based and point-to-point communication protocols as well as common mathematical operations and datatypes.

Key Benefits

Stratus HLS gives engineering teams the ability to explore hundreds of micro-architectures in a fraction of the time it takes to write and verify a single RTL description. With automated exploration and optimization, designers can quickly find the most optimal implementation.

Stratus HLS starts with transaction-level SystemC, C, or C++ descriptions. Because the micro-architecture details are defined during HLS, the source description is significantly easier to write and re-target, making your IP significantly more portable across different technologies.

Stratus HLS is highly productive and can be used interactively or via batch runs controlled via Tcl scripts. Users can define a range of constraints and automatically run high-level synthesis and adjacent tools like simulation, power analysis, and logic synthesis.

customer success

Resources

White Paper

MATLAB Integration: Accelerate Algorithm to Silicon Development with Stratus HLS

Article

Cadence Academic Network: Shift-Left Methodology for the Development of Hardware Accelerators Education Kit Is Available Now

Video

CadenceTECHTALK: From MATLAB to Optimized RTL in Minutes

Training and Support

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportFind community on the technical forums to discuss and elaborate on your design ideas.