Datasheet

Stratus High-Level Synthesis

Fastest path from specification to silicon

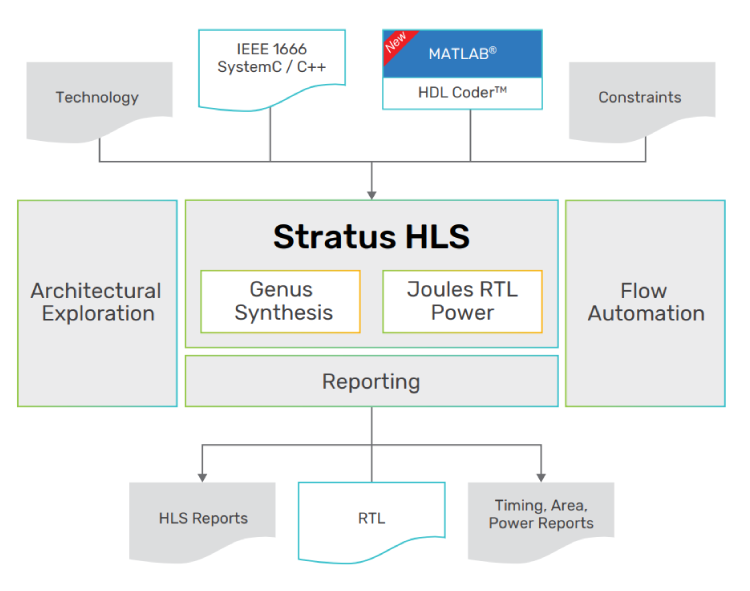

Cadence Stratus High-Level Synthesis (HLS) automatically creates high-quality register transfer level (RTL) design implementations for ASIC, system-on-chip (SoC), and FPGA targets from high-level IEEE 1666 SystemC, C++, and MATLAB descriptions. The proven successes of Stratus HLS in production designs around the world are testament to its consistently highquality results, mature feature set, and complete design coverage. While most widely used for image processing, wireless, and machine learning (ML) applications, products built with Stratus HLS technology can be found in your home, automobile, and pockets.

Overview

Overview

With Stratus HLS, engineering teams can quickly design and verify high-quality RTL implementations from abstract IEEE 1666 synthesizable SystemC, C, C++, or MATLAB models. The models can be easily created using the Stratus integrated design environment (IDE). Stratus synthesizable SystemC IP provides simulation and synthesis models for common bus-based and point-topoint communication protocols as well as common mathematical operations and datatypes.

Leveraging Cadence’s Genus synthesis and Joules power engines inside of Stratus HLS, the power, performance, and area (PPA) results are typically equal to or better than those achieved with hand-written RTL. Front-end designers get high-quality PPA estimates through turnkey integration with the Cadence digital flow.

With Stratus HLS, SystemC models can be retargeted to new technology platforms and reused more easily than traditional hand-coded RTL. The Stratus graphical user interface (GUI) also allows designers to actively and quantitatively evaluate PPA tradeoffs from within the high-level synthesis environment.

Stratus HLS automates the design and verification flow of hundreds of blocks from transaction-level models (TLMs) to gates. In addition, Stratus HLS helps with the real-world issues of engineering change orders (ECOs) and routability, both of which normally occur much later in the flow, through tight integration with the full Cadence tool flow.

Features

IEEE 1666 SystemC, C, C++ Synthesis

Stratus HLS supports industry-standard IEEE 1666 SystemC as well as C and C++ semantics.

The SystemC class library provides modularity, concurrency, and bit-accuracy, allowing designers to use familiar hierarchical decomposition techniques to manage design complexity. By supporting hierarchy and multiple threads, SystemC allows design and verification of algorithms and their interfaces operating concurrently.

Stratus HLS also allows C or C++ algorithmic code to be automatically put into the context of a hardware module with hardware interfaces.

Broad Applicability

Silicon built with Stratus HLS is in billions of products worldwide. While most widely used for image processing, wireless, and ML applications, products built with Stratus HLS can be found in a wide range of silicon applications.

Stratus HLS supports untimed and timed SystemC and C++ models, including a mix of both, providing maximum flexibility to the designer. The output can be fully pipelined (new data each cycle), pipelined at reduced throughput (new data every n cycles), or unpipelined. It also supports multiple pipeline stalling modes, including hard stalling and soft stalling, as well as pipeline draining and bubble squashing. Stratus HLS ensures the generated RTL finitestate machine (FSM), datapath, and memory interfaces correctly implement even the most complex stalling scenarios.

Stratus IP building blocks include application-specific IP as well as general-purpose IP. For example, Stratus line buffer IP is widely used in imaging and video applications, complex datatypes are widely used in wireless applications, and support for floating-point type bfloat is used in ML and artificial intelligence (AI) applications. Meanwhile, all designs may leverage point-to-point and bus-based communication IP.

Hierarchical Design

Stratus HLS is applicable to a single block or complex hierarchy of modules, including both HLS and RTL blocks. Stratus design and verification automation allows the designer to synthesize one, some, or all of the modules and do mixed SystemC and RTL simulation and verification.

Each module may contain one or more SystemC threads and/or methods specified by the user. By using the Stratus communication IP, each module may be simulated as SystemC or RTL. The Stratus communication IP allows mixed simulation of SystemC and RTL, eliminating the need for complex co-simulation wrappers. Stratus clock-domain crossing (CDC) IP ensures modules can communicate correctly across clock boundaries.

Stratus HLS also supports creating hierarchical modules. For example, the designer may want a function to be implemented as a separate FSM and datapath. With Stratus HLS, this can be done with a Tcl directive instead of a complex rewrite of the SystemC code.

Stratus HLS fully supports the use of memories in the hierarchy, including the ability to promote memory test ports to the top-level module or even extract the memory to be outside of the module hierarchy.

Integrated with the Cadence verification suite, Stratus HLS supports automated mixed-language (SystemC and RTL) verification and debug including assertions, debugging, waveforms, and linkage back to the original SystemC design.

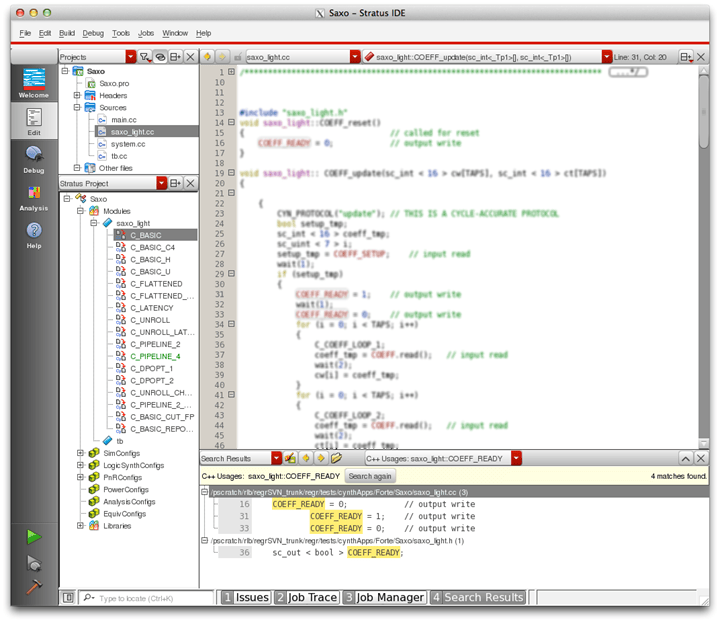

GUI

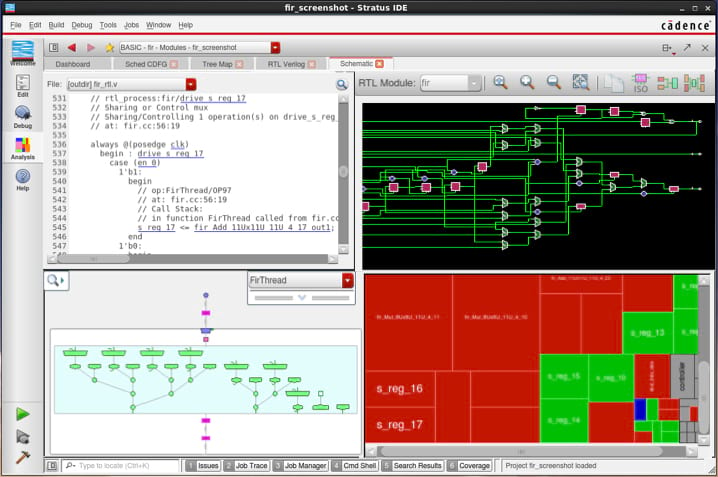

The Stratus GUI incorporates an IDE, making SystemC development easy and intuitive for new users and advanced users alike. In addition to typical IDE features, the Stratus IDE makes it easy to quickly create new models using pre-defined design templates to reduce design and debugging time.

The Stratus analysis environment includes SystemC and RTL source linking, control and dataflow graphs, schematic viewer, and pipeline analysis, as well as QoR reporting and visualization to judge the impact of architectural optimizations. Although most commonly used via the GUI, this analysis is also available via the Stratus Tcl API.

IP Building Blocks

Stratus HLS includes an IP library and the Stratus interface generator to give designers synthesizable building blocks to jump-start their designs. Because these pre-designed optimized elements are implemented in high-level SystemC code, they can be used without performance or area penalties. The result is truly reusable design IP that accelerates the design and verification process.

The Stratus HLS IP library contains high-speed simulation models and bit-accurate synthesizable models.

Design and Verification Flow Automation

Stratus HLS comes with a fully integrated automation system. One short Tcl file can configure and automate all of the following.

This automation allows designers to use Stratus HLS to explore multiple architectures and implementations while improving verification by providing a consistent environment from early TLM models through gates.

ECO Support

Changes to the design can become necessary at any point during the design flow. When those changes come late, the ECO mode of Stratus HLS can enable you to still meet your deadlines.

Rather than creating new RTL and completely redoing the entire RTL-GDSII implementation, Stratus HLS creates an RTL implementation with minimal changes so that Cadence Conformal ECO Designer can create an ECO patch to minimize the impact of the change on the design and thus the schedule.

Working in conjunction with Conformal ECO Designer, the patch can be applied on the netlist, the placed design, the routed design, or even the post-mask netlist if a metal-only ECO is possible. This ensures the patch is correct and that the design still meets its quality of results goals.

Low-Power Optimization

With Stratus HLS, design teams can automate complex low-power optimizations that are often difficult or impossible to realize with hand-coded RTL, such as fine-grained and block level clock gating, FSM optimizations, and poweraware scheduling (re-ordering) of operations.

Designers can use the exploration capabilities of Stratus HLS to quickly trade off design PPA. For some applications, additional criteria may be included in the tradeoff analysis, such as ML accuracy or implementation loss for wireless applications.

These optimizations can yield power reductions of 50% or more, depending on the design.

Design Closure

Stratus HLS ensures easy timing closure for the generated RTL by exhaustively analyzing each path and scheduling operation so they fit in the given clock period.

Stratus HLS uses patented datapath optimization technology and the embedded Genus synthesis to build all datapath components, multiplexers, and registers in the specified technology library to get accurate timing and area models.

The user can control how aggressively Stratus HLS packs these operations into each clock period. Creating designs with Stratus HLS can save months of back-end effort by preventing timing closure problems.

Integration with Genus physical synthesis allows early visibility and feedback into likely congestion problems, allowing the front-end designer to avoid problems in the back-end.

Behavioral IP Reuse

Stratus HLS enables the creation and adaptation of behavioral IP, delivering on the promise of true IP reuse.

Using Stratus HLS, the verified source code can be reused without modification for widely different process technologies, clock speeds, or PPA targets. Modifications to the algorithm, architecture, or interfaces can be made incrementally at a high level, where previously they required a complete RTL rewrite.

Behavioral IP reuse with Stratus HLS significantly reduces overall design effort and maximizes return on investment (ROI).