Sigrity2017アップデートのご紹介

2017年12月13日に、“Sigrityフォーラム 2017 ~PCBからシステムレベルへ~”と題し、従来Sigrity環境としては提供していなかった筺体を含むSI/PI/EMI/熱解析向け解析環境ソリューションの紹介やSigrity™2017最新QIR (Quarterly Incremental Release) 2のリリースをはじめ、これまでのSigrity2017 QIRリリースから継続的に進化する有益な機能を取り上げたセミナーを開催いたしました。

以下、セミナーにてご紹介しましたSigrity2017の新機能や改良点の一部を説明いたします。

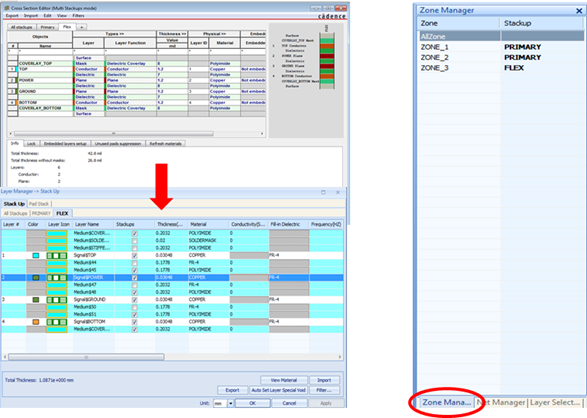

CAD Translator for Cadence Allegro/APD/SiP

以下のケイデンス・ツールの設計パラメータのサポートを開始しました。

- Backdrill

- Fillets

- Material lib

- Embedded components

- Net groups

- APD / SiP solderball / bump

- Board outline

- Multi-Zone Stackup Support

CAD Translator for 3rd party tools

以下の3rd patty CADデータのサポートを開始しました。

- Altium designs (*.pcbdoc ) サポート※

- IEEE Standard 2401 (*.xml ) サポート※

- Zuken CR5000/CR8000 (*rul, *rulf ) サポート

- Zuken CR8000 (*.sdf, *.stf ) サポート

- IPC 2581 (*.xml) サポート※

※Sigrityアプリケーションから直接読み込み時のみ

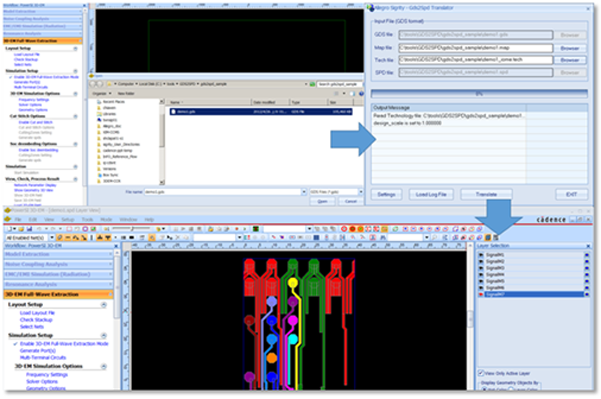

CAD Translator for IC data

GDSフォーマットデータのサポートを開始しました。(Map/Techファイル必須)

Sigrity PowerSI Technology

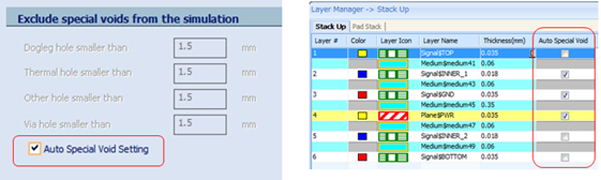

Auto Special Void Setting

上下層にTraceが配線されているShapeのVoidに対して、自動的にSpecial Voidとして処理されます。それ以外は、Normal Voidとして処理され、設定の手間とモデリング時間を削減することができます。また、Optionウィンドウ以外に、Stack upウィンドウで各層ごとに個別指定することも可能です。

New Port Generation workflow for improved low frequency accuracy

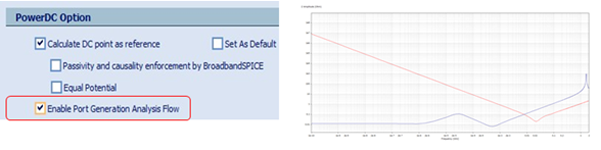

•Enable Port Generation Analysis Flow

低周波帯域でのCapacitorモデルと電源インピーダンス差による反射誤差を低減させるため、2-nodesのCapacitor部品がLinkする個所にPortを代替接続し、Sパラメータを算出します。次に、この代替Port部へCapacitorモデルを接続し直し、再度算出したSパラメータ結果を表示します。

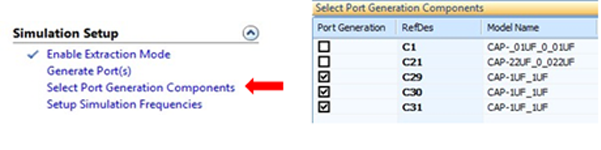

• Select Port Generation Components

Model Extraction ワークフローに追加で表示されます。クリックしますと、Componentsウィンドウが表示され、チェックされた部品へ代替Portを自動設定します。(注:2-nodes部品のみ)

Sigrity PowerDC Technology

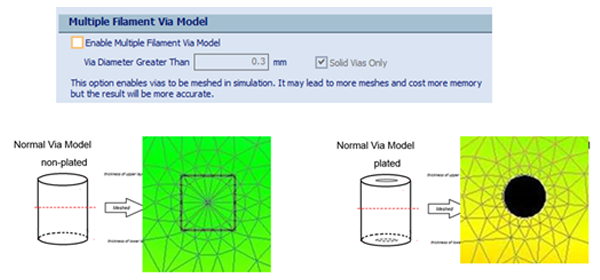

Support to Mesh All Vias in 3D for IR Drop Analysis

ビアは、通常IRドロップ解析時にメッシュ化されませんが、このオプションをチェックしますと、条件を満たすビアが3Dメッシュで処理されます。

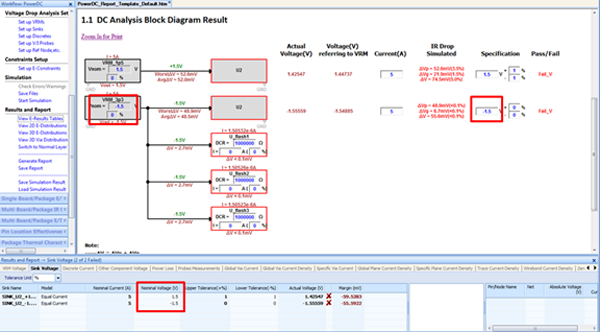

Support Negative Nominal Voltage

マイナスの電圧値を指定することが可能となりました。

PowerSI 3D EM Extraction Option (3D-EM)

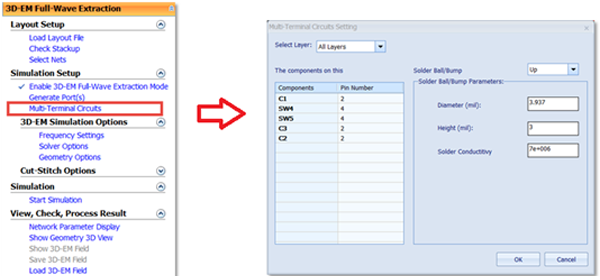

Multi-terminal SPICE model circuit support

3端子回路以上の部品モデルが適用可能(Sigrity2016までは2端子回路のみ)となりました。ただし、その部品モデル用に追加される層への接続用Solder Bumpパラメータを入力する必要があります。

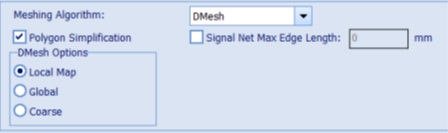

New Mesh Algorithm DMesh Added

既存のDefault Meshによる解析結果は精度が高いのですが、高密度のInitial Meshが生成されてしまうためその後のプロセスにおいての計算に時間がかかってしまいます。そのため、新しいメッシュ・アルゴリズムDMeshが追加されました。色々なレイアウトデザインに対して、メッシュ・アルゴリズム比較した解析検証において、DMeshのパフォーマンス(精度を含む)はDefaultやSigma Meshを上回っております。

Sigrity Speed2000 Technology

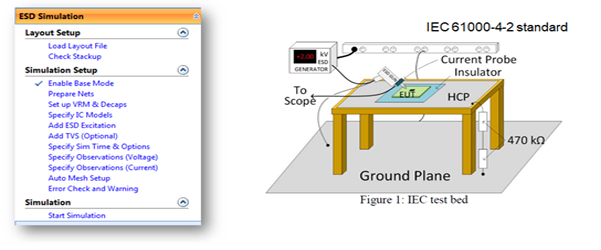

ESD simulation workflow

新しいESDシミュレーションのワークフローを追加しました。静電気放電(ESD)による接触、電気的短絡、絶縁破壊によって引き起こされる2つの帯電した物体間の急激な電気の流れを解析することが可能です。

日本ケイデンス・デザイン・システムズ社

SPB / Allegro, OrCAD, Sigrity and ICP Products

イノテック株式会社

ICソリューション本部

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues