在制造前,验证系统级芯片 (SoC) 设计功能是否正常是一项艰巨的任务,需要用到高性能计算 (HPC)。工程师可以采用多种方式来解决这一问题,因为验证每个状态是不现实的,但这些方法背后最常用的技术是逻辑仿真。

在 EDA 计算工作负载中,SoC 验证任务占到了 70% 以上,是数据中心增长和转型的关键驱动因素。数据中心需要计算密集型平台,并针对各类工作负载进行性能提升优化,以最低的成本最有效地部署和管理这些工作负载。一些数据中心包含基于 Arm® 的服务器,可以利用数以万计的多核 CPU 来执行海量 HPC 工作负载,如验证移动、物联网、云、5G 和其他应用的 SoC 所需的工作负载。

由多家企业组成的生态系统,解决您的 SoC 验证计算需求

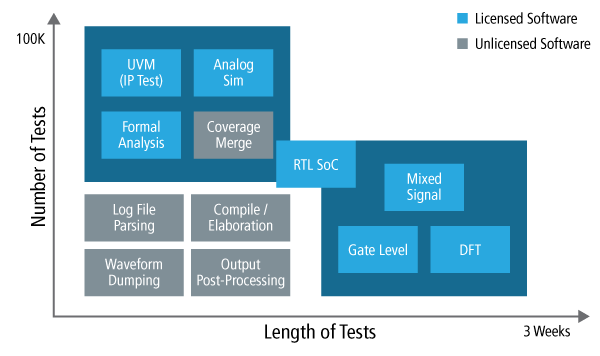

Cadence 与 Arm、HPE、Marvell 等其他企业合作,竭力满足在基于 Arm 平台的服务器数据中心验证 SoC 的计算需求。验证任务一般分为两类:第一类是简短的测试,用于验证 IP 模块。这些任务往往可以在一个核上轻松运行,并使用服务器内存的一小部分,这意味着服务器中的每个核都会运行其中的一项任务,并获得很高的吞吐量。另一类任务的工作量很大,可能运行几个小时到几周,占用服务器的大部分或全部内存。对于这些任务,它们要么在单个核上运行,并使用服务器的全部内存,要么借助 Cadence® Xcelium™ 多核仿真,让工作量分布在多个核上,以便加快运行速度。除此之外,还有许多其他验证工作负载是无需许可的,或不受许可的限制,包括编译/链接、覆盖率合并、输出后处理等等。这些工作负载也需要使用数据中心中的计算资源。

应用 Xcelium 仿真和 Arm 服务器

在基于 Arm 的服务器上原生运行的综合验证套件,更有效地执行高吞吐量和高容量工作负载,从而进一步扩大计算优势,减少 SoC 验证的整体时间和成本。

Xcelium 仿真既提供了更快的单核引擎,以加快高吞吐量测试组的每个工作负载,又提供了多核引擎,以减少长延迟工作负载的运行时间。因此,Xcelium 仿真非常适合高核数的基于 Arm 的典型服务器。对于高吞吐量测试,高核数意味着项目可以在一组给定的服务器上并行运行更多的测试,因此项目团队可以实现更好的整体 SoC 质量,并缩短质量错误修复周转时间。对于大容量测试,Xcelium 仿真可以扩展到使用服务器上所有可用的内核,从而在项目周期的最后几天或几周的关键时间点加快回归周期。

通过将 EDA 工具移植到基于 Arm 的服务器上,Cadence 为电子行业提供了可以利用创新型 HPC 服务器的工具,以加快 SoC 的验证。