概述

低至 2nm 先进制程节点的首选合作伙伴

22nm 及以下的先进节点上进行设计的独特之处在于,除了不断增加的功耗和性能规格外,制造和可变性之间存在着深层、复杂的相互依赖性。需要解决的问题包括:

- 多重图案技术 (MPT) 和色彩感知的物理设计,包括双重、三重、四重和五重图案

- 布局依赖效应 (LDE) 和密度梯度效应 (DGE),其中布局环境(放置在靠近器件的位置)对器件性能的影响高达 30%

- 复杂的颜色感知定制布线

- 物理设计规则数量呈指数增长

- 器件变化和灵敏度

核心优势

提高先进节点的设计效率,在规定时间内将产品推向市场

提升硅品质

扩展至数千次仿真,应对最激进的先进节点工艺挑战

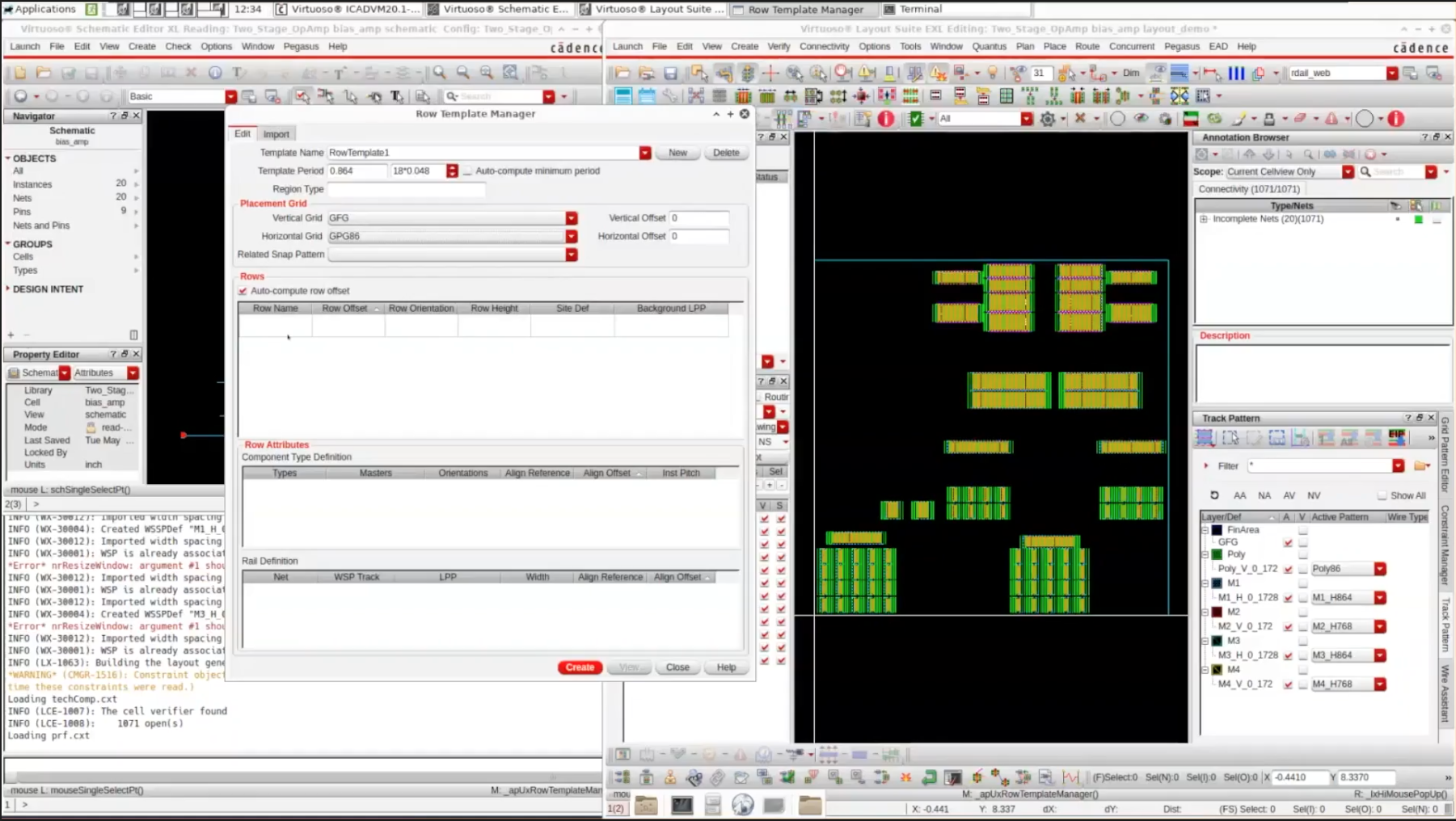

通过自动化提高生产力

采用新的设计方法,借助有针对性的自动化技术,与采用传统设计工具和流程相比,工作效率提高了 10 倍之多

通过设计迁移重用先前经验

将设计和 layout 从一个制程节点迁移到另一个制程节点,快速启动新设计

避免代价高昂的重新设计

与领先的代工厂密切合作,在设计流程中提前预测和管理工艺变化

可靠的解决方案

从 FinFET 到 GAAFET 等先进技术均获得所有主要代工厂的认证

主要功能

业界领先的方法,助力克服先进节点工艺中独特的设计挑战

资源

浏览推荐资源

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums