High-Level Synthesis

What is High-Level Synthesis?

High-level synthesis is the process of taking an abstract functional-only design description and translating and optimizing it into a logic-synthesizable register transfer language (RTL) description. High-level synthesis tools perform numerous optimizations such as scheduling and resource sharing to improve the power, performance, and area (PPA) of the design.

How Does High-Level Synthesis Work?

High-level synthesis tools work by converting an abstract functional description into a language-independent control-data-flow-graph (CDFG) that represents the flow of data and processing defined by the source description. Next, arithmetic operators, muxes, and design partitions are characterized to understand implementation details like timing and area. This characterization data is then used to map the operators to logic-synthesizable implementations, then schedule functionality within or across clock periods. Design space exploration is a key activity enabled by high-level synthesis solutions. Exploration is the task of applying combinations of tool settings, constraints, and synthesis directives with the goal of finding designs that best meet PPA goals.

A comparison clarifies the difference between high-level synthesis and logic synthesis. Logic synthesis takes a register transfer language (RTL) description and translates and optimizes it into a gate-level description. Logic synthesis optimizations are limited to modifying or restructuring the combinational logic between registers and cell sizing optimizations performed on cells (including registers) that implement the functions. Logic synthesis tools do not disturb the design’s schedule. High-level synthesis tools can modify the schedule. Therefore, high-level synthesis tools can impart stronger changes to the design—affecting the micro-architecture. Micro-architecture changes have a greater impact on PPA than logic restructuring and cell sizing operations performed by logic synthesis.

Why is High-Level Synthesis Important?

High-level synthesis tools are important because they improve designer productivity and they deliver improved PPA in less time vs. manual RTL design creation.

Benefits of High-Level Synthesis

The benefits of high-level synthesis are numerous and include clearer source descriptions that are closer to the design specification; fewer lines of code; faster functional verification; easier design re-use, and superior PPA in less time.

Superior PPA and Productivity vs. Manual RTL Creation

Productivity and PPA gains are a primary motivation for the adoption of high-level synthesis. By abstracting design to the functional (transactional) level and relying on automated high-level synthesis for implementation, designers can more rapidly explore and develop more optimal micro-architectures that deliver greater performance and consume less power.

More Reusable Design Descriptions

High-level design descriptions are significantly more reusable as they are free of low-level implementation details. These low-level implementation details constrain the design such that it can be implemented in a specific process technology node; however, they also constrain the design such that it can’t be implemented in a more advanced technology node. Free of low-level implementation details, high-level design descriptions can be more easily re-targeted to different process technology nodes as the high-level synthesis tool optimizes the micro-architecture to meet the requirements of the target process technology.

Design Descriptions Closer to the Source

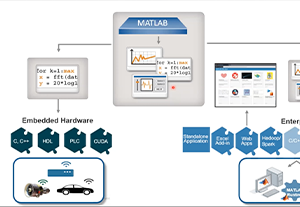

High-level synthesis tools are particularly well suited for algorithmic design descriptions. Many algorithms, such as codecs, FFTs and filters are described in C, or C++. The ability of high-level synthesis tools to read C, and C++ enable the development of design source that closely matches the original specified description. Compared to RTL, high-level design descriptions typically have an order of magnitude fewer lines of code and are significantly easier to read and maintain.

High-Level Synthesis with Cadence

Cadence Stratus High-Level Synthesis is a market leading solution with production use at 9 of the top-10 semiconductor vendors. Stratus features built-in integrations of Genus Logic Synthesis and Joules RTL Power Analysis.

Learn how to accelerate algorithm to silicon development with Stratus HLS.