Analog Defect

Key Benefits

- デバイスの製造上の故障が発生する原因を迅速に特定

- 複数の故障注入手法によるシミュレーション結果とパフォーマンスの最適化

- シミュレーションに基づいてテストプログラムの故障カバレッジを計算

- 最小限のテストセットを選択して最大限の故障カバレッジを提供

- 複数の故障モデル(オープン、ショート、ブリッジ)をサポート

- デバイスの種類、パラメータ値、終端などの基準に基づいて故障を選択

- 構築時から正確な故障検出

- 製造テスト制限(範囲、>など)に基づく故障検出

- 前処理や補正などに基づいてカスタマイズ可能な測定テスト

製造テストは、製品の市場投入における重要なステップです。テストのコストはダイの反復設計コストのかなりの部分を占めており、テスターが要する時間に正比例します。

Cadence® Legato™ Reliability Solutionは、Spectre® APSおよびVirtuosoカスタムIC設計プラットフォームをベースに構築されており、迅速、簡単に導入できます。テープアウト前に製造テストを迅速、簡単に解析し、テスト・カバレッジを向上させ、実用時の故障が発生する前に粗悪なダイを排除できます。SpectreとVirtuoso ADE Product Suiteのツール群の統合により、ミックスシグナルのコンテクストでのアナログ・パーティションの欠陥シミュレーションが可能になり、さらに、故障カバレッジ解析のシミュレーション時間を短縮する独自の高速シミュレーション・ツールを提供します。

Legato Reliability Solutionはサインオフ向けのレイアウトベースの故障解析や、テスタビリティ向けに設計の回路図ベースの故障解析をサポートします。さらに、テストプログラムが検出する故障のパーセンテージを表示するカバレッジ解析、最大のカバレッジでテスト数を最小化することでテストのコストを削減するテスト最適化、ミックスシグナルのコンテクストでのアナログ・パーティションの故障シミュレーションを提供します。

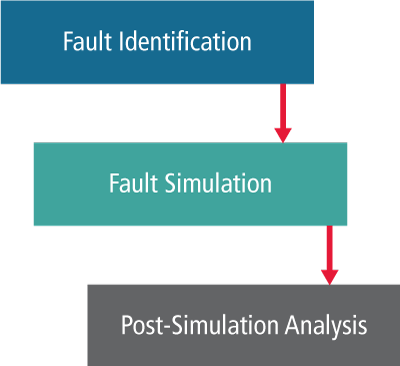

Legato Reliability Solutionは、ポストシミュレーション解析向けに、テスト制限に基づく方法と、故障結果データとゴールデンデータを比較して違いを評価する方法の2つの故障検出方法をサポートしています。ポストシミュレーションの故障検出では、Virtuoso ADE Assemblerでユーザー指定の式や仕様上の制約に基づいて検出します。測定は、要件に応じて単一信号または複数信号のいずれもカバーすることが可能です。

この独自のソリューションにより、設計サイクルの初期段階でテスタビリティの問題を検出し、テスト・カバレッジの最大化とテスト漏れの削減を実現します。