概要

2nm までのすべての新しいプロセスノードの優先パートナー

22nm以下の先端プロセスノードの設計を複雑なものにしているのは、消費電力と性能の仕様増加に加え、製造やばらつきの深く複雑な相互依存性が関係しています。懸念事項には次のようなものがあります:

- ダブル、トリプル、クアドラプル、ペンタパターンを含むマルチパターンニングテクノロジー(MPT)およびカラー認識の物理デザイン

- レイアウト依存効果(LDE)および密度勾配効果(DGE)といった、レイアウトコンテキスト(デバイスの近くに配置されるもの)がデバイスの性能に最大30%影響

- 洗練されたカラー認識のカスタム配線

- 物理的な設計ルールが指数関数的に増加

- デバイスのばらつきと感度

主な利点

先端ノードでの設計生産性の向上により、市場投入までの時間目標を達成

シリコン品質の向上

積極的に先端ノードプロセスの課題に対応するため、数千のシミュレーションをスケーリングします

自動化による生産性の向上

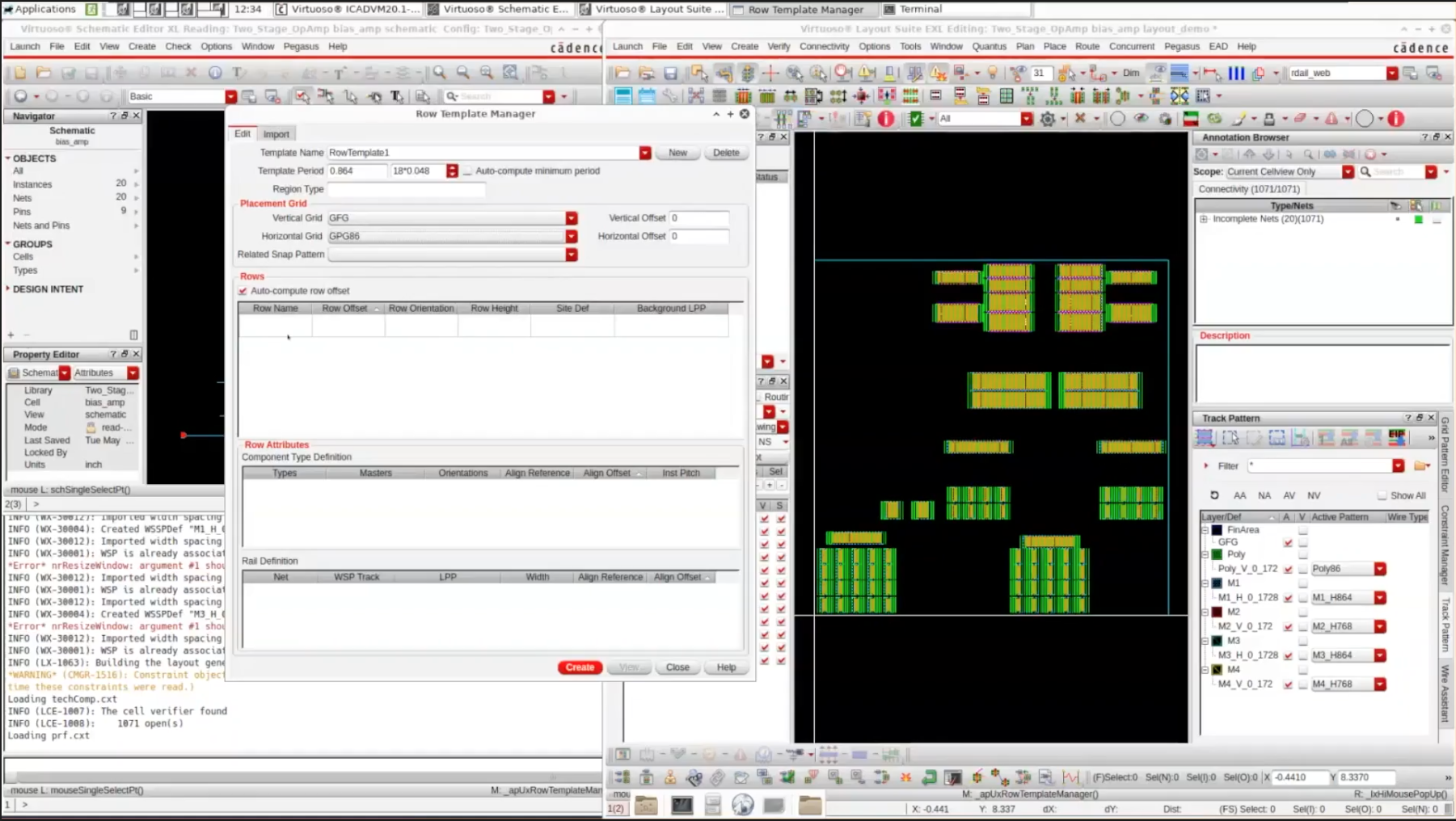

新しい設計手法と対象を絞った自動化技術により、従来の設計ツールとフローと比較して生産性が最大10倍に向上します

デザインマイグレーションによるエクスペリエンスの再利用

あるプロセスノードから別のプロセスノードへデザインとレイアウトをマイグレーションすることで、新しい設計を迅速に開始できます

コストのかかるリスピンの回避

大手ファウンドリとの緊密な連携により、設計フローの前段階でプロセスの変動を予測および管理する機能が提供されます

実証済みのソリューション

FinFETからGAAFETまでの先端テクノロジーについて、すべての主要ファウンドリに認定されています

特長

業界をリードする、先端ノードプロセス特有の設計課題を克服する手法

Resources

関連情報

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums

Related Products