Advanced Driver Assistance System

High-performance and low-power Tensilica processors and high-speed interface and memory IP for safety-compliant automotive designs

Advanced driver assistance system (ADAS) applications—essential for enhancing the driver experience and overall safety—are one of the fastest growing segments of the automotive semiconductor space. To equip future vehicles with greater levels of driver autonomy, data must be transmitted and analyzed over a network that provides deterministic, high data rate links from a multitude of different sensor types to the ECU modules. Sensor integration and system optimization are critical to achieving the high-performance and reliability necessary to address both the safety requirements and cost constraints for this market.

ADAS applications require a performance level that goes far beyond popular microcontrollers, which is leading to major disruptions in the automotive industry. Hence a new class of high-performance SoC is needed to process all sensor data and fuse them together.

High-performance ADAS SoC requirements include:

- High-compute performance: 1TMAC/sec in <1mm2 to support a digital signal processing architecture tuned to process compute-intensive algorithms, delivering an optimal SoC performance, power, and area (PPA) ratio

- Machine learning: Dedicated optimized and fully programable neural network processor cores

- High memory bandwidth: >3Gbit/s data-rate interfaces and sufficient memory space required to store and access intermediate results generated by highly complex algorithms

- High network bandwidth: 1Gbit/s or more to support a low-latency transmission of high video/image resolution or control data

- Low power consumption: <9W power consumption for ADAS applications

- Safety: Safety architecture including documentation to support ISO 26262-compliant system development

- Security: Protect safety-critical data against manipulation

Cadence® Tensilica® customizable processors scale from small efficient controllers up to compute-intensive data processing engines. The high-performance, low-power DSPs are ASIL-B-ready certified and perfectly suited for automotive applications like vision, radar, lidar, infotainment, Car2X, and more.

Imaging and Computer Vision Processing

In order to make cars safer and more comfortable, ADAS applications are becoming more and more popular. The huge amount of data generated by these systems—up to 1Gbyte/s (4TByte/day)—requires very powerful data-processing platforms with AI acceleration.

Tensilica DSPs can help to efficiently offload the host CPU and accelerate the sensor data processing to significantly reduce the power consumption. Imaging and vision algorithms can run on a DSP that’s specifically optimized for the imaging and vision functions. Regardless of the ADAS application, the Tensilica DSP can be leveraged in the sensor itself, within the ADAS electronic control unit (ECU), or in the central sensor fusion platform.

LEARN MORE

On-Device AI Processing

However, regardless of the sensor type, a machine needs to efficiently analyze the data and reliably recognize objects. Recently neural networks have become very popular for this task, enabling high object-recognition rates of more than 99%. However current solutions based on CPUs or GPUs consume too much power and therefore cannot be used in production cars.

Two key things must be provided for the efficient deployment of neural networks:

- A scalable, low-power multi-core hardware platform that is fully programmable

- A development software flow that automatically optimizes and maps neural networks on the target platform

Our Tensilica DNA 100 processor is well suited for on-device neural network inference applications spanning autonomous vehicles (AVs), ADAS, surveillance, robotics, drones, augmented reality (AR), virtual reality (VR), smartphones, smart homes, and IoT.

The DNA 100 processor delivers up to 4.7X better performance and up to 2.3X more performance per watt compared to other solutions with similar multiplier-accumulator (MAC) array sizes.

LEARN MORE

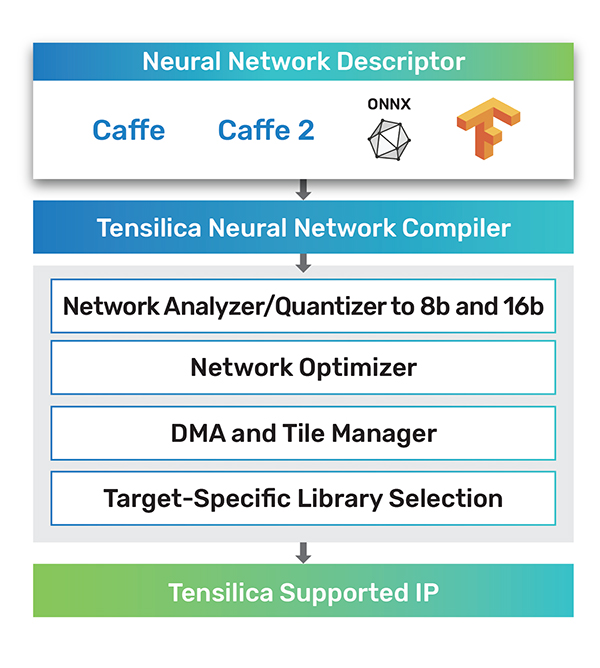

Tensilica Neural Network Compiler

The Tensilica Neural Network Compiler is an offline code generator that automatically maps pre-trained neural networks to highly optimized platform-specific executables. The Tensilica Neural Network Complier is based on the GLOW and supports ONNX input. It also supports Caffe2, Caffe, and TensorFlow. It delivers superior performance on Tensilica processors in a minimal amount of time, resulting in speedy development for our users.

Radar, Lidar, and Communications

DSP

From the dual- or quad-MAC Tensilica Fusion F1 DSP up to the super-high-performance 128-MAC Tensilica ConnX B20, these DSPs are designed for a broad range of applications that control sensors and antennas and process the data they handle.

The Tensilica Fusion and ConnX DSP families are the industry's lowest power, most compact, and best performing DSPs for applications including radar, lidar, 5G, 4G/LTE-A, Bluetooth, smartgrid, and 802.11 modems. Cadence offers several pre-designed, pre-verified DSPs to accelerate the design effort and time to market. LEARN MORE

RF/mmWave

Radar and other sensor technologies enable smart vehicles with ADAS to enhance driving safety and potentially usher in the age of self-driving cars. The mmWave spectrum provides the bandwidth for greater resolution and object detection, thus systems designers are employing phased-array antennas to produce a directive beam that can be repositioned (scanned) electronically to overcome the additional path losses, diffraction, and scattering that occur at mmWave bands. Successful implementation of the antenna system, mmWave front-end components, and radar waveform requires an integrated design approach. Radar developers require RF-aware system design software that supports radar simulations with detailed analysis of RF front-end components, including nonlinear RF chains, advanced antenna design, and channel modeling. The Cadence AWR Design Environment® platform integrates these critical radar simulation technologies while providing the necessary automation to assist the engineering team with the very complex task of managing the physical and electrical design data associated with ADAS electronics. LEARN MORE

-

Automotive White Papers

- Functional Safety Methodologies for Automotive Applications

- Automotive Functional Safety Using LBIST and Other Detection Methods

- Meeting Functional Safety Requirements Efficiently Via Electronic Design Tools and Techniques

- Improve Reliability and Redundancy of Automotive Ethernet Through Open Standards

- Enabling ISO 26262 Qualification By Using Cadence Tools

- Functional Safety Methodologies for Automotive Applications

-

Cadence 推出全方位安全解決方案,加速汽車和工業設計認證 10/19/2021

- Architecture Trends for Sensing and Computing to Enable Autonomous Driving

- Whiteboard Wednesdays - Tensilica DSPs, Sensors, and Neural Networks

- A Flexible Lockstep Architecture for ASIL Compliant DSPs and Controllers

- Dream CHIP Technologies – Automotive ADAS Chip Architecture

- AI for image classification and object recognition

- Low Power Embedded CNN with Tensilica High-Performance Vision DSP