White Paper

小芯片和异构封装正在改变系统设计与分析

在电子产品设计领域,单纯依靠工艺尺寸缩减来推动产品创新和提高系统性能已不再有效。由于与先进节点相关的成本和复杂性不断增加,所有厂商都在寻找传统系统级芯片 (System on Chip,即 SoC) 的替代品。此时,“More than Moore”(超越摩尔定律)和异构集成应运而生。这些异构的多芯粒 (multi-chiplet) 架构为最新的设计节点提供了成本更低的选择,同时仍然以物理芯粒的形式,提供基于 IP 的重用模型。现如今,封装设计已成为新一代电子产品的核心。

Overview

简介

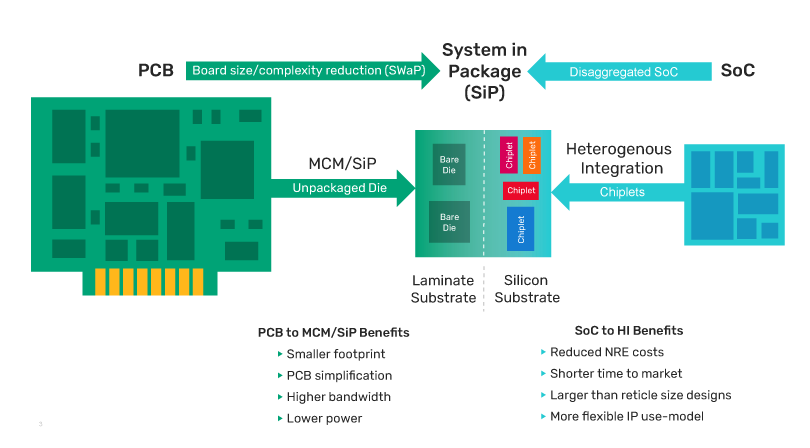

如今,半导体封装行业蓄势待发,将在未来的电子产品设计中发挥更大、更重要的作用。为了满足市场对这些异构的、基于芯粒的架构的需求(图 1),需要采用新的系统级设计方法,并以改善系统级的功率、性能和面积 (PPA) 为目标。当设计人员从单一的单片系统过渡到多芯粒架构时,所面临的第一个挑战是如何规划、管理并优化顶层设计和连接。现在,我们需要一种新颖的系统级设计管理解决方案。这个平台必须能够聚合来自集成电路 (IC) 设计师、封装设计师、甚至电路板设计师的数据,以便进行系统级优化,并为签核连接验证提供顶层网表。

传统的封装设计人员还面临着其他挑战。其中最大的挑战可能是需要将专业知识从层压基板(substrates layout) 过渡到硅基板(silicon substrates layout)。此外,硅基板(掩模)需要进行形式物理验证过程,这对当下大多数的封装设计人员来说都是一种新挑战。

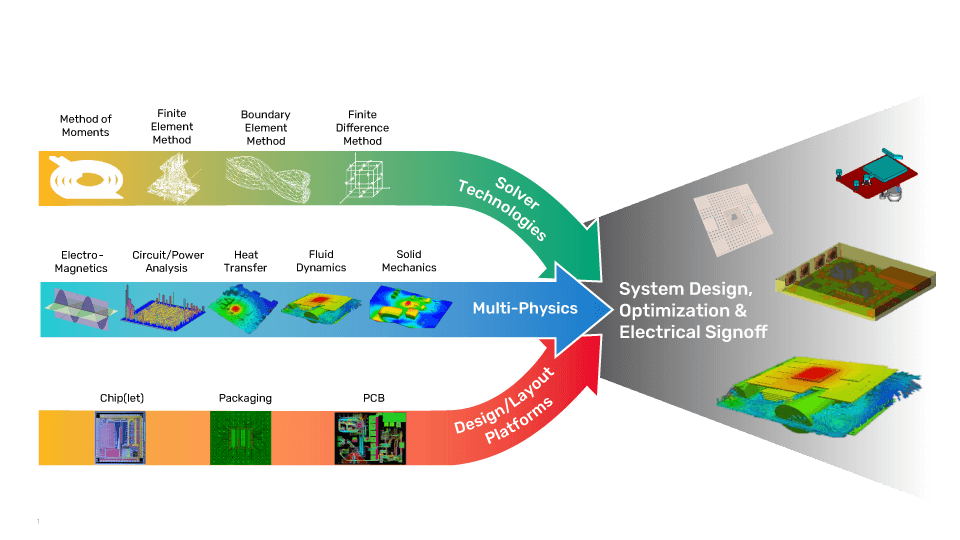

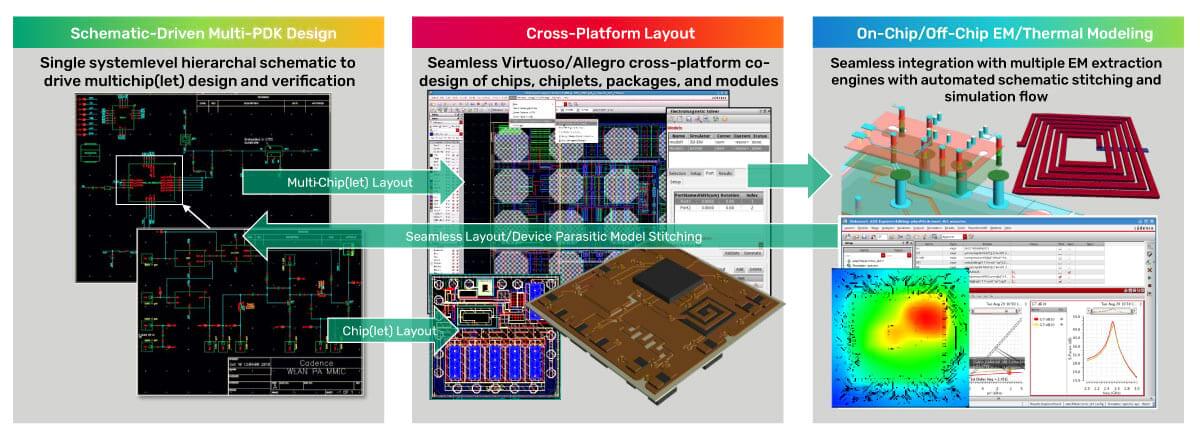

另外,随之而来的电气和热分析挑战也不容忽视。同样,设计工具必须在系统层面上提供价值。为了做到这一点,工具必须支持芯片上、芯片外系统和互连的设计内以及电-热签核(图 2)。还要对跨域耦合效应进行建模。

当涉及到芯片(芯粒)级热分析时,通常需要利用芯片(芯粒)EM-IR 解决方案来生成一个详细的热模型。然后,将该芯片(芯粒)级热模型导入系统级热分析解决方案,以便将封装和 PCB(最大的自然散热器)以及设计中的任何散热器包含在内。随后,系统级热分析工具向工程师提供热梯度信息以及热应力计算结果。此外,还可以生成最新的芯片(芯粒)热力图。热图可以反馈到芯片(芯粒)级 EM-IR 工具中,然后可以更准确地进行芯片功率分析和压降分析。此时,再一次体现了系统级建模的重要性。

总而言之,业界早就预料到摩尔定律会放缓,因此许多前沿公司都力求能超越摩尔定律。在最先进的节点上设计复杂的系统级芯片时,小规模公司几乎不可能承担收回小批量芯片生产的非经常性工程 (NRE) 成本。美国国防部 (Department of Defens,即 DoD) 公司很早就意识到了这一点,因此早早着手研发单一的单片式系统级芯片的设计替代方案。如今的先进 IC 封装是为了增加最终产品的价值,并为改善 PPA 做出贡献。电子产品设计公司正在利用封装技术来创造价值,获得不同于竞争对手的差异化优势,多芯片(芯粒)解决方案侧重于“超过摩尔定律”的愿景。换言之,当市场开始重视成本和小批量生产时,系统级封装 (System in Package,即 SiP) 成为设计先进节点单片式系统级芯片的理想选择。戈登·摩尔预见到了这种分解设计方法的可能性,并预言:“事实可能会证明,用小型功能构建大型系统,分别进行封装和互连,性价比会更高。”

芯粒和异构集成

芯粒 (chiplet) 是一个经过实际测试(制造)的 IP,拥有能在硅晶片中制造的标准通信接口,能通过提高产量和跨应用的重复使用来降低成本。基于芯粒的架构使设计人员能够利用 IP,而无需考虑它是基于何种节点或技术制造的。设计人员可以只关注 IP 或其为设计带来的附加值。这些基于芯粒的设计可以基于不同的材料,如硅、玻璃,甚至是层压板。最终,可以在较短的时间内以较低的成本构建高性能的伪 SoC。芯粒的可重复使用性有助于在设计过程中降低成本,提高产量。

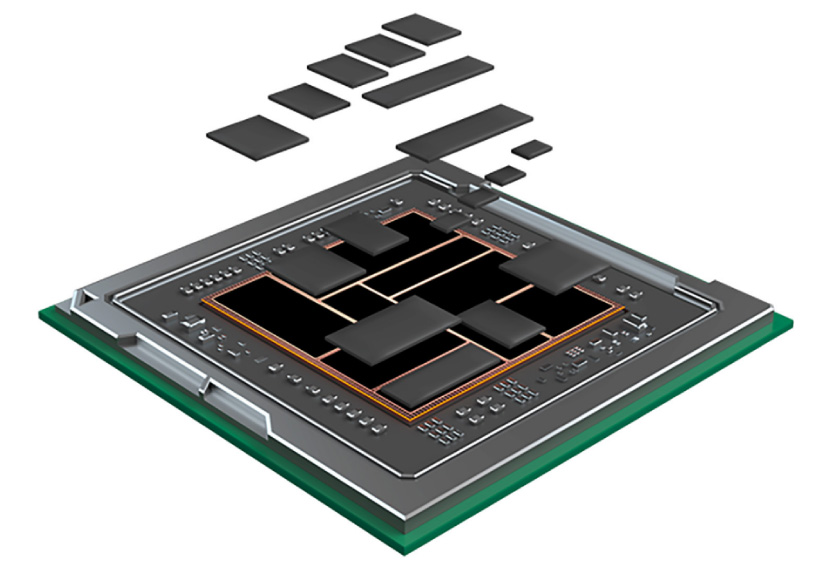

术语“异构集成”广泛用于描述由多个芯粒构建的分解系统级芯片架构(图 3)。基于芯粒的设计和系统级封装类似,只不过是将多个 IP 以芯粒的形式集成在一个基板上,而不是像通常的系统级封装那样在一个基板上集成多个裸片(包括 3D 堆叠)。这也类似于设计一个小型 PCB,因为每个芯粒都有一个共同/已知的通信接口,如 PCI Express®(PCIe、HBM 或 AIB)。异构集成提供的价值主张是:

许多领先的半导体制造商正在探索这一领域。Intel CO-EMIB 异构封装平台允许将 EMIB 和 Foveros 一同部署在同一封装中。Intel 全向互连 (Omni-Directional Interconnect,即 ODI) 技术允许顶部封装的芯片与其他芯片进行水平通信,类似于 EMIB;或类似于Foveros 通过 TSV 进行垂直通信。TSMC 的 Chip-on-Wafer-on-Substrate (CoWoS) 是另一个异构集成平台。

未来何去何从?

尽管如今的设计正在使用多芯粒技术,但大多数基于芯粒的设计是在垂直集成的公司开发的,这些公司既设计芯粒,又设计模块化或分解 SoC。为了使基于芯粒的架构成为主流,芯粒需要实现大范围供应,而为了实现商业化芯粒的愿景,需要 IP 供应商设计一种合适的商业模式。推进实现这一愿景的方法之一是制定和记录芯粒标准,如 I/O 间距、通信接口和相应的“合规套件”,以及热功耗模型等。一些组织,包括美国政府项目和标准机构,如开放计算项目/开放域特定架构 (OCP/ODSA),都在积极努力缩小芯粒的差距。

令人激动的是,这个生态系统正在逐渐形成。大型半导体代工厂如今正在自行研发先进封装,而众多支持设计团队的方法,如参考流程和制程设计套件 (PDK) 正在成为设计环境的一部分。这些概念通常在整个封装界都是缺乏的。Cadence 一直致力于与诸多领先的代工厂和外包的半导体组装和测试公司 (OSAT) 合作,开发多芯片(芯粒)封装参考流程和封装组装设计套件。这一代 SoC 工程师殚心竭虑地提高 PPA(表 1),他们对性能更低、功耗更高、面积更大并基于晶粒的架构接受程度如何,我们仍然要拭目以待。

| Monolithic SoC | Chiplet-Based | |

|---|---|---|

| 成本 | 高 | |

| Effort | 高 | |

| Risk | 高 | |

| 功耗 | Acceptable? | |

| 性能 | Acceptable? | |

| 区域 | Acceptable? |

芯粒的演变

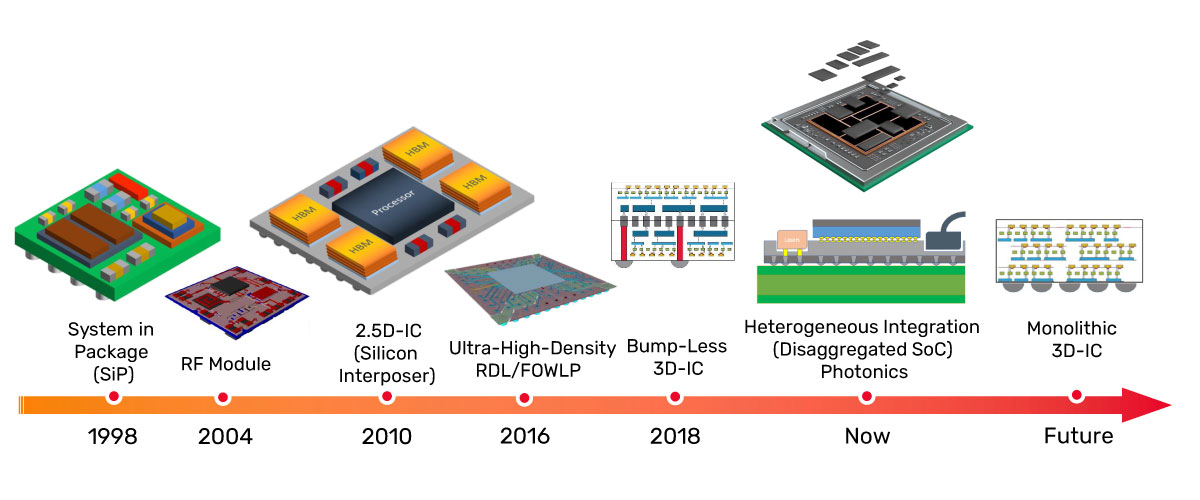

如果考虑到半导体封装近五十年来的演变(图 4),过渡到基于芯粒的架构是一种更微妙的变化,在其中的大部分时间里,异构集成多芯片产品一直都存在。EDA 公司在 20 世纪 90 年代初开始开发先进的封装工具,当时球栅阵列 (Ball Grid Array,即 BGA) 为机械引线框架封装提供了高性能、小尺寸的选择。

多芯片组件 (MCM) 可以追溯到 20 世纪 60 年代,至今在某些应用中仍然常见。20 世纪 90 年代末,随着晶圆级测试大行其道,SiP 一词开始取代 MCM 一词,而困扰 MCM 设计的 KGD 问题开始变得不那么重要。与此同时,封装设计师开始堆叠裸片,这也清楚地表明,3D 堆叠对封装设计师来说并不新鲜。在 21 世纪初的早期和中期,射频模块开始过渡到如今智能手机和手表中非常常见的层压板 BGA 封装。到了最新一代的先进多芯片封装,随着硅通孔 (TSV) 的引入,硅基材成为有机基材的高密度替代方案。最早利用基于 TSV 的中介层技术的例子是重新分区的 Xilinx FPGA。如今,这种技术通常被称为 2.5D-IC 封装。

十年前,半导体代工厂将后端设计扩展到基于硅的高级封装解决方案。基于代工厂的高密度 RDL 方法也引起了人们对扇出型晶圆级封装 (Fan-out Wafer-level Packaging ,即 FOWLP) 的重新关注,现在,随着对多芯粒的支持,人们的兴趣达到了前所未有的高度。此外,为了进一步提高带宽,3D-IC 封装(即 wafer-on-wafer 或 chip-on-wafer 堆叠)实现了新的发展。

芯粒趋势(图 4)表明,基于芯粒的新一代技术只是一种新的逻辑分区方式,与封装制造技术的进步完美契合。

异构集成工具和流程

向基于芯粒的方法过渡为芯片设计师和封装设计师的 EDA 工具带来了新的挑战。封装设计师需要熟悉实体与逻辑 (LVS) 和智能金属平衡的要求,以执行硅基板的布局和验证。当从设计单个器件过渡到设计和/或集成多个器件时,芯片设计师必须处理定义和管理顶层连接的要求。在 3D 堆栈中设计多个芯粒时,测试的格局也会发生重大变化。例如,测试堆栈顶部与外界无任何连接的芯粒。互联和验证具有多个芯粒的设计将为 IC 设计团队和封装设计师带来新的挑战。有些设计工具和方法已经扩展到支持多芯粒技术,并对项目的成败起着关键作用。

从 EDA 工具供应商的角度来看,开发跨域设计流程非常重要,这可以为用户提供一个平台,用于在芯粒、中介层、封装基板和电路板之间实现无缝规划、设计、分析和验证。这个平台应该为设计基于多芯粒的封装提供许多独特功能(图 5),首先是完整多芯粒设计的单一逻辑分层表示,从每个芯粒的晶体管水平一直到完整的系统级设计。这个系统级原理图是无缝电路布局验证和功能验证的基础,理想情况下应包括跨芯粒、中介层和封装基板的布局寄生。如果用户需要,甚至还应该延伸到 PCB。

结论

从上面讨论的系统级设计框架来看,用户应该能够跨技术或节点设计和/或导入多个芯片或芯粒。然后,设计人员将每个芯粒原理图符号实例化到顶层的系统级原理图中,然后轻松从系统级库中添加额外的封装/电路板级器件。该原理图有多种用途,包括系统感知的功能仿真,但也许最重要的是提供“黄金参考”网表,可用于对整个系统级设计进行 LVS 检查。这种方法为设计人员提供了系统级签核的信心,在进行芯粒签核时也可拥有十足把握。