Datasheet

Cadence Virtuoso Digital Implementation

面向混合信号设计的时序驱动数字模块实现方法

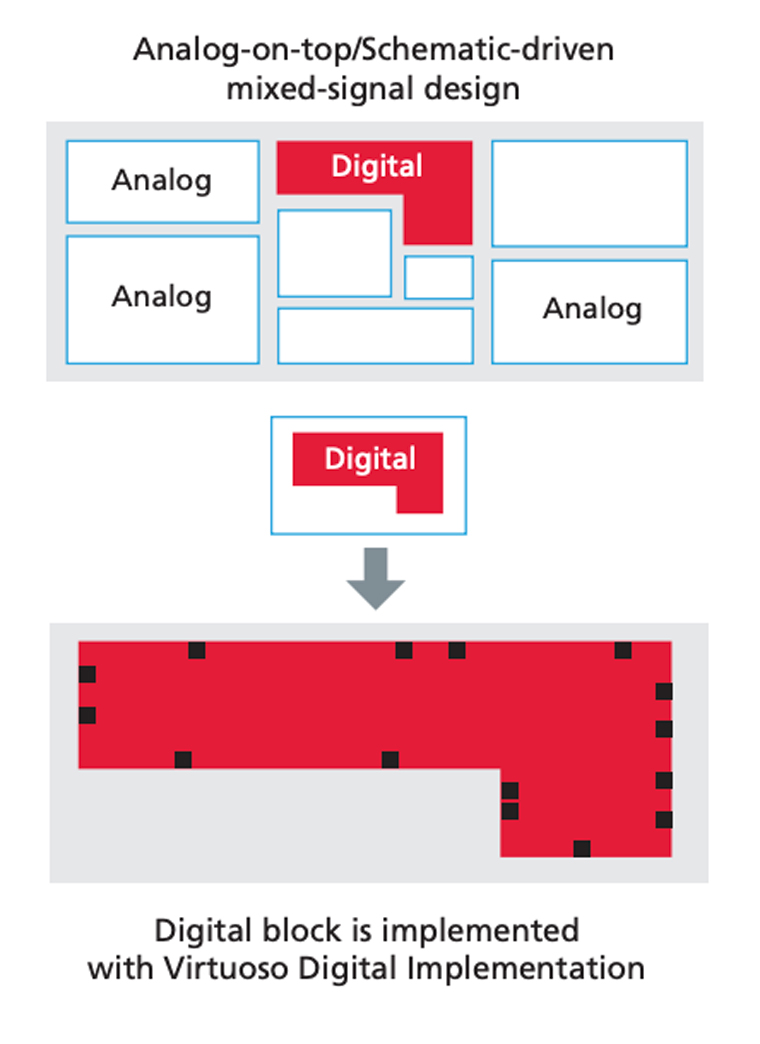

Cadence Virtuoso Digital Implementation 是一个完整的自动化系统,用于 RTL-to-GDSII 模块实现。该系统基于 Encounter RTL Compiler 和 Encounter Digital Implementation System 核心技术,在综合、实现和优化方面具有极佳的性能和准确性,可在先进的模拟驱动混合信号设计中实现一定容量的时序驱动的模块物理实现,包括门级综合和测试驱动设计,以及版图规划、布局、布线和优化。

Overview

针对所有目标快速实现设计收敛

Virtuoso Digital Implementation 是 Cadence 基于 OpenAccess 通用数据库的可互操作混合信号方法的一部分,它可自动确保按照时序、功耗、信号完整性(SI)和物理规范,以正确一致的方式实现数字模块,跨越数字和模拟边界,并始终跨越多个功率域。借助这种实现方式,客户能够针对复杂混合信号设计的所有目标快速完成设计收敛。