The Cadence® Pegasus™ Critical Area Analyzer provides the next generation of critical area analysis (CAA) for even the most advanced nodes, including FinFET technologies, and based on an innovative adaptive sampling method to reduce runtime while maintaining accuracy. The failure models are set up based on learnings from Cadence foundry partners. This adaptive sampling automatically tunes the sampling and numerical methods that are applied to each failure model, which can vary significantly from model to model and technology to technology. Additionally, the process uses our efficient and scalable shape engine, dramatically increasing performance from the previous generation of the tool.

Systematic defects have drawn a lot of focus from the semiconductor industry, especially in the technology development and early technology ramp. However, random defects are still dominant when the technology is mature and in high-volume manufacturing. Historically, foundries have run CAA on incoming designs in order to identify yield-limiting failure modes and estimate yield loss.

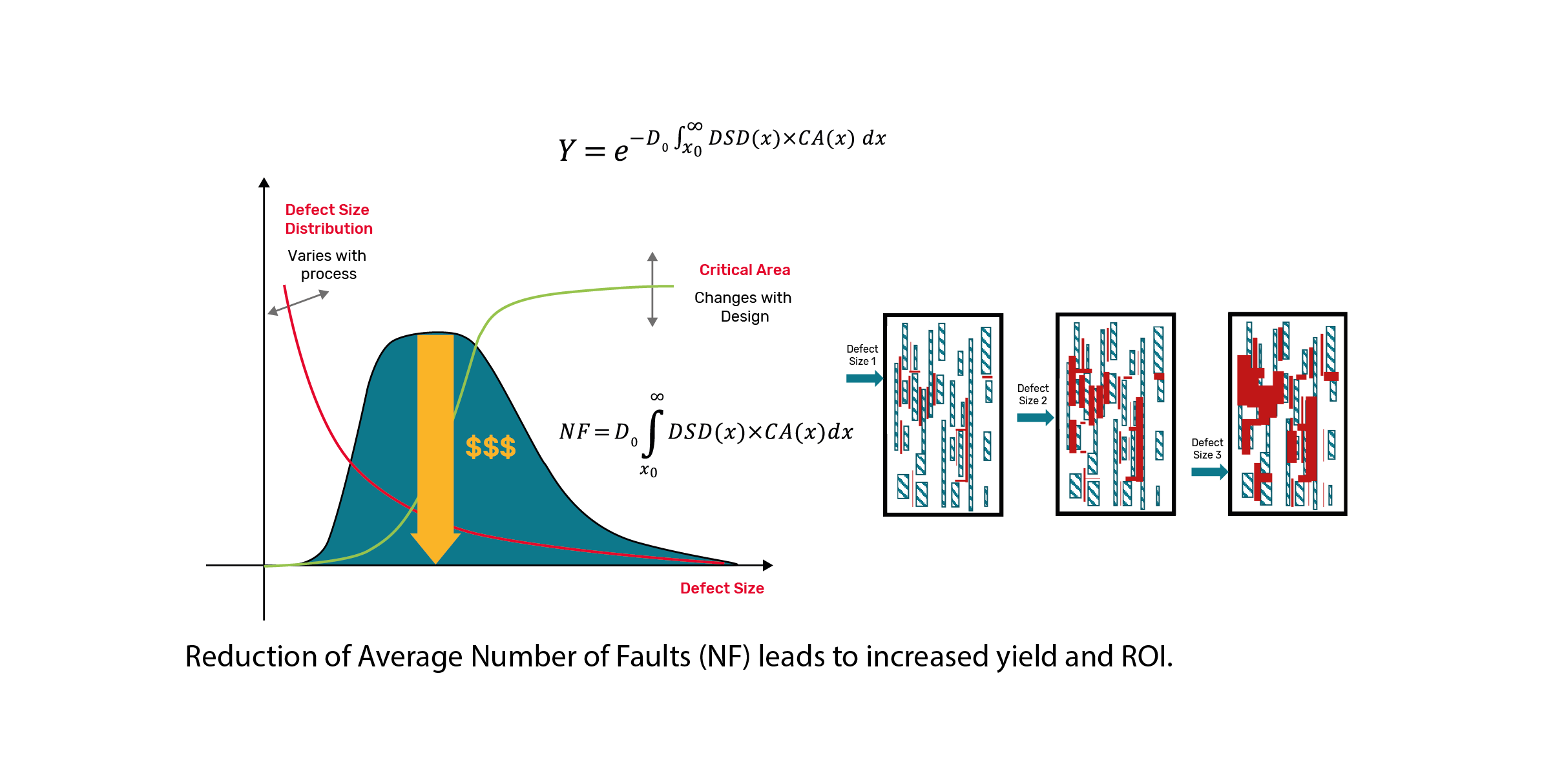

CAA, which has been used for yield modeling since its inception in the 1980s, is a function of the defect size and is the region where the center of a certain-size defect falls into to cause a functional failure in ICs. In recent years, CAA has also been used to identify areas that are sensitive to defects in the layout, as a guideline to optimize the layout, and to make IC products more manufacturing friendly.

However, with growing design complexity in advanced technology nodes, the runtime for critical area computation has increased from hours to days and even weeks. Additionally, FinFET nodes bring their own challenges and failure modes such as transistor-related defectivity and interlayer interactions. Pegasus CAA addresses these challenges with FinFET failure models, critical area extraction efficiency improvements, and methodologies and applications.

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums