Overview

Bridging the Gap Between Custom Design Implementation and Physical Verification

Today's complex SoC designs significantly increase layout creation and verification time, especially at advanced nodes. To meet overall demand for faster design cycle turnaround time, bridge a demand gap, and improve productivity between custom implementation and physical verification tools, Cadence iPegasus Verification System (formerly Virtuoso InDesign DRC*), part of the overall physical verification portfolio, delivers instant signoff quality design rule checks (DRC) to achieve higher quality layout from the Virtuoso Layout Suite.

iPegasus Verification System, in conjunction with foundry-certified signoff rule decks with the Virtuoso Layout Suite, runs Cadence’s Pegasus Verification System in an instantaneous interactive mode. The iPegasus Verification System is a cloud-ready physical verification signoff solution that enables engineers to deliver advanced-node integrated circuits (ICs) to market faster.

Key Benefits

Boost Productivity and Time to Market Using Virtuoso Layout Suite with iPegasus Verification System

Productivity and Performance Boost

Instant in-design DRC physical verification checks deliver up to 50% productivity improvement with integrated in-memory computing using a shift-left approach

Easy to Use

Unified Virtuoso GUI and toolbar for quick access to run the Pegasus Verification System using configurable checks on the complete design as well as a localized/specified area

Expanded Verification

Extensive capabilities include Microsoft Windows-based DRC, density and connectivity checks, as well as signoff fill

Foundry-Certified Rule Decks

Higher quality layout from the Virtuoso Layout Suite with all-inclusive foundry-certified Pegasus Verification System or Physical Verification System (PVS) decks across nodes

Features

Maximize Efficiency and Minimize Errors During Signoff with Key Features in the iPegasus Verification System

Features and Capabilities

Pegasus Integration Delivers Signoff Quality with Foundry-Certified Decks

iPegasus DRC

The creation and verification of complex SoCs, particularly at advanced nodes, can be a time-consuming process. iPegasus DRC for Virtuoso Studio improves productivity and delivers instant signoff quality DRC to achieve a higher quality layout to meet overall demand for faster design cycle turnaround time. iPegasus DRC, combined with foundry-certified rule decks, runs the Cadence Pegasus Verification System in an instantaneous interactive real-time mode (iPegasus). It helps to boost productivity and layout quality with in-design signoff physical verification checks.

iPegasus DRC is an in-design DRC tool that can be invoked during layout creation or modification. It uses a signoff DRC rule deck and runs DRC directly on the layout without data translation. iPegasus DRC is an on-demand DRC that allows running design rule checks with five modes ranging from the visible area to a whole cellview. In addition to the area-specific checks, it lets you check the edited portion of the layout through the “Changed Area” option. These modes allow you to invoke DRC at any stage of layout editing or fixing. Further, you can continue layout editing while iPegasus DRC is running. It can operate on the “read-only” cellview, which is very useful when the layout is managed in a version-control environment. iPegasus DRC excludes the run-time overhead introduced by data translation and rules compilation. So, for small blocks or device-level designs, iPegasus DRC is more attractive than its signoff counterpart.

Key features of iPegasus DRC for Virtuoso Studio include:

- Higher performance

- Capability to run DRC on the complete layout as well as specified areas

- Run-time improvement leveraging snapshots for design rule capturing

- One-click access to run the DRC

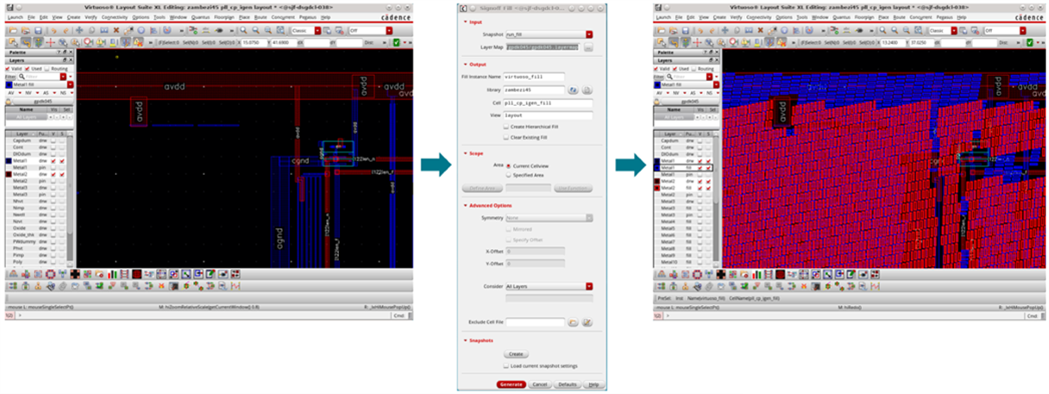

iPegasus FILL

iPegasus Fill for Virtuoso Studio is getting more attention with the adoption of advanced nodes because, at advanced nodes, metal fill can contribute to significant differences in parasitics, making it important to capture the impact of metal fill during the implementation stages for a better and faster convergence in the final design. In-design fill generates signoff quality metal fills and maps them to the OpenAccess design.

The signoff-fill is an interactive tiling feature seamlessly integrated with the OpenAccess database without any dependency on stream in/out. It is very useful for tiling symmetrical analog blocks implemented in a half-cell approach.

*Former Products: The iPegasus Verification System replaces two former products: Virtuoso Integrated Physical Verification System (Virtuoso iPVS) and Virtuoso InDesign DRC

Resources

Browse Recommended Resources

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums