Key Benefits

- 早期に潜在的な反射やクロストークの問題を特定することで、コストや時間を削減

- DCから56GHzまでのシリアルおよびパラレルリンクの統計解析、および、時間領域と周波数領域の解析を備えた最先端のSIインターフェイスをサポート

一般的なトポロジーと標準インターフェイスを迅速に設計できるように、 Cadence® Sigrity™Advanced SIテクノロジーは、以下のような、複数のモードで自動化されたダイからダイのシグナル・インティグリティ(SI)解析を実行します

- パラレル・バスのソースの同期

- SerDesチャネルに重点を置いたシリアル・リンク

- 信号、電源、もしくは、複合what-if解析のためのフリーフォームの汎用トポロジー探索環境

ケイデンスのAdvanced SIテクノロジーは、DCから56GHz(112Gbps)を以上の範囲に対応し、周波数領域の解析手法、時間領域の解析手法、および統計解析手法を使用します

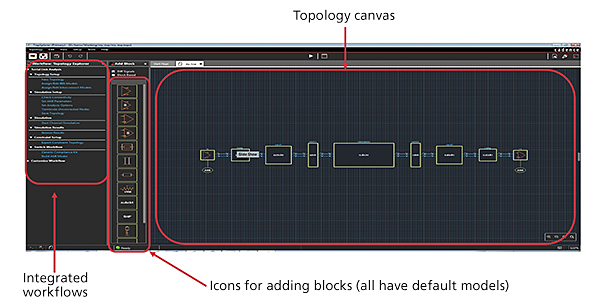

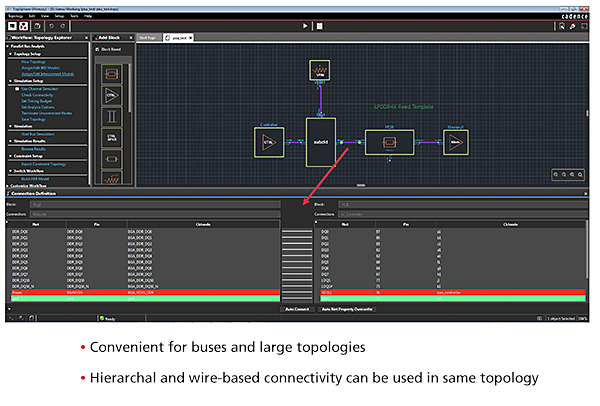

Sigrity Topology Explorer

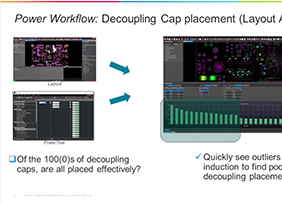

この汎用トポロジー探索機能は、SIやトランジェント・パワー・インティグリティ(PI)解析を同時に実行できるようにすることなど、エンドツーエンドの信号や電源トポロジーの探索に適した機能ですまた、複雑なインターコネクト・モデルを含め、回路を自動的に再現する単体のドライバー/レシーバー/ディスクリート・シンボルにインターコネクト・モデルの各ポートの接続も可能です。この機能はSigrity Auroraに含まれ、物理的なPCBやICパッケージ・デザインから自動的にネットを抽出することができます。

Sigrity SystemSI Parallel Bus Analysis

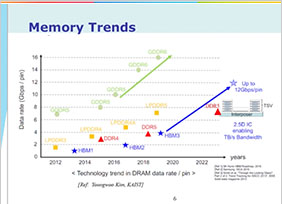

このエンドツーエンド解析はDDRxメモリーを使用したデザインなどソース同期パラレル・インターフェイスを対象としています。プリ・レイアウトの機能(ビア・ウィザードを含む)により、迅速に生成され接続されたモデルから始めることができます設計がより詳細になった時は、詳細モデルに入れ替えて、実際のハードウェアのデザインの影響を反映させます。Advanced SIには、以下の機能が備わっています

- 反射やクロストーク解析のためのインターコネクト・モデルの作成

- Sパラメータを使用せずに精度のあるSSN(simultaneous switching noise、同時スィッチング・ノイズ)解析をサポートする有限差分時間領域ダイレクト(FDTD-direct)を用いてSSN解析を実行(Cadence Extraction Suitesなどに含まれているツールを使用して、Sパラメータのインポートが可能)

- Advanced SIテクノロジーの一部であるCadence Sigrity Broadband SPICE®ユーティリティを用いたSパラメータからSPICEモデルの生成機能

- Read とWrite の両方の送信にイコライゼーション効果を追加します。IBIS-AMIモデルを追加し、100万ビットのシミュレーションにチャネル・シミュレーションを適用して、ビット・エラー・レート(BER)シミュレーションを実現

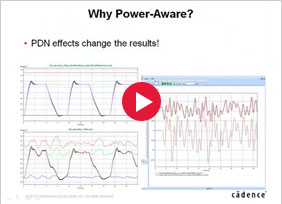

コンカレント・シミュレーションでは、誘電損失および導体損失、反射、シンボル間干渉 (inter-symbol interference 、ISI)クロストーク、SSNの影響を考慮しています。これらのシミュレーションから、非理想的な電源供給システムの影響を完全に説明することができます。グラフィカルな出力とポスト・プロセッシングのオプションから、迅速にシステムを改善するための洞察が得られます。

シミュレーション結果を、DDR4やDDR5などのJEDEC標準要件と比較することで、デザインが標準準拠要件を満たしているか確認することができます。必要があれば、追加のテストを構成して、コンプライアンス・テストを増強したり、独自のIP向けのカスタム・コンプライアンス・キットを作成したりすることが可能です。

Sigrity SystemSI Serial Link Analysis

PCI Express® (PCIe®)、HDMI、SFP+、Xaui、Infiniband、SAS、SATA、USBなどのハイスピードSerDesデザインに焦点を当てた、受賞歴のあるチップ間解析では基本的なテンプレートを使用して早期に評価を行うことが可能です。業界標準のIBIS-AMIトランスミッタとレシーバー・モデルをサポートしているため、複数のサプライヤからのチップを使用したシリアル・リンクのチャネル動作のシミュレーションが可能です。チップ・モデルの開発者の場合、IBIS-AMIモデル開発を支援するテクノロジーを使用することができます。複数のパッケージ、コネクター、ボードのモデルを追加し、チャネル全体を反映させることができます。シミュレーションでは、クロストークの問題を特定し、チップ・レベルのクロック・データ・リカバリー (CDR)テクノロジーの有効性を確認することができます。数百万ビットのデータを含むフル・チャネル・シミュレーションにより全体のBERを確認し、ジッタやのノイズ・レベルが指定の許容範囲内に収まるかどうかを確認することができます。PCIe 5.0など一般的なインターフェイスのコンプライアンス・キットを入手することで、必要な信号品質チェックを自動化することが可能です。所望の規格で利用できない場合、カスタムなコンプライアンス・キットを構成することも可能です。

Features

- 非理想的な電源供給システムのSIへの影響の高精度な処理

- 損失、反射、クロストーク、同時スイッチング出力 (SSO)などのSIの影響の同時評価

- 業界標準のIBIS-AMIトランスミッタ―/レシーバー・モデルのサポートにより、複数サプライヤのチップを用いたシリアル・リンクのチャネル動作のシミュレーション

- 高度に自動化された測定とレポート作成機能

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.