As SoC design complexity continues to increase, verification of the fully assembled chip with all its IP components, buses, and interfaces has become the critical path to tape out. Chip-level testbench creation, bus traffic generation, bus performance bottleneck identification, and data and cache coherency verification all lack automation. The effort required to complete these tasks is error prone and time consuming. Missed performance bottlenecks can expose architectural-level oversights late in the project and covering all corner cases for cache coherency across multiple parallel compute engines can take months.

Cadence® System-Level Verification IP (System VIP) takes Cadence’s market leadership in IP-level verification automation and brings it to the chip level. It consists of a suite of tools and libraries, each working seamlessly with Cadence’s simulation, emulation, and prototyping engines.

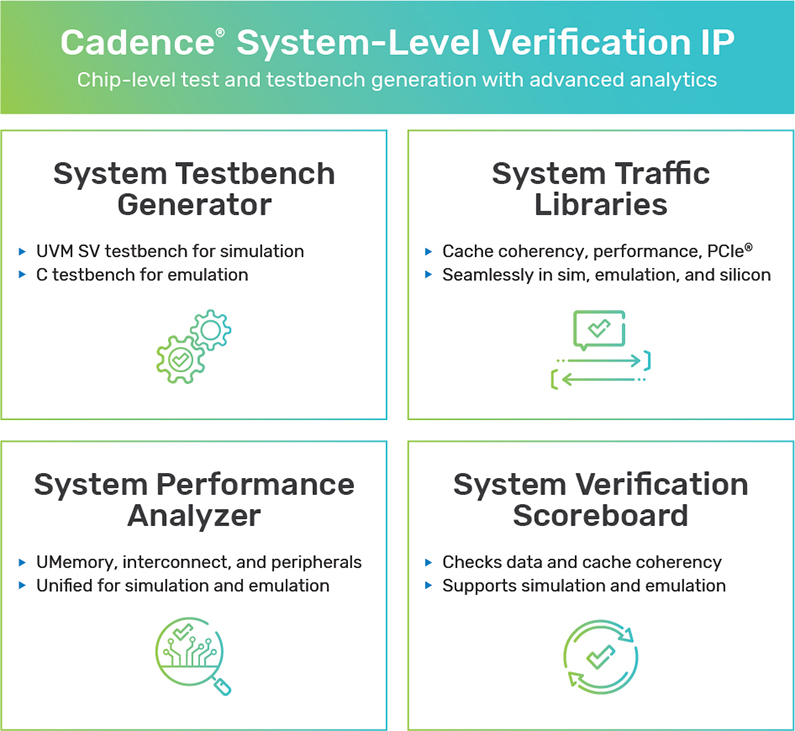

Cadence System VIP includes:

- System Testbench Generator allows users to describe their testbench topology through IP-XACT or CSV and automatically generate a ready-to-use UVM SystemVerilog testbench for simulation or C testbench for emulation.

- System Traffic Library provides users with rich portable stimulus tests for common SoC domains including coherency, performance, PCIe, and NVMe subsystems, which run seamlessly in simulation, emulation, and final silicon. These libraries are integrated with Cadence VIP and Accelerated VIP (AVIP) for fast bring-up.

- System Performance Analyzer offers comprehensive performance analysis for memory subsystems, bus interconnects, and peripherals.

- System Verification Scoreboard provides data and cache-coherency checkers, which allow users to check data consistency across the system, supporting both simulation and emulation flows. The automated scoreboard supports coherent interconnects, memories, and peripherals, and is integrated with Cadence VIP and AVIP.

Cadence System VIPを使用することにより、オートモーティブ、モバイル、コンシューマー向け超大規模チップを開発するお客様はチップレベルの検証を自動化することが可能となり、検証効率を従来比で最大で10倍向上できます。