Datasheet

Sigrity SPEED2000

Layout-based, time-domain signal integrity/power integrity/electromagnetic interference simulations

Cadence Sigrity SPEED2000 technology provides for direct layout-based, time-domain simulations of an entire board design or for a specific IC package together with the PCB. These simulations can include various SPICE/S-parameter interconnect models and component models commonly used in signal integrity (SI)/power integrity (PI) simulations. The Sigrity SPEED2000 engine combines circuit solver and transmission line solver with a fast electromagnetic (EM) field solver to capture dynamic interactions between signal, power, and ground on signals and planes in one time-domain simulation. Using the tool, you can perform a broad range of workflows for various levels of SI and PI analysis as well as electromagnetic interference (EMI) and electro-static discharge (ESD) studies in a single environment.

Overview

Sigrity SPEED2000 ERC

Electrical rule checking (ERC) is a fast and easy way to scan a full board for first-order electrical design problems without the requirement for IBIS models. These checks fill in the gap between a geometry-based design rules check (DRC) and a simulationbased signoff simulation task performed with IBIS models.

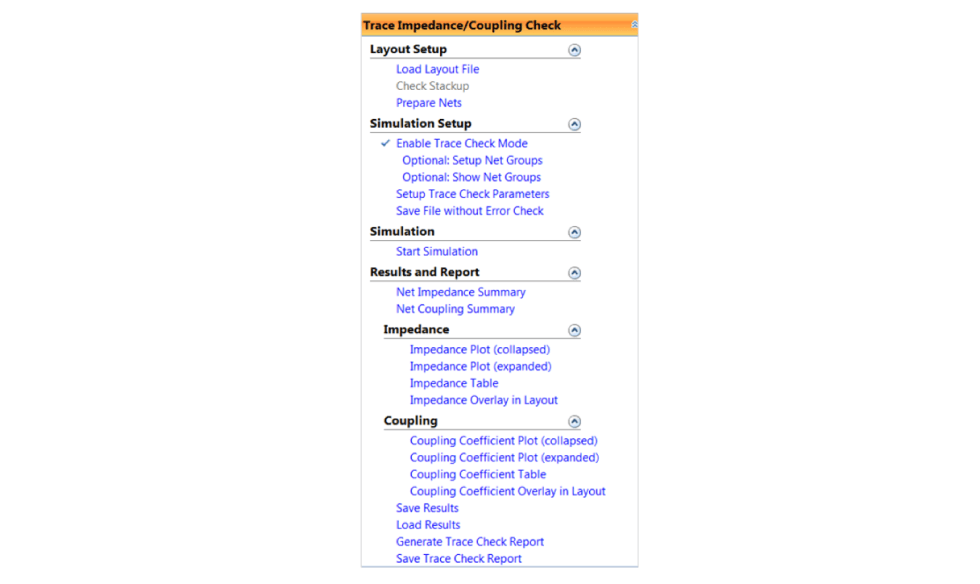

Basic ERC

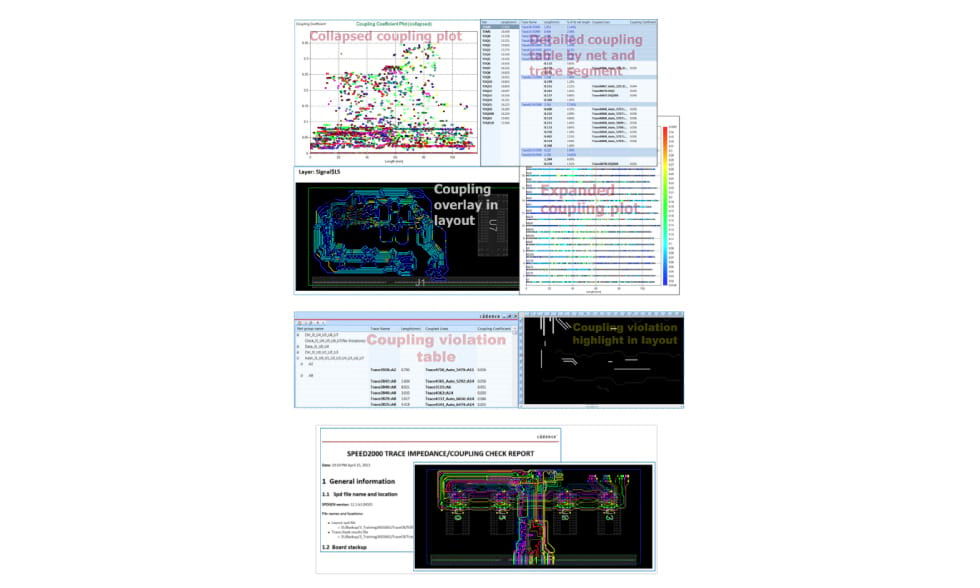

Trace impedance, coupling, and return path discontinuity checks provide a micro view of layout trace properties, which are useful for design and debug. Using this technology, you can quickly screen the board layout to get:

Trace check results are bundled by net groups, making the comparison easy and meaningful. Set up of net groups is easy and automated. Based on the trace check results, you can easily see the impedance/ coupling distribution to identify the violations in the plots, and use cross-probing to locate the violations in the layout. Reports are available in HTML.

Simulation-based ERC

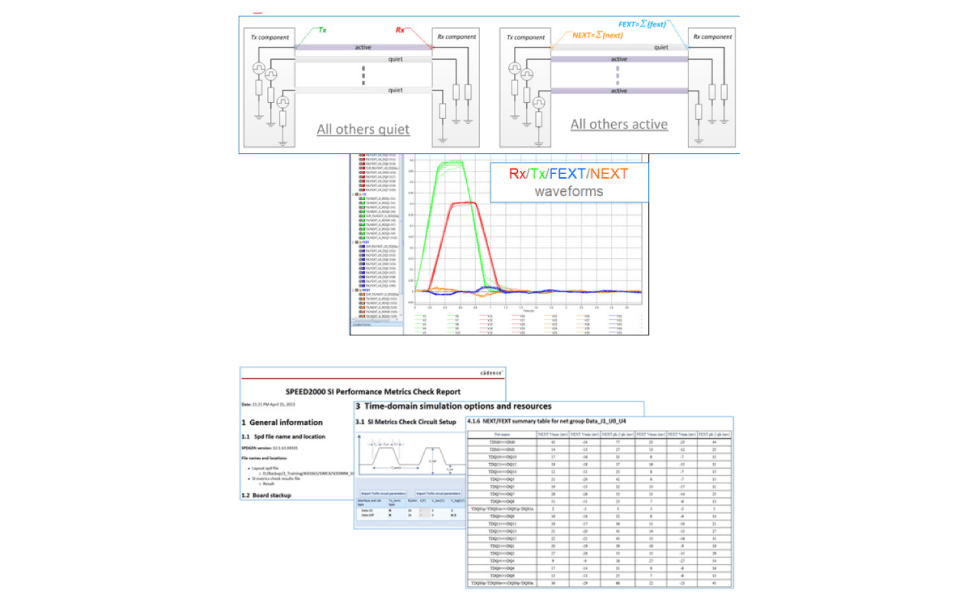

Simulation-based rule checking provides a more detailed view of overall SI performance, which is useful for additional screening and design reviews before moving on to detailed power-aware SI analysis for signoff. Simulation-based electrical rule checks rely on time-domain simulations that consider crosstalk and non-ideal power and ground supplies, without having to assign IBIS models. Save time when checking on a large number of nets with an easy-to-use workflow combined with a high level of automation and parallel computing. Generated results include:

Simulation-based electrical rule checks can be used in the following cases:

Power-aware ERC

When run with a non-ideal PDN, simulation-based rule checking can be expanded to simulate the impact of power noise and the coupling to signals. These expanded checks include:

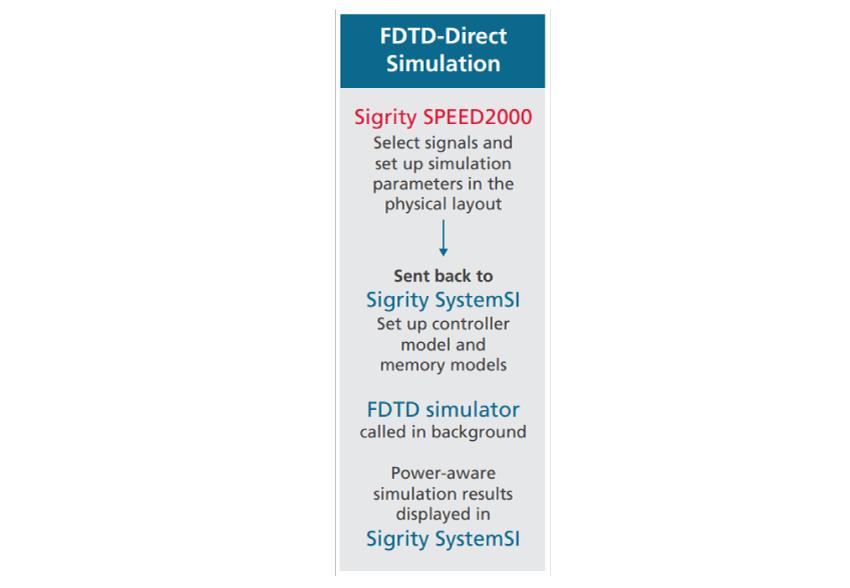

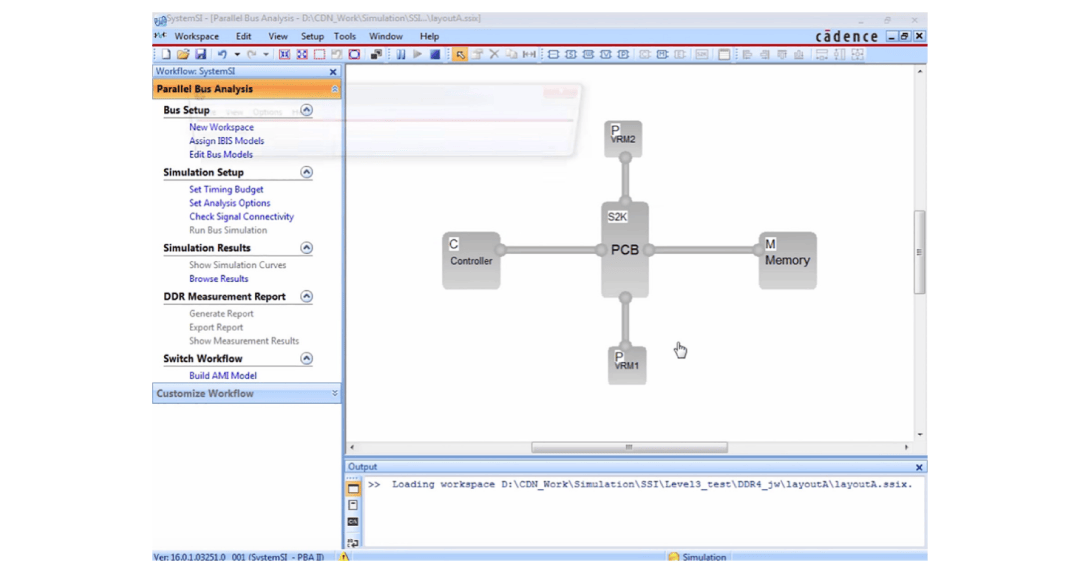

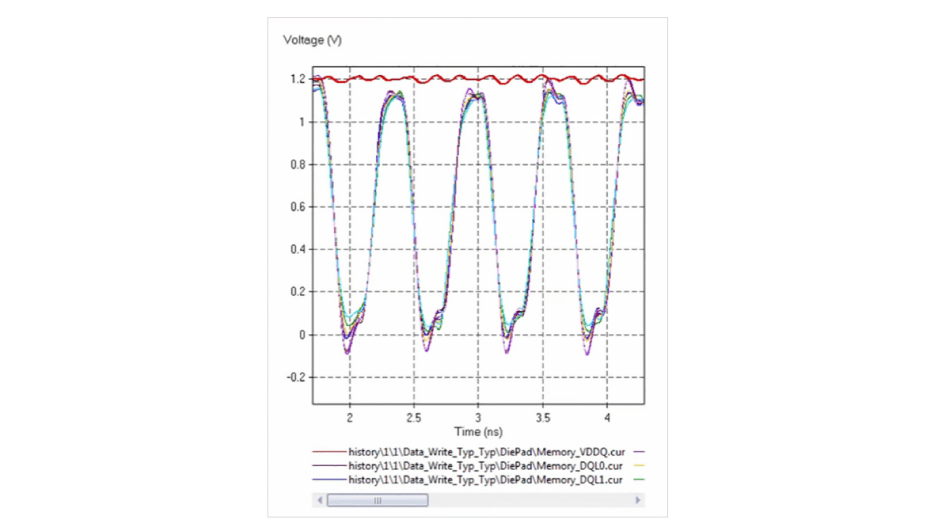

DDR Simulation with Sigrity SPEED2000 and SystemSI Tools

Due to complexities in setting up DDR simulations as well as interpreting the post-simulation results, Cadence recommends driving DDR simulations from the Sigrity SystemSI tool. The Sigrity SPEED2000 tool plays an important role in moving from initial reflection simulations to signoff-level power-aware simulations that include the impact of simultaneous switching noise. Initial simulations can be driven from the Sigrity SystemSI tool using extracted SPICE models created by Sigrity SPEED2000 workflows. For final signoff, the same user interface in the Sigrity SystemSI tool can be used to drive the Sigrity SPEED2000 FDTD-direct workflow where the interactions between signal, power, and ground are all included.

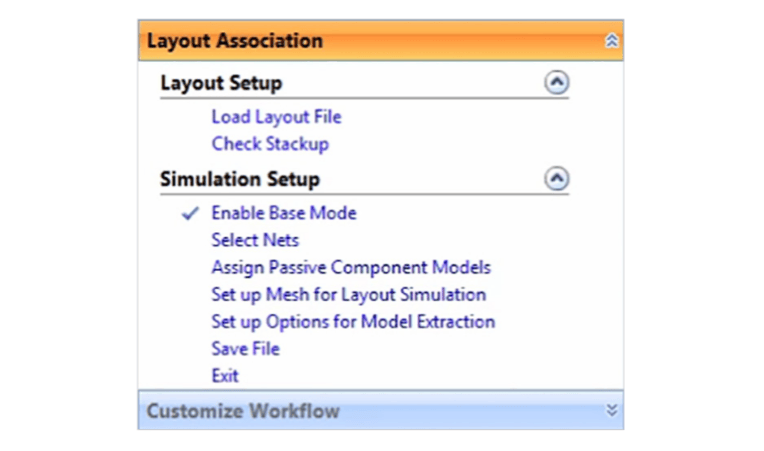

An important advantage of using the combination of Sigrity SPEED2000 and SystemSI technologies is that you do not need to generate S-parameter models for interconnect models, so you can avoid typical non-passive and non-causal problems when S-parameters are used in SPICE time-domain simulation. Those problems are typically more pronounced when a large number of DDR signals is included in the simulation, along with DDR power and ground nets and large number of decaps. Using the Layout Association (FDTD-direct) workflow, you can run what-if DDR simulations to see the impact of non-ideal power/ground on the memory interface design.

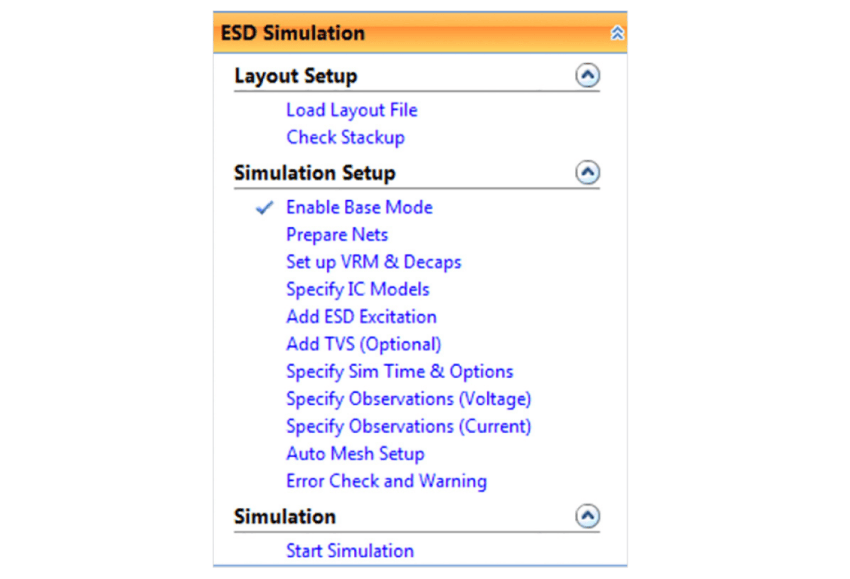

ESD Workflow

The electro-static discharge (ESD) workflow is used to test the impact of sudden and unexpected flow of electricity from an external source such as human contact or plugging in a cable with a charge. The flow includes defining the placement of an ESD gun model and then observing the impact to the board, signals, and planes. Transient-voltagesuppression (TVS) diodes and their ability to clamp the voltage peak are included in the ESD simulation.

Using the Sigrity SPEED2000 Engine as a General-Purpose SI/PI Tool

The Sigrity SPEED2000 engine offers other workflows and features that make it useful as a general-purpose SI/PI tool:

Fast Simulation Setups with Workflows

Support for a Variety of Layout Data Types

The Sigrity SPEED2000 tool performs time-domain simulation directly on physical design data. You can easily use layout data from Cadence SiP Digital Layout, Cadence Allegro Package Designer, and Cadence Allegro PCB Designer. Then, you simply attach circuit models directly to components in the layout. This way, vias, signal traces, power/gnd planes, and passive and IC component circuits are all included in simulations, providing you with comprehensive and accurate SI/PI performance results. All other major types of layout databases, such as those from Zuken and Mentor Graphics, can be translated into the Sigrity SPEED2000 tool.