- Introduction

- Analog, Digital, and Mixed-Signal Simulation

- Modeling Languages, Tools, and Techniques

- RNMs

- EEnet and Table Models

- RNMs in the Context of UVM, SVA, and UPF

- RNMs in the Context of MDV and MS-MDV

- DMS and AMS with Xcelium Logic Simulator

- Example Applications and Vertical Markets

- Conclusion

White Paper

Demystifying Mixed-Signal Simulation for Digital Verification Engineers

The convergence of analog and digital technologies on a single chip, commonly referred to as mixed-signal, has reshaped the integrated circuit (IC) landscape. In recent years, mixed-signal designs have emerged as the dominant technology, therefore requiring traditional analog and digital methodologies to be enhanced. A mixed-signal design offers many advantages, including boosted performance, reduced power consumption, and increased reliability. As the tech industry continues to push the limits of what is possible, the need for mixed-signal simulation makes thorough verification essential.

Cadence’s Xcelium Logic Simulator offers significant advances in mixed-signal verification, streamlining the future of chip design. Xcelium verification tasks are typically carried out by digital engineering teams. This paper introduces an innovative approach to enable digital engineers to efficiently model and simulate analog and mixed-signal components within the digital domain. Doing so simplifies the integration of mixed-signal elements into the broader digital framework, thereby reducing development costs and streamlining the entire process.

Overview

Introduction

As analog and digital components become increasingly intertwined, particularly in control loops and datapaths, the need for integration and effective verification is becoming a requirement. This integration demands a precise verification process that balances performance, accuracy, and comprehensive metric-driven validation.

In the IC design process, disparate simulators with limited advanced verification features frequently operate independently and may not adhere to universal verification methodology (UVM) standards. These independent tools are implemented by separate teams of analog and digital engineers to individually verify the functionality of analog and digital blocks. At some stage, it is necessary to verify the device in its entirety, sometimes in the context of a full system, to ensure that the chip’s analog and digital functions work together as intended. It is possible to couple the analog and digital simulators to provide a solution known as analog mixed-signal (AMS), but this has previously been left to a specialized team towards the end of the development process.

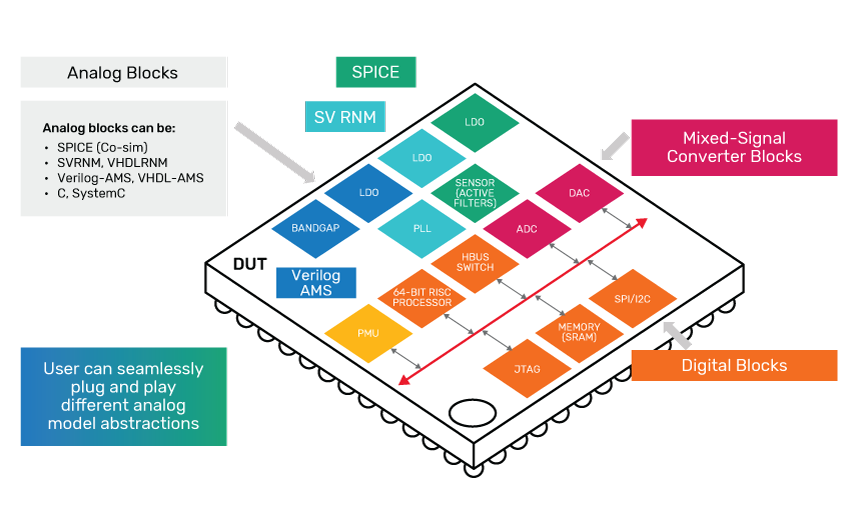

Even predominantly digital chips invariably incorporate analog elements like on-chip sensors for process, voltage, and temperature. These sensors provide data to digital control functions. Integrating mixed-signal features such as touch screens, haptic actuators, PHYs for connecting to external systems, and memory interfaces further blur the line between digital and analog functions. The result is that today's complex ICs incorporate a blend of analog, digital, and mixed-signal elements, each playing a vital role in the device's operation.

The consequences of not performing full device-level mixed-signal simulation may involve re-spinning the device, which is both expensive and time-consuming. The problem is that digital verification (DV) engineers are rarely experienced when it comes to creating analog models, running analog simulators, and understanding and debugging the results from analog simulation runs. The solution is to use a digital mixed-signal (DMS) approach. While maintaining a reasonably high level of accuracy, a DMS simulation runs orders of magnitude faster than its AMS counterpart. DMS simulation allows DV engineers to create models of the analog functions in a form they understand and to subsequently perform many aspects of the mixed-signal simulation in the digital domain using their existing digital environment with which they are familiar.

The Xcelium Logic Simulator can support integrated DMS simulation and co-simulation with the Cadence Spectre Simulation Platform, a SPICE analog simulator for full AMS verification. This methodology’s scalability of verification is a key feature, ensuring the seamless incorporation of advanced analog (SPICE/Verilog AMS) models into high-accuracy simulations with minimal overhead down the road.

Analog, Digital, and Mixed-Signal Simulation

An analog simulator works with circuits at the level of transistors, resistors, capacitors, and inductors, with the circuit represented as a matrix of differential equations. The simulator simultaneously solves the equations while trying to find a solution for a given stimulus.

The advantage of analog simulation is that it offers the highest level of accuracy and most closely achieves fidelity of verification. However, there are several disadvantages associated with this approach. These include the complexity and expertise required to create models of the components. Analog design knowledge is required to run the simulation and debug the results. Furthermore, the analog simulator tends to have a relatively limited performance compared to its digital counterpart. Additional concerns include the lack of functional coverage capabilities provided by digital domain tools and the inability to employ the full suite of digital verification techniques.

The most common forms of digital logic simulation are event-driven, in which the simulator sees the world as a series of discrete events, and cycle-based, in which the steady-state value of the circuit is computed for each cycle of the clock. Although this is something of a simplification, a digital simulator primarily works with only four logic values: 0, 1, X (unknown), and Z (high impedance). In the case of event-driven simulators, when an input to a digital function experiences a change in value, the simulator evaluates that function to determine whether it will result in a change at the output and, if so, schedules an event for some time in the future.

The advantages of digital simulation include extremely high performance compared to analog simulation. Also, digital simulators support a full verification flow, offering repeatability and predictability. The simulators work well with tools that automatically generate verification stimuli, evaluate coverage results, and perform regression tests. It is unfair to say that digital simulators are less accurate than analog simulators because they are extremely accurate in their own domain. By default, they may not model and simulate analog effects but are more than sufficient for functional verification for the digital portion of the design.

To ensure seamless operation across all domains, it may be necessary to verify the entire device, ensuring that both the analog and digital functions work together as planned. The integration of analog and digital simulators to establish an AMS solution is usually deferred to a dedicated specialist team toward the conclusion of the development process. The challenge is that DV engineers also need to perform extensive simulation runs and regressions. However, in addition to the analog simulator’s inherently heavy computation requirements, an AMS implementation involves time-consuming inter-process communication.

Due to the preponderance of digital functionality within the IC, the bulk of full device-level verification falls on the shoulders of the DV engineers, who give little thought to analog. As a workaround, many engineers address this issue by creating simple “stub models” to represent analog components. However, all these models do is monitor or generate 0 and 1 values without any real understanding of what is occurring in the analog domain . As a result, customers report that many design failures and silicon respins are caused by preventable errors, including pin connections, inverted polarities, incorrect bus order, or pins connected to the wrong power domains. Without simple checks, such errors are often found only in lengthy AMS simulation runs.

Digital verification engineers need a DMS solution that can effortlessly create analog function models in a familiar format and conduct the entire mixed-signal simulation within their existing digital environment. In addition to a DMS simulation running orders of magnitude faster than its AMS counterpart, the DMS approach allows DV engineers to take full advantage of their existing environment and tools to verify and debug the interaction of the mixed-signal portions of the design.

Modeling Languages, Tools, and Techniques

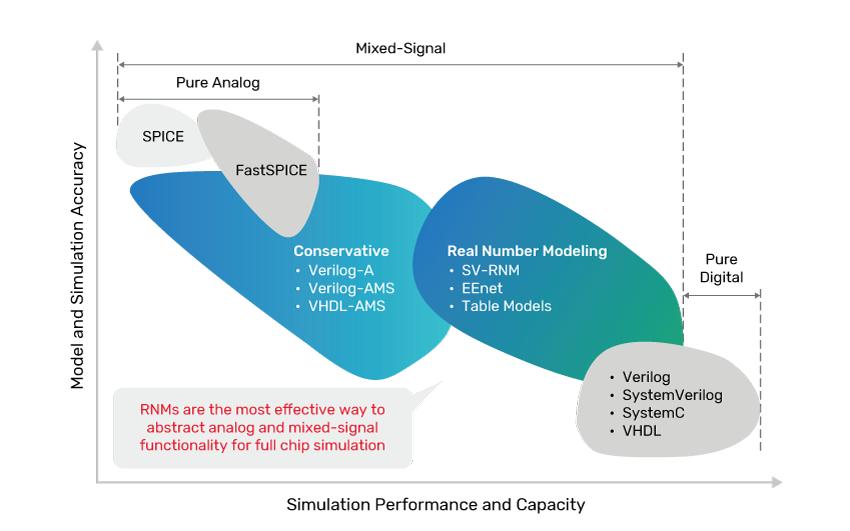

Pure analog simulation relies on SPICE or Spectre FX FastSPICE simulators, primarily utilizing the SPICE Netlist hardware description language (HDL). SPICE excels in transistor-level analog intellectual property (IP) verification due to its high accuracy. Still, it's impractical for full-chip simulations, as it constructs a single large matrix for solving current and voltage values over time. In contrast, FastSPICE, while using the transistor-level netlist, partitions it into smaller segments, each with its small matrix, allowing for faster computation by solving multiple smaller matrices instead of one large matrix.

Models used for pure digital simulation are captured using HDLs like Verilog, SystemVerilog, SystemC, and VHDL, where SystemVerilog is a superset of Verilog. Many digital simulators can accept multiple HDLs. Furthermore, since an IC design may include IPs from multiple vendors, each of whom may favor a different HDL, digital simulators typically support designs using a mixture of HDLs.

One of the early steps toward the ability to support mixed-signal simulation was the creation of language extensions to traditional digital HDLs in the form of Verilog and VHDL. These language extensions, Verilog-AMS (which subsumed the earlier Verilog-A) and VHDL-AMS, can be used to create behavioral models of the analog portions of the design. These models may be called “conservative” because the systems they model conserve charge and energy.

One problem with Verilog-AMS and VHDL-AMS is that most DV engineers are unfamiliar with them. Also, they regard them as being difficult to learn and hard to use. Another issue is that these models run under the SPICE or FastSPICE simulators, which means the DV engineers would still need to employ a full AMS simulation environment.

As illustrated in Figure 1, the most effective way for DV engineers to abstract analog and mixed-signal functionality for use in full-chip simulations is to use a technique called real number modeling to create eponymous real number models (RNMs). If created using SystemVerilog, these models may be referred to as SV-RNMs.

In addition to SV-RNMs being captured in a language already known to DV engineers, these models allow the entire full-chip simulation to be performed with the digital simulator, with all the performance and capacity advantages that entails.

RNMs

Real number modeling, also known as wreal (wired-real) modeling, borrows concepts from the analog and digital simulation domains. The most important point for DV engineers is that RNMs are created in a language they already know, SystemVerilog in the case of SV-RNMs.

The easiest way to think about this is as follows: instead of writing digital models that accept, manipulate, and generate only 0s and 1s, RNMs allow DV engineers to write models that involve complex mathematical equations that work with real number values like 3.142 or 16.893. An example of one of the easier RNMs a DV engineer might wish to create would be an analog-to-digital converter (ADC). In this case, the modeler doesn’t need to worry about voltages and currents, just real number inputs and integer outputs.

It’s important to note that RNMs are not restricted to modeling only electrical circuits. Instead, they can model things like user interfaces with haptics and touchscreens to sensors detecting rotation and vibration.

EEnet and Table Models

In some cases, the DV engineers may wish to include an extra level of reality into the simulation with respect to specific analog and mixed-signal functions. However, it may be that these functions are not easily described using equations. Often, it may be preferable to represent these functions in terms of analog circuits.

As DV engineers typically have limited expertise in the analog domain, including the creation of analog models at the component level, the initial solution involves collaborating with analog design engineers. Nevertheless, a new challenge arises as most analog engineers are unfamiliar with the digital domain, including digital HDLs.

To address this situation, Cadence has developed the EEnet, which contains parameterized RNMs that represent resistors, inductors, capacitors, diodes, transistors, and op-amps. Analog engineers can employ their preferred schematic capture tool to swiftly and effortlessly create diagrams using EEnet's associated symbols. The schematic tool can then generate a netlist that references these EEnet based (or developed) model. DV engineers can utilize this netlist of RNMs to represent analog and mixed-signal functions within their DMS simulations when working with the Xcelium Logic Simulator.

Additionally, instead of writing a model for an analog function, such as a sensor, it's possible that either the analog engineers or the DV engineers possess real-world data obtained from testing equipment like oscilloscopes, logic, or spectrum analyzers. In this scenario, when utilizing the Xcelium Logic Simulator, it's possible to use this data to construct a type of RNM known as a table model, with the time-value data structured in a standard CSV format.

RNMs in the Context of UVM, SVA, and UPF

UVM is a standardized, structured methodology for creating testbenches, which includes coding guidelines and is used to develop reusable verification IPs, including agents, monitors, and drivers. A significant advantage of using UVM is code reuse.

SystemVerilog Assertions (SVA) are vital in validating an IP's behavior through Assertion-Based Verification. In addition to the IP's functional definition in HDL, assertions specify the expected IP behavior. These assertions cover signals at the IP's interface as well as signals and registers inside the IP itself. For instance, a simple assertion might state, "Signals A and B should never both be active (low) at the same time." More complex assertions may involve transaction-level conditions, like, "Upon receiving a PCI write command, a memory write command of type xxxx must be issued within 5 to 36 clock cycles." These assertions can be dynamically examined during simulation, providing valuable functional coverage insights when a testbench is applied to a design.

DV engineers are used to employing UVM, SVA, and UPF in their simulations and emulations. Since RNMs, including EEnet and table models, work entirely in the digital domain, DV engineers can continue to leverage all aspects of UVM, SVA, and UPF in their full-chip DMS simulations. This aspect of real number modeling is important since RNMs expand the capabilities of UVM, SVA, and UPF into the mixed-signal world, which may be difficult to achieve in a purely analog simulation.

RNMs in the Context of MDV and MS-MDV

Metric-driven verification (MDV) is a method that automates the verification process by comparing test coverage against predefined goals. This involves defining criteria within an executable verification plan, collecting metrics after running tests, and then integrating these metrics back into the verification plan.

RNMs, which include EEnet and table models, operate exclusively within the digital domain, enabling DV engineers to expand conventional MDV to encompass analog and mixed-signal components modeled with RNMs in DMS simulations. This expanded approach is referred to as mixed-signal MDV (MS-MDV).

Expanding metric-driven verification to include the digital, analog, and mixed-signal functions represented through RNMs results in improved verification predictability. It offers automated data collection and reporting and faster turnaround time from regression to bug triage and design debug, along with clear signoff criteria that ensure consistent quality with traceable metric-based results.

DMS and AMS with Xcelium Logic Simulator

The Xcelium Logic Simulator provides best-in-class core engine performance for SystemVerilog, VHDL, SystemC, e, UVM, UPF, low power, and X-propagation. By providing support for RNMs (including EEnet and Table Models), the Xcelium Logic Simulator offers full integrated support for DMS simulations.

The Xcelium Logic Simulator utilizes domain-specific applications, such as mixed-signal, machine learning-based test compression, and functional safety tools. These applications enable design teams to attain verification closure sooner for both IP and system-on-chip designs.

The Xcelium Mixed-Signal app enables integrated co-simulation with Spectre simuation to provide full AMS simulation capability as required.

Example Applications and Vertical Markets

A growing number of Cadence customers have shifted away from traditional AMS simulations and are instead adopting DMS simulations using RNMs, including Table Models and EEnet. This transition has resulted in substantial productivity gains in speed, performance, and debug capabilities.

Below are a few recent use cases from Cadence customers:

Conclusion

The convergence of analog and digital technologies in mixed-signal designs continues to reshape the chip development landscape. Mixed-signal designs introduce additional complexity to the design process, making thorough verification critical. This paper has introduced a solution aimed at enabling digital engineers to proficiently model and simulate analog and mixed-signal elements within their familiar digital domain, reducing engineering cycle time. Cadence's Xcelium Logic Simulator plays a central role in this solution, offering significant advancements in mixed-signal verification. It streamlines the verification process and leads the path forward for chip design, promising improved performance, power efficiency, reliability, accuracy, and cost-effectiveness.