- Overview

- Tempus DRA Suite Benefits

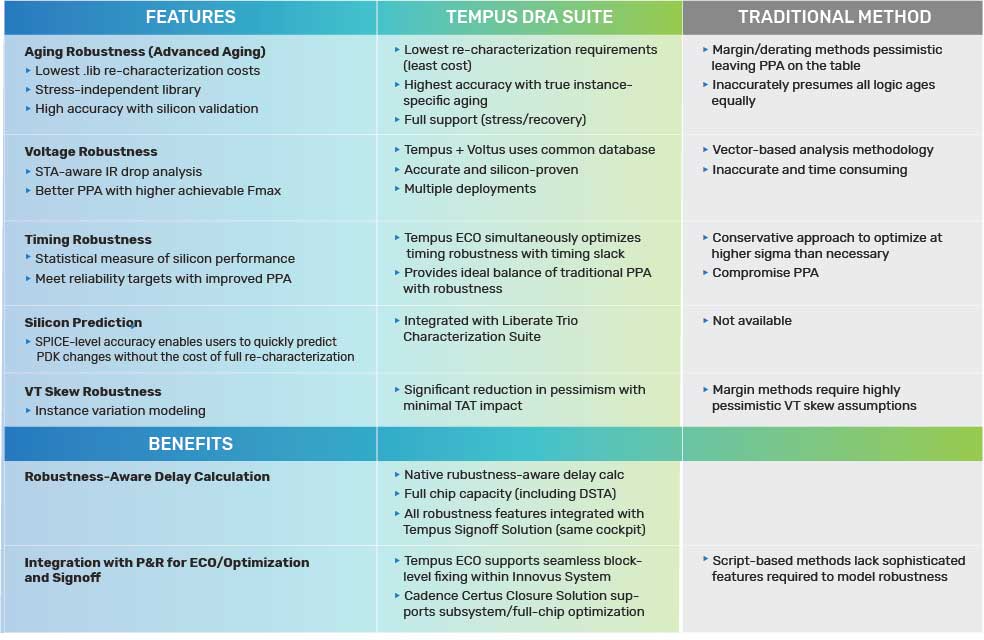

- Aging Robustness – Improve PPA by Up to 10% Through Accurate Aging Analysis

- Voltage Robustness – STA-Aware IR Drop Analysis

- Timing Robustness – Statistical Measurement of Silicon Performance

- Silicon Prediction – Process Drift Modeling and Prediction Plus Model-to-Hardware Correlation

- VT Skew Robustness - Advanced Techniques Addressing Pessimistic STA Methodology

Technical Brief

Achieving Best-in-Class PPA with the Cadence Tempus Design Robustness Analysis Suite

The Cadence Tempus Design Robustness Analysis (DRA) Suite delivers signoff analysis and optimization of specific phenomena such as silicon aging, process variation, and other critical effects impacting design performance. It provides highly accurate models enabling design engineers to sign off with confidence while achieving best-in-class power, performance, and area (PPA).

Overview

Overview

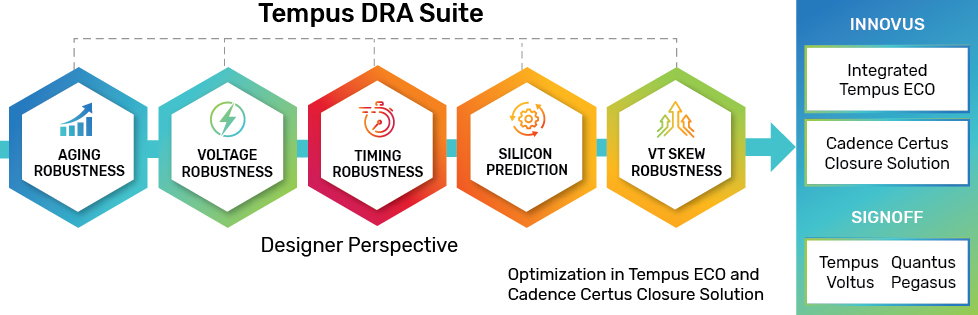

The Tempus DRA Suite comprises five advanced timing analyses: aging robustness, voltage robustness, timing robustness, silicon prediction, and VT skew robustness. The suite’s advanced timing models enable design engineers to accurately analyze these effects with significantly reduced pessimism compared to traditional approaches such as derates or margins. Furthermore, design engineers may use the timing data to drive optimization and signoff closure using the Tempus ECO Option from within the Cadence Innovus Implementation System or using the Cadence Certus Closure Solution. This integrated approach ensures the best PPA and fastest closure from block-level to subsystem-level/full-chip design.

Aging Robustness – Improve PPA by Up to 10% Through Accurate Aging Analysis

Aging robustness, the first industry-leading analysis capability, offers breakthrough technology to accurately address the aging challenges present in automotive, aerospace, consumer, mobile, and hyperscale designs. In lieu of grossly inaccurate margins, aging robustness calculates the exact effect of aging on circuit performance while simultaneously improving design PPA. The analysis begins with the Cadence Liberate Library Characterization Flow capturing an aged stress-independent library model based on foundry-specific SPICE reliability models. Design engineers then measure design performance within the Tempus Timing Solution utilizing non-uniform aging and recovery models. Finally, designers simultaneously optimize aged and fresh PPA within Tempus ECO and the Innovus Implementation System flow. With aging robustness, teams can now deliver faster design closure and better PPA by avoiding the over-design of traditional aging methodologies.

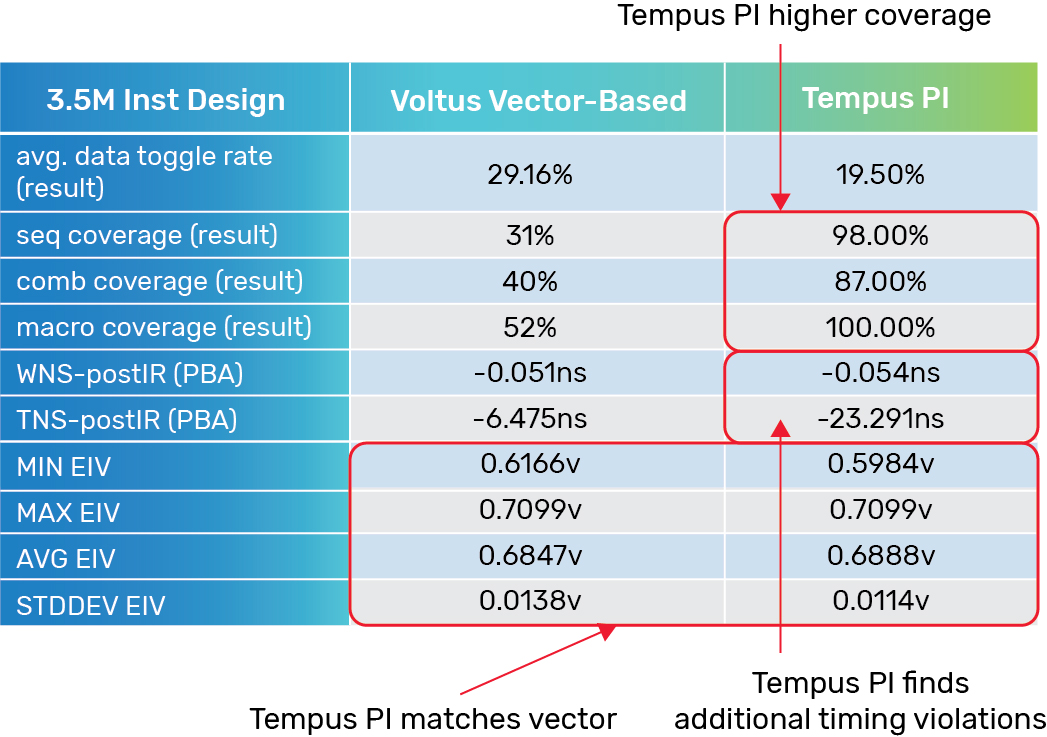

Voltage Robustness – STA-Aware IR Drop Analysis

The voltage robustness analysis capability offers first-of-its-kind integrated IR drop analysis and fixing technology to provide true signoff capability. With seamless integration between Tempus Power Integrity (PI) and Voltus IC Power Integrity solutions, voltage robustness analyzes the impact of IR drop on circuit performance, catching timing violations missed by today’s traditional IR drop signoff methodology that can result in dead silicon. Furthermore, voltage robustness integrates with Tempus ECO to reduce both timing and IR drop violations while achieving the best PPA.

Timing Robustness – Statistical Measurement of Silicon Performance

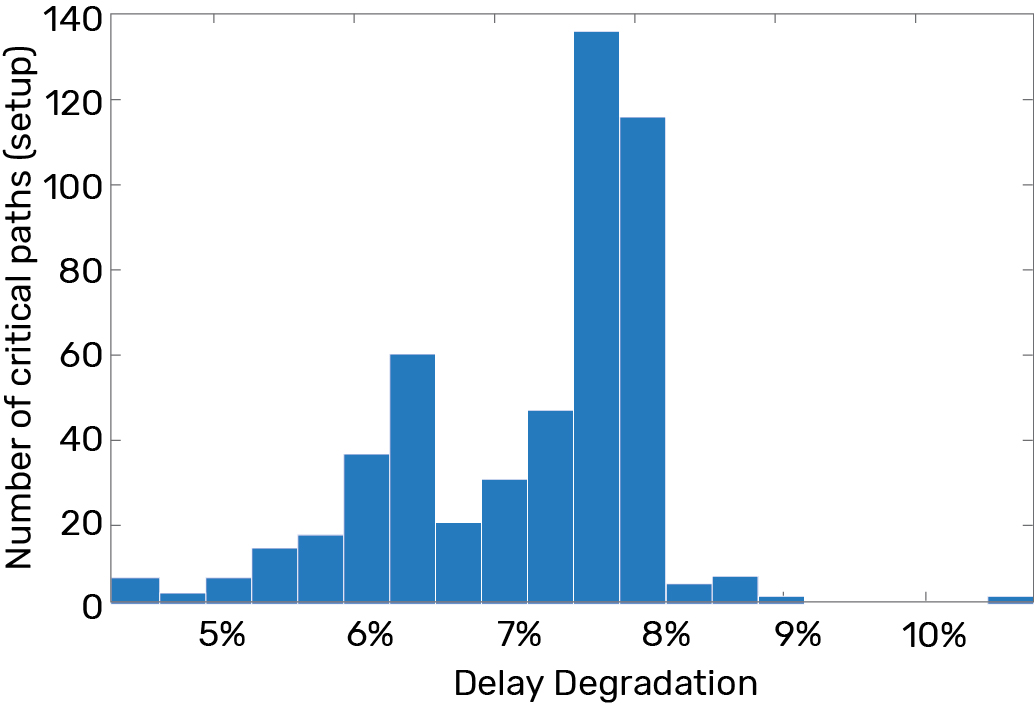

Timing robustness, the third analysis capability in the Tempus DRA Suite, captures correlated delay variation across the design, overcoming the capacity limitations of traditional SPICE Monte Carlo analysis. Design engineers can use timing robustness in conjunction with Tempus ECO to optimize variation while improving PPA and accelerating the timing closure ECO cycle.

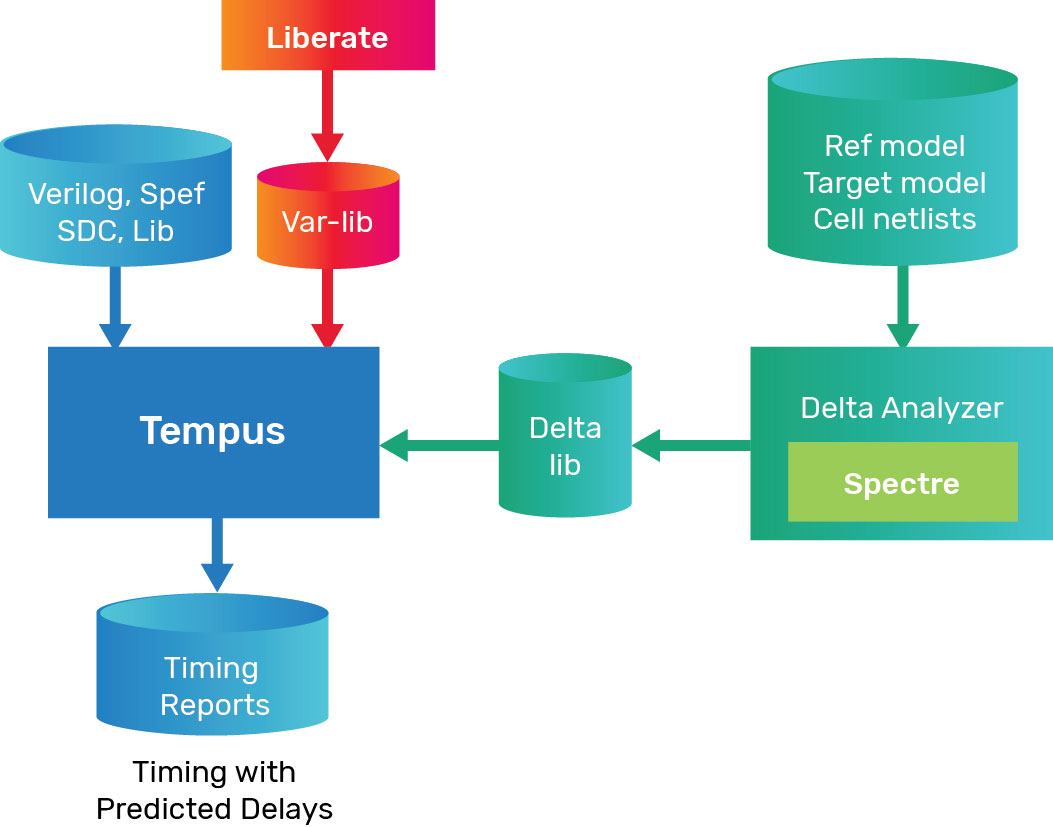

Silicon Prediction – Process Drift Modeling and Prediction Plus Model-to-Hardware Correlation

Silicon prediction is the fourth analysis capability in the Tempus DRA Suite, providing design engineers with a methodology to predictively analyze circuit performance over a series of PDK revisions. Silicon prediction leverages integration between the Liberate Library Characterization Flow and the Tempus Timing Solution to provide accurate statistical models for identified discrete parameters. This allows design engineers to quickly assess the impact of a parameter change on the overall design performance. Furthermore, silicon prediction allows design engineers to perform model-to-hardware correlation between the Tempus STA environment and test silicon. Using silicon prediction, teams are empowered to perform true signoff and PPA optimization with predicted delays using accurate silicon models.

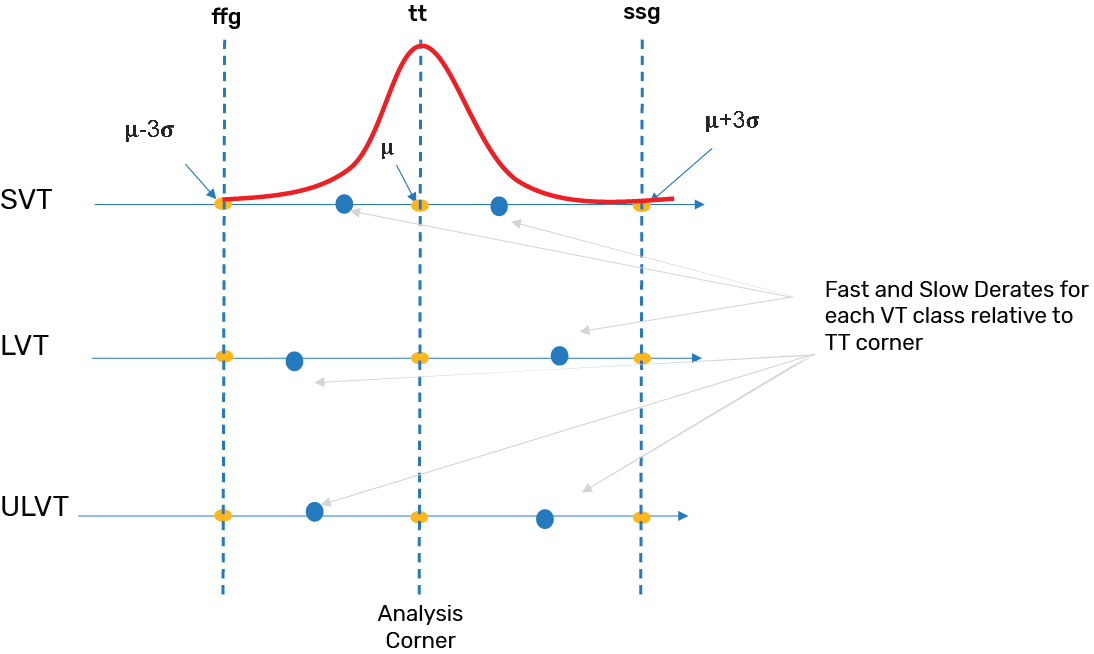

VT Skew Robustness - Advanced Techniques Addressing Pessimistic STA Methodology

VT skew robustness is the fifth analysis capability in the Tempus DRA Suite that provides a more accurate means of modeling variation on designs employing multiple VT class libraries within the clock tree. Using VT skew robustness, the design engineer defines VT classes and their associated fast and slow derates. VT skew robustness then performs an intelligently enumerated series of analyses to determine the worst-case slack based on the launch and capture path compositions. This advanced approach adds confidence and reduces pessimism compared to traditional STA signoff methodologies.