Success Story

Renesas and Cadence

Boosting Productivity by 6X by Leveraging Xcelium ML and Verisium Platforms

Overview

The Customer

Renesas is a global leader in microcontroller (MCU), analog, power, and system-on-chip (SoC) products. It has manufacturing, design, and sales operations in approximately 30+ countries. Renesas’ market-proven MCU, SoC products, and technologies provide solutions to key market segments such as IoT, industrial, infrastructure, and automotive.

Key Challenges

Verification remains the indispensable core of SoC design, and the ever-increasing functionality over SoCs drives their ever-increasing complexity. The state space, and therefore verification space, for SoCs, increases exponentially with gate count, and thus the need for total verification throughput, finding and fixing bugs, grows exponentially as well. Renesas Verification teams also found it the same way, and they noticed that meeting verification and coverage goals with confined resources and budgets is challenging with the increasing functional density and rising number of IP blocks over SoCs. Further, they discovered that the verification throughput is a significant bottleneck, and with the dynamic market scenario, it is crucial to meet the strict tapeout schedules dictated by market pressures. To stay ahead of the competition, Renesas needed a solution that could help shorten the overall design cycle, accelerate the coverage closure, improve productivity, and save resources.

The Solution

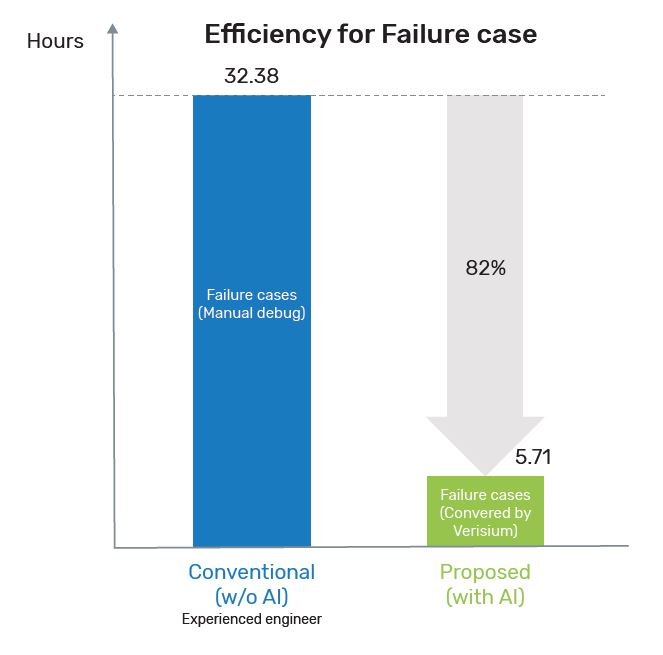

Renesas adopted Cadence AI-based Verisium Platform and Xcelium ML App to solve this problem. The proposed solution provides a holistic debug environment that allows engineers to debug from IP to SoC-level design. The solution (Verisium and Xcelium ML App) helped the Renesas verification team to accelerate the verification curve by optimizing the simulation regressions with preserved coverage. Its SmartLog technology and capabilities like waveform, schematic, and driver tracing enable fast, comprehensive, interactive post-process debug flows. It helped Renesas boost coverage, optimize verification workloads, and accelerate the root-cause analysis of design bugs for complex SoCs. The machine learning technology in Xcelium App enabled Renesas verification teams to generate a well-condensed regression. Using the existing randomized testbench to simulate corner case scenarios enabled early bug detection for Renesas.

Cadence’s Verisium Debug allows our engineers to debug from IP- to SoC-level designs. The new waveform format is well-designed for modern verification needs and helps to improve simulation probing performance by 2X.

Noriaki Sakamoto, president of Renesas Design Vietnam Co

Renesas mentioned that Verisium Debug played a central role in improving debug productivity, and they achieved improvement in verification cycles leveraging the below mentioned apps:

By incorporating the Cadence Xcelium Machine Learning App as part of our verification flow, we were able to accelerate coverage convergence with fewer regression tests. This helps us meet our aggressive deadlines while maximizing verification performance and overall verification efficiency.

Tatsuya Kamei, Distinguished Engineer, HPC Digital SOC Division, Renesas Electronics

Incorporating Xcelium ML App enabled Renesas with considerable regression compression and saving in regression cycle times without any loss in coverage.

Results and Customer Benefits

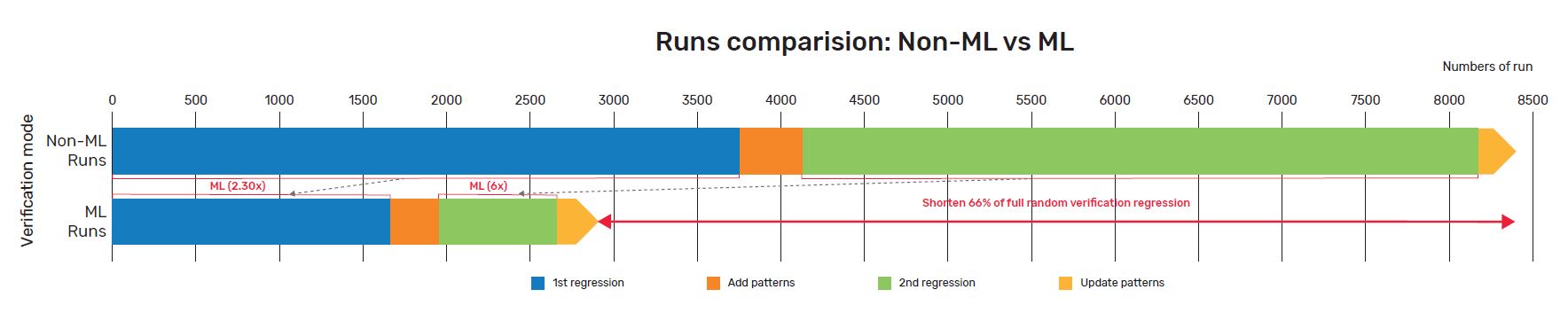

Verisium AI-Driven apps enabled Renesas to improve the entire debug productivity by up to 6X and shorten the overall verification cycle. Renesas achieved excellent results, saving 66% of their complete random verification regression cycle. The Xcelium ML App helped them achieve 2.2X compression with 100% coverage score regain. Furthermore, Renesas achieved a 3.6X reduction with a 100% coverage score regained when using the ML regression on the first derivative.

The reduction in ML regression runs (1168 from 3774) helped Renesas to meet the time-to-market demands. In addition to saving resources, time and accelerating coverage closure, the Xcelium ML app saved ~27 work hours for Renesas. The three mentioned Verisium Apps in Cadence’s Verisium AI-Driven Verification Platform boosted the verification productivity up to 6X for Renesas.

Summary

Renesas realized a considerable boost in productivity and a tremendous reduction in regression runs by adopting Cadence’s AI-based Verisium Platform and Xcelium ML App. The solution helped Renesas to boost coverage and accelerate the root-cause analysis of design bugs on complete SoCs. Leveraging AI/ML increased their verification productivity by up to 6X.