Success Story

IAC and Cadence

Significantly Cut Design Time for Next-Generation Smart Wearable Devices

Overview

Key Challenges

Inventec Appliances Corporation (IAC), a subsidiary of Inventec Group, is committed to continuous innovation of design and manufacturing of Industry 4.0 smart products that are used in a wide range of applications around the world, including wearable devices (Figure 1), smart homes, smart healthcare, autonomous driving, mobile phones, and consumer electronics.

As wearable devices move toward lighter, longer-range, and higher-speed applications with more intelligence, meeting design specifications while maintaining size and cost constraints—all in a short timeframe—is becoming more challenging.

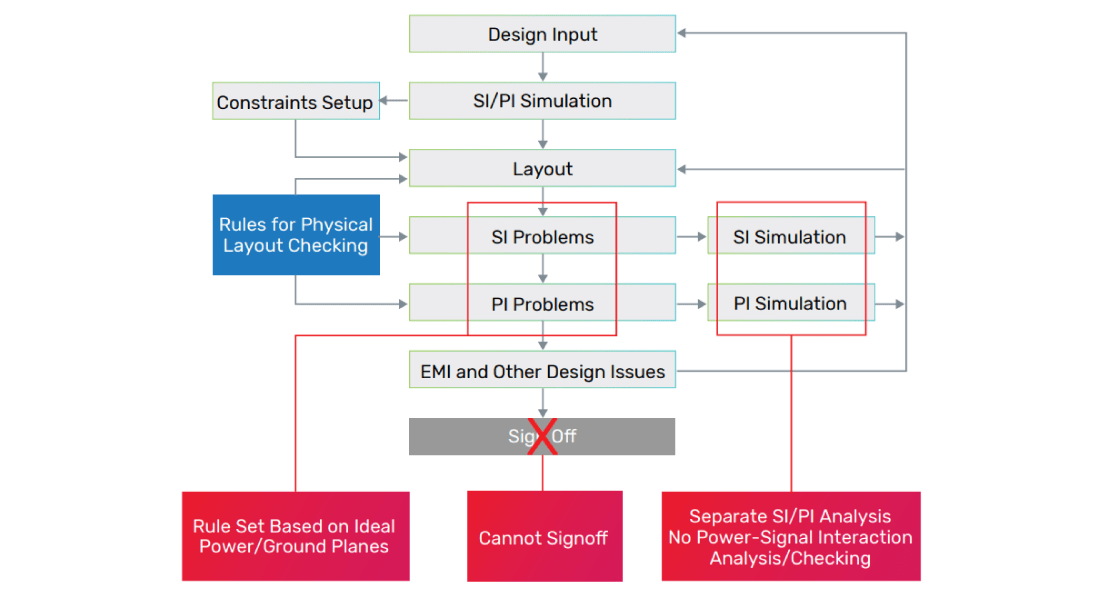

The IAC design team faced several signal/power integrity (SI/PI) issues when verifying high-performance interfaces such as low-power double data rate 4 (LPDDR4). For example, LPDDR4 is plagued by power-aware SI problems such as simultaneous switching noise (SSN), which adversely affects the random jitter. This impacts the eye diagram and requires further optimization of the system noise associated with the interface. However, the IAC team did not have an ideal simulation workflow to complete the SSN analysis. Instead, they performed SI and PI analyses separately; however, the process of bringing them together for power-aware SI was very time-consuming (Figure 2). This was especially true if a problem was detected that required repeating the entire interconnect model extraction process with each layout change, which significantly affected the product delivery timeline.

The Solution

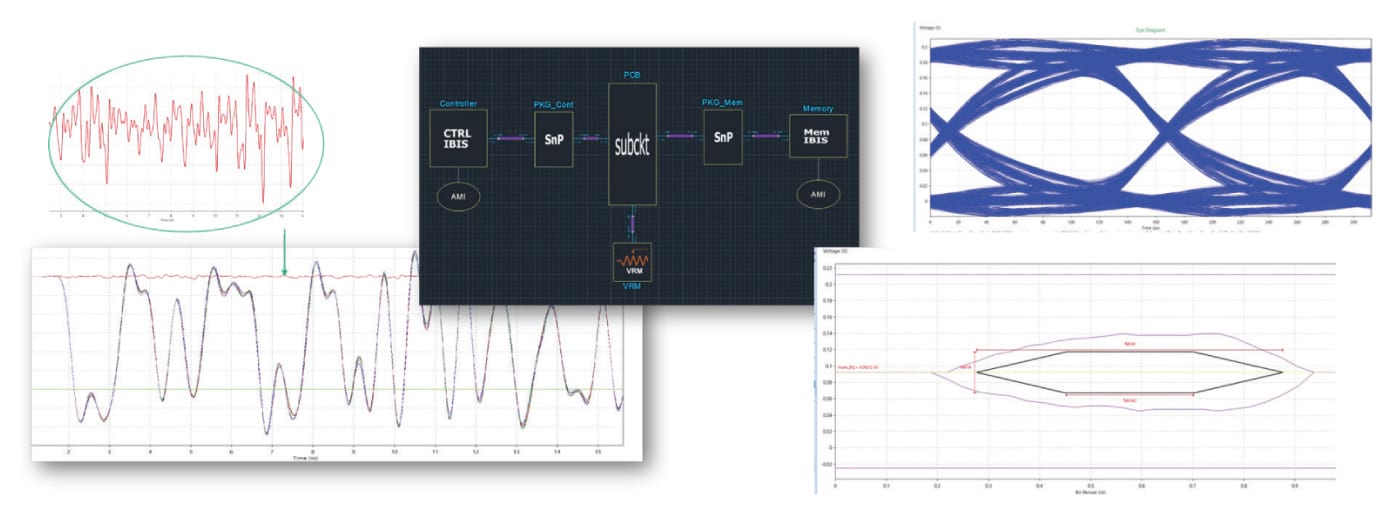

The IAC team turned to the Cadence Sigrity X next-generation SI/PI analysis solution, which works in tandem with the Clarity 3D Solver and is deeply integrated with the Allegro PCB Design tool. In the very early stage of design, the Sigrity hybrid solver and Clarity 3D Solver easily extracted the full LPDDR4 interface without missing any power or ground elements from the .brd file exported from Allegro PCB Designer. The resultant S-parameters of the PCB LPDDR4 channel were optimized to meet the expected performance. In addition, with the input/output (I/O) IBIS model, package model, and channel model, the Clarity 3D Solver and Sigrity Advanced SI simulation tools were used to simulate multiple bus signals simultaneously, creating a highly accurate eye diagram that was easily verified against the LPDDR4 Joint Electron Device Engineering Council (JEDEC) standard. The risk of manually reducing the modeling structure size was eliminated and the ability to quickly obtain the power-aware eye diagram (Figure 3) compliance report accelerated design iterations, resulting in a high-quality product being delivered on time.

IAC is committed to R&D and manufacturing smart terminal products in various fields. The Cadence Sigrity X and Clarity 3D Solver technologies have excellent performance and accuracy, which help us find and solve SI/PI problems early in the design process for our smart wearable devices

Li Zhiyong, manager of the IAC Engineering Development Department

Summary

The Cadence Sigrity X next-generation SI/PI analysis solution, combined with the Clarity 3D Solver integrated with the Allegro PCB Design tool, enabled the IAC team to overcome their (SI/PI) challenges when verifying high-performance interfaces. The solution helped the team accelerate design iterations and deliver a high-performing product that met exacting specifications on time.

Graser Taiwan

Graser is a long-standing valued channel partner of Cadence in Taiwan, and played a critical role in the success story of IAC by providing technical expertise and support to help the IAC team overcome their SI/PI challenges. Graser’s analysis of the challenge revealed the need for power-aware SI analysis, which required a more streamlined simulation workflow than the IAC team currently had in place. Graser recommended the Cadence Sigrity X and Clarity 3D Solver solutions, which together provided a more efficient and integrated simulation workflow. Graser followed up with a thorough tech review and helped to optimize the system noise associated with the LPDDR4 interface. With Graser’s support, the IAC team was able to complete the project on time and meet the design specifications while maintaining size and cost constraints.

At Graser, we are dedicated to providing our customers with the most advanced Cadence EDA tools to help them overcome their toughest design challenges. We are thrilled to partner with IAC to accelerate their growth in this SI/PI field.

Lillian Pan, general manager, Graser

Learn More About Cadence’s Technologies

Sigrity X Technology

Sigrity X delivers up to 10X performance without any loss of accuracy, which is achieved using massively distributed simulation in the cloud (or large on-premises data centers). The Sigrity X technology is available across the range of Sigrity products: PowerSI, PowerDC, XtractIM, SystemSI, and OptimizePI.

Clarity 3D Solver

Cadence Clarity 3D Solver is a 3D electromagnetic (EM) simulation software tool for designing critical interconnects for PCBs, IC packages, and system on IC (SoIC) designs.

Allegro PCB Designer

Allegro PCB Design brings your innovative and bleedingedge designs to life. The constraint-driven environment provides real-time visual feedback and ensures the functionality and manufacturability of your PCBs while allowing you to keep designing.