- Overview

- Vision DSP Family Features and Benefits

- Vision 341 DSP Features and Benefits

- Vision 240 DSP Features and Benefits

- Vision 331 DSP Features and Benefits

- Vision 230 DSP Features and Benefits

- Vision 130 DSP Features and Benefits

- Vision 110 DSP Features and Benefits

- Vision 4DR Accelerator Features and Benefits

- Library Support

- Toolchain

- AI Software Support

- Cadence Services and Support

Product Overview

Tensilica Vision DSP and Accelerator Family

High-performance, low-energy camera, radar, lidar, and AI processing

The Cadence Tensilica Vision family is designed for demanding embedded vision, camera, radar, and artificial intelligence (AI) applications in the mobile, automotive, surveillance, augmented reality (AR) / virtual reality (VR), drone, and wearable markets. The six DSPs in the vision family offer 3.84 TOPS to 0.4 TOPS maximum performance. All Vision DSPs are built on the same VLIW SIMD architecture and offer an N-way programming model, allowing easy software migration from each DSP. All these DSPs offer the best DSP performance and the necessary MAC for today’s AI workload. Tensilica provides a comprehensive offering with low-end 128-bit SIMD, mid-range 512-bit SIMD, and high-end 1024-bit SIMD. These DSPs are also ISO26262-ready for the automotive market. Plus, as all our DSPs are built on the highly successful Cadence Tensilica Xtensa processor, the Vision DSP family shares the same development environment and can be extended using the Tensilica Instruction Extension (TIE).

In addition to programmable DSPs, the Vision family also offers a Vision 4DR Accelerator targeted at 4D Radar applications for automotive market, providing area, power, and performance advantage over a DSP-only solution.

Overview

Overview

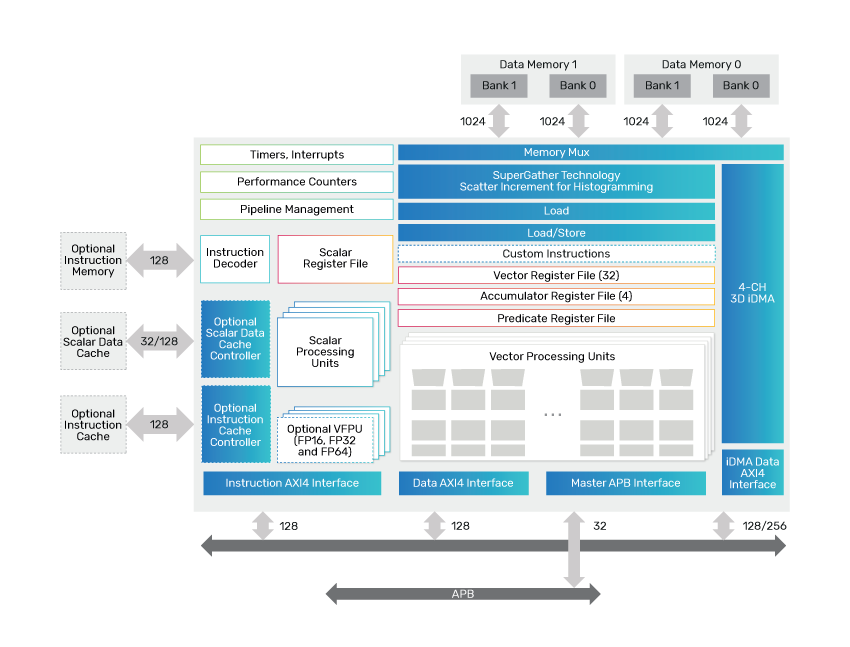

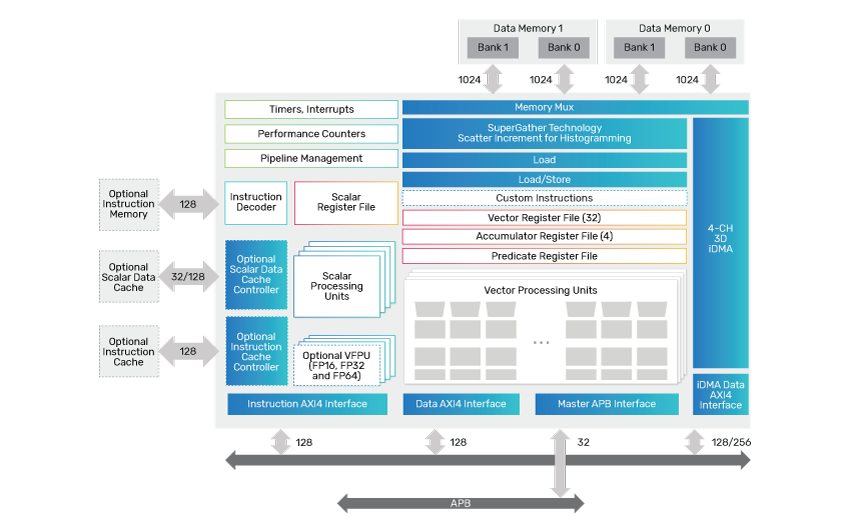

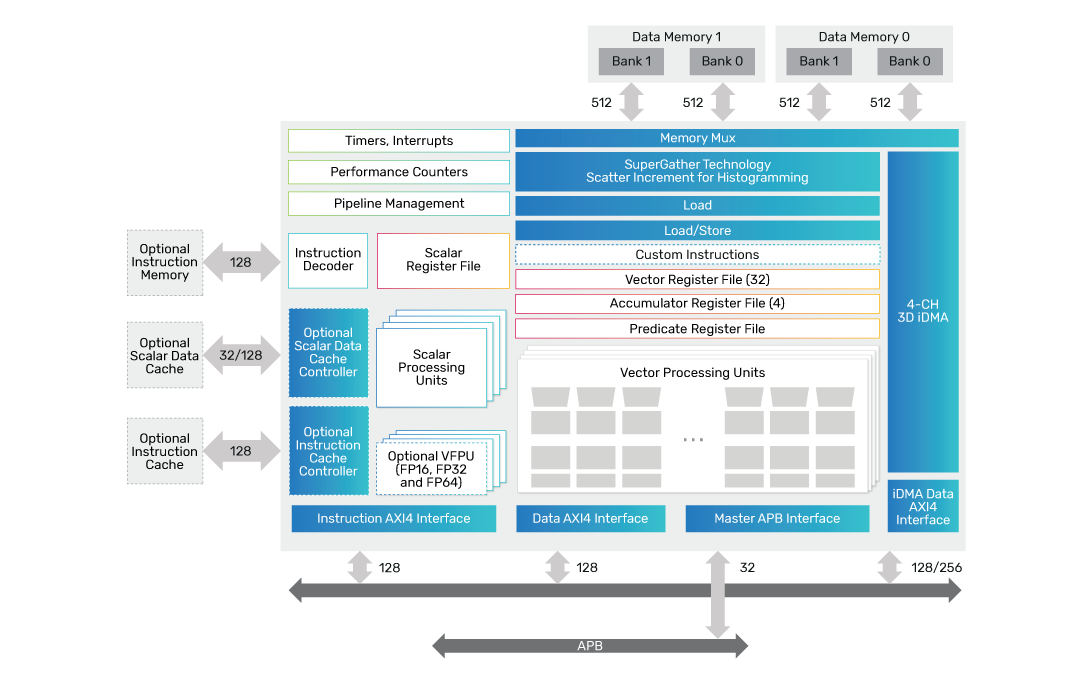

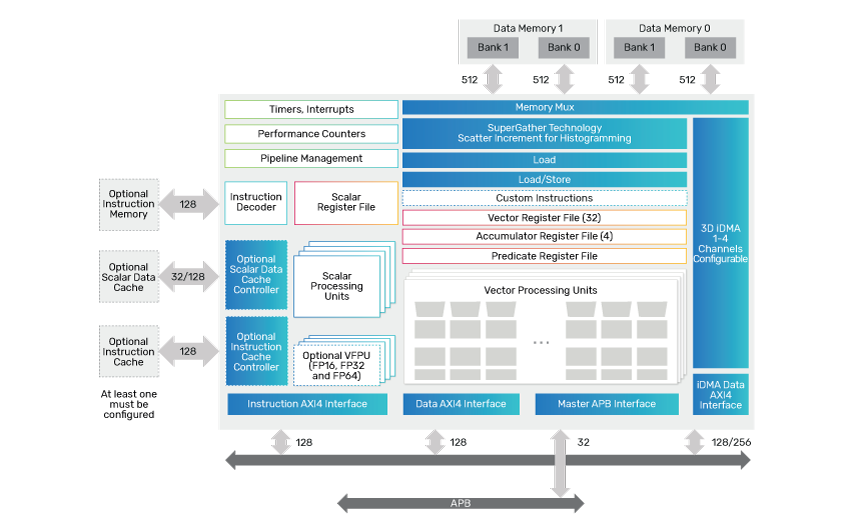

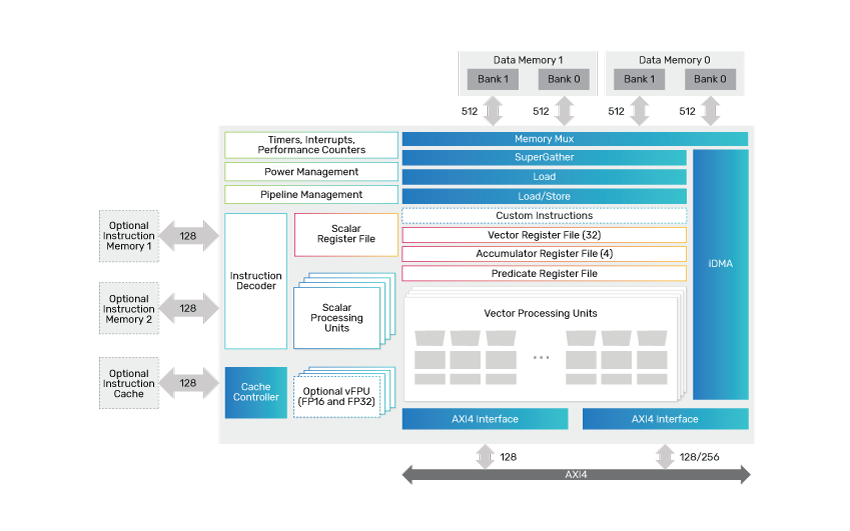

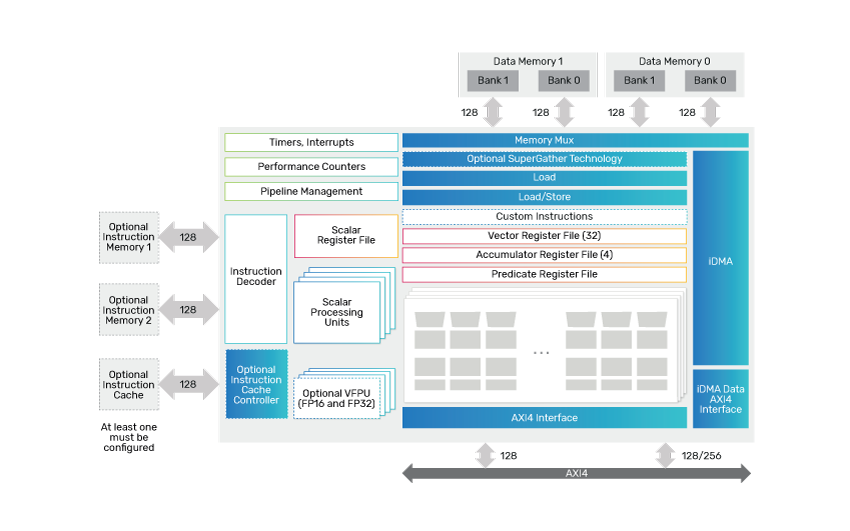

For sufficient sensor data processing throughput, the Vision DSP product architecture incorporates advanced VLIW/SIMD support for the industry’s highest number of ALU and MAC operations per processor cycle and the industry’s widest and most flexible memory bus.

Specialized instructions also allow the Vision DSP products to efficiently speed up sensor data processing. Various architecture enhancements boost performance while keeping energy consumption low. The Vision DSP products provide unprecedented flexibility in system implementations at power-consumption levels that significantly reduce the need for hardware accelerators. The DSPs also offer an integrated DMA engine, an interface for instruction memory, an instruction cache, and two AXI interfaces. Vision 341 and 240 offer the industry’s widest data memory bus of 2048-bit. All DSPs also provide an optional vector floating-point unit supporting double, single-half precision, complex floating point, and bfloat16 operation. All Vision DSPs offer base-level AI accelerations on DSP by offering sufficient 4-bit, 8-bit, and 16-bit MAC acceleration.

Vision 341 and Vision 331 are the latest additions to the vision family and provide the best instruction set to run camera (vision), radar, lidar, and AI workload. Both these DSPs are built on the Xtensa NX controller, offering the best frequency possible. Vision 341 is a 1024-bit SIMD, and Vision 331 is a 512-bit SIMD. The newly introduced Vision 3xx family of DSPs offers the best architecture and instruction set for 4D imaging radar. For certain 4D imaging radar workloads, the 512-bit Vision 331 DSP offers up to 4X performance improvement over the Vision 230 DSP in radar boost mode, while the Vision 341 DSP offers up to 6X performance improvement over the Vision 230 DSP.

Vision 110 and Vision 130 provide a balanced architecture with optimum area, performance, and low energy. These DSPs are built on the latest Xtensa controller LX8, offering all new features for the best system design. Vision 110 with the 128-bit SIMD is the smallest Vision DSP, targeting lower power applications, offering one-third the power and area compared to Vision 130 while offering easy software transition from Vision 130 via the N-way programming model. Vision 110 also provides the flexibility to configure without various features to reduce area and the data RAM, providing the best area for on-sensor integration.

Both Vision 110 and Vision 130 offer the following improvements over previous generations of Vision P1 and Vision P6

|

|

Vision 110 |

Vision 130 |

Vision 230 |

Vision 331 |

Vision 240 |

Vision 341 |

Use Case |

|

|

|

|

|

||

MAX SIMD Width |

|

128 |

512 |

512 |

512 |

1024 |

1024 |

Xtensa Processor |

|

LX8 |

LX8 |

NX |

NX |

NX |

NX |

MAC For AI |

8x8 |

128 |

256 |

512 |

512 |

1024 |

1024 |

SHOW ALL

5 of 18

Table 1: Feature Summary

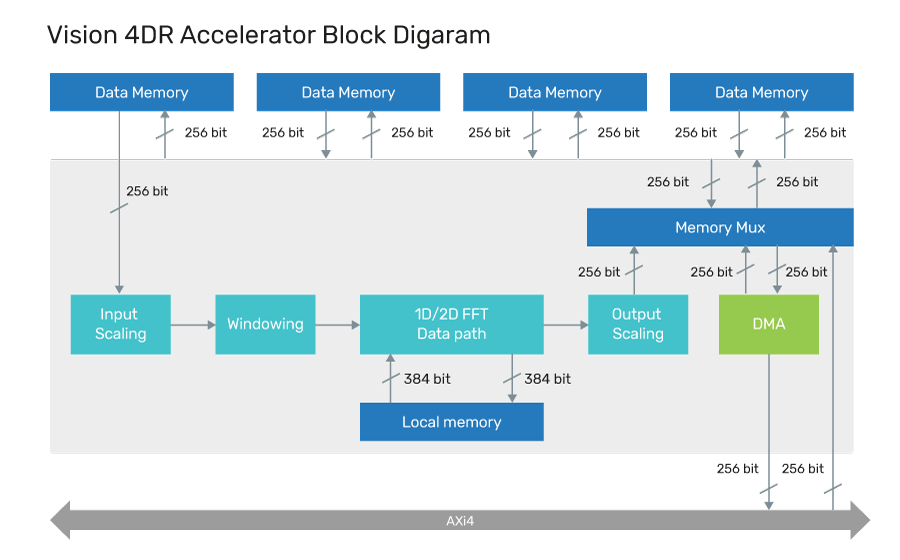

Vision 4DR Accelerator is the first accelerator product targeting 4D Imaging radar applications. As the automotive market moves to 4D radar that provides range, doppler, azimuth, and elevation information with large data cubes, it becomes challenging to implement the radar processing chain just in programmable DSPs. When paired with the new DSPs for 4D imaging radar applications, the Vision 4DR accelerator offers 4X greater performance and up to 6X greater area advantage than a Vision 341 DSP alone and 7X greater performance than a Vision 331 DSP alone.

Vision DSP Family Features and Benefits

Vision 4DR Accelerator Features and Benefits

The Cadence Tensilica Vision 4DR Accelerator is hardware designed to address the increasing computational requirements for 4D Imaging radar in the automotive market. With its much higher performance than a DSP-only solution, a combined solution of Vision 331/341 with Vision 4DR saves considerable power and area.

Library Support

Toolchain

The Vision DSPs are delivered with a complete set of software tools: