As the full custom IC layout suite of the industry-leading Cadence® Virtuoso® Studio, the Virtuoso Layout Suite supports custom analog, digital, RF, and mixed-signal designs at the device, cell, block, and chip levels. The enhanced Virtuoso Layout Suite offers accelerated tool performance and differentiated productivity from flexible connectivity-driven, interactive full custom layout (XL), through electrical-driven assisted custom layout automation (EXL), to the most advanced layout platform that enables full custom layout automation from device to block to chip to package (MXL). Seamlessly integrated with the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment, the Virtuoso Layout Suite enables the creation of differentiated custom silicon that is both fast and silicon accurate.

Overview

As the full custom IC layout suite of the industry-leading Cadence® Virtuoso® Studio, the Virtuoso Layout Suite supports custom analog, digital, RF, and mixed-signal designs at the device, cell, block, and chip levels. The enhanced Virtuoso Layout Suite offers accelerated tool performance and differentiated productivity from flexible connectivity-driven, interactive full custom layout (XL), through electrical-driven assisted custom layout automation (EXL), to the most advanced layout platform that enables full custom layout automation from device to block to chip to package (MXL). Seamlessly integrated with the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment, the Virtuoso Layout Suite enables the creation of differentiated custom silicon that is both fast and silicon accurate.

The Virtuoso Layout Suite is the trusted centerpiece for custom layout creation. The Virtuoso Layout Suite has evolved over more than three decades, solving design challenges as electronic system complexities increase and championing new features, flows, and methodologies to tackle the intricacies introduced with each process technology. It accelerates custom layout with a comprehensive set of user-configurable, easy-to-use pure polygon layout features within a fully hierarchical environment.

The Virtuoso Layout Suite revolutionized device layout creation through parameterized cells (PCells) and empowered skilled design automation engineers to create crafted and customized automation features using the SKILL® scripting language, which provides direct database access, tool configuration, and interoperability with other tools. The correct-by-construction layout paradigm presented the opportunity for connectivity-driven, constraint-driven, and simulation-driven layout floorplanning, automated placement and routing, and assisted layout editing with powerful in-design physical verification and parasitic and electromigration/IR drop (EM-IR) analysis. An electrical-aware design methodology paves the way for new automation tools that maintain design intents throughout the design cycle from schematic creation, simulation, and layout.

The era of chiplets and 2.5/3D integration of integrated circuits (ICs) in a package ushers in greater cohesiveness between chip layout implementation and package layout creation. It is also necessary to co-analyze the parasitic, electrical, and thermal aspects of chip, package, and PCB components to achieve the intended circuit behavior at the end-product level. Cadence is uniquely positioned to provide solutions in all these aspects of implementation, extraction, verification, analysis, and simulation of complete systems. The Virtuoso Layout Suite acts as the central cockpit for IC designers to optimize the layout of chip and package together, invoking appropriate solvers for parasitic and device parameter extraction.

Virtuoso Studio Custom Design Platform

The Virtuoso Studio’s custom design platform includes Virtuoso Schematic Editor, Virtuoso ADE Suite, and the Virtuoso Layout Suite to speed convergence on design goals at every step for front-to-back custom analog, digital, RF, and mixed-signal design flows. The platform is backed by the largest number of process design kits (PDKs) available from the world’s leading foundries, for process nodes from mature 0.60um to advanced 2nm. It is built on the OpenAccess database, engineered by Cadence for industry-wide interoperability.

The custom design platform also interoperates with the Cadence Innovus™ Implementation System’s digital technology via the OpenAccess database, providing a single, complete, coherent, and unified representation of mixed-signal design intent. This mixed-signal design intent is preserved throughout the entire physical implementation phase while operating with multiple levels of design abstractions (device, cell, block, chip), speeding design convergence to realize silicon for complex mixed-signal and system-on-chip (SoC) designs.

Virtuoso Layout Suite Benefits

Three Tiers of Increasing Layout Automation and Designer Productivity

The Virtuoso Layout Suite family of products comprises the layout environment of the industry-standard Virtuoso Studio custom design platform. The Virtuoso Layout Suite preserves design intent throughout the physical implementation process, while managing multiple levels of design abstractions from device, cell, and block levels to the full-chip level. It provides the fastest path to design convergence for mature and advanced-node silicon realization.

The Virtuoso Layout Suite includes three tiers of increasing layout automation and designer productivity. By selectively automating aspects of custom-analog design and providing advanced technologies integrated in a common database, engineers can focus on precision-crafting their designs without sacrificing creativity to repetitive manual tasks.

Virtuoso Layout Suite XL

Virtuoso Layout Suite XL sets the new standard for custom layout authoring to handle the increased complexity of modern designs. Driven by schematic connectivity and design intents, an LVS-correct layout can be done in real time.

Connectivity-driven functions

Generating instances with correct logical connectivity from the schematic forms the foundation of most advanced custom layout automation. The Virtuoso Layout Suite’s Schematic Assistant provides an intuitive interface to cross-probe and highlight instances between schematic and layout. Incremental connectivity-driven binding and incremental check against source ensures that the schematic versus layout mismatches are identified, and you can take corrective action immediately.

The fast multi-threaded connectivity extractor ensures the connectivity propagation from pins to wires, revealing opens and shorts in the layout. Navigator can be used to highlight the routing shapes on the net with flight lines showing opens between terminals. The shape-based net-tracing functionality is a powerful debug capability to identify incorrect connectivity assignments and shorts.

Assisted placement functions

Designer productivity is a pervasive theme in Virtuoso Layout Suite. The connectivity-driven layout creation in the Layout XL tier drives improvements to interactive device placement. The smart snapping of devices to poly and diffusion grids ensures DRC-correct device placement in advanced-process nodes. Automatic chaining of instances generates a compact device arrangement with a continuous diffusion island resulting in area savings.

Virtuoso Layout Suite XL has a unique capability that allows users to “clone” portions of the layout without altering connectivity. What differentiates cloning from a more traditional copy of geometry is that cloning supports both a geometric copy and a connectivity update. This capability is essential in today’s connectivity-driven methodologies. In addition to cloning, synchronous clones enable a single change in a member of a clone to update all partner clones. This capability greatly boosts productivity when working in a connectivity-driven environment.

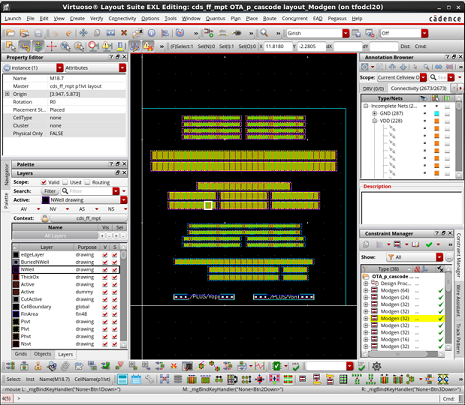

Virtuoso Layout Suite EXL

Virtuoso Layout Suite EXL elevates the custom layout user experience to the next level. Built upon the connectivity-driven Virtuoso Layout XL framework, the EXL tier delivers unique assisted automation capabilities that boost layout designer productivity by 2X to 20X. Awareness of electrical design constraints and circuit simulation results allows the user to perform in-design parasitic and electrical analysis, assisted simulation-driven routing, and electrical constraint checking in real time to produce a correct-by-construction layout.

Design planning and analysis

Virtuoso Layout Suite EXL provides maximum flexibility to plan and analyze analog and mixed-signal designs using hard blocks, soft blocks, and virtual hierarchy. The tool permits top-down and bottom-up floorplanning methodologies and a mix of the two to achieve placement planning, pin optimization, global route planning, and congestion analysis. Virtual hierarchy enables floorplanning of the entire hierarchy without needing to manage multiple cell views. The virtual hierarchies can be converted to real layout cell views with automatic congestion-aware pin placement of the hierarchical cell.

Concurrent layout editing

Empowering layout teams to work collaboratively on the same layout yields faster layout implementation, chip finishing, and routing. Concurrent layout editing promotes partitioning the layout based on areas or layers, assigning partitions to different users to edit them simultaneously, and finally reviewing the edits and merging them into the layout. Collaboration also enables non-destructive edits to the layout for review purposes and performing what-if analyses without managing numerous copies of the layout.

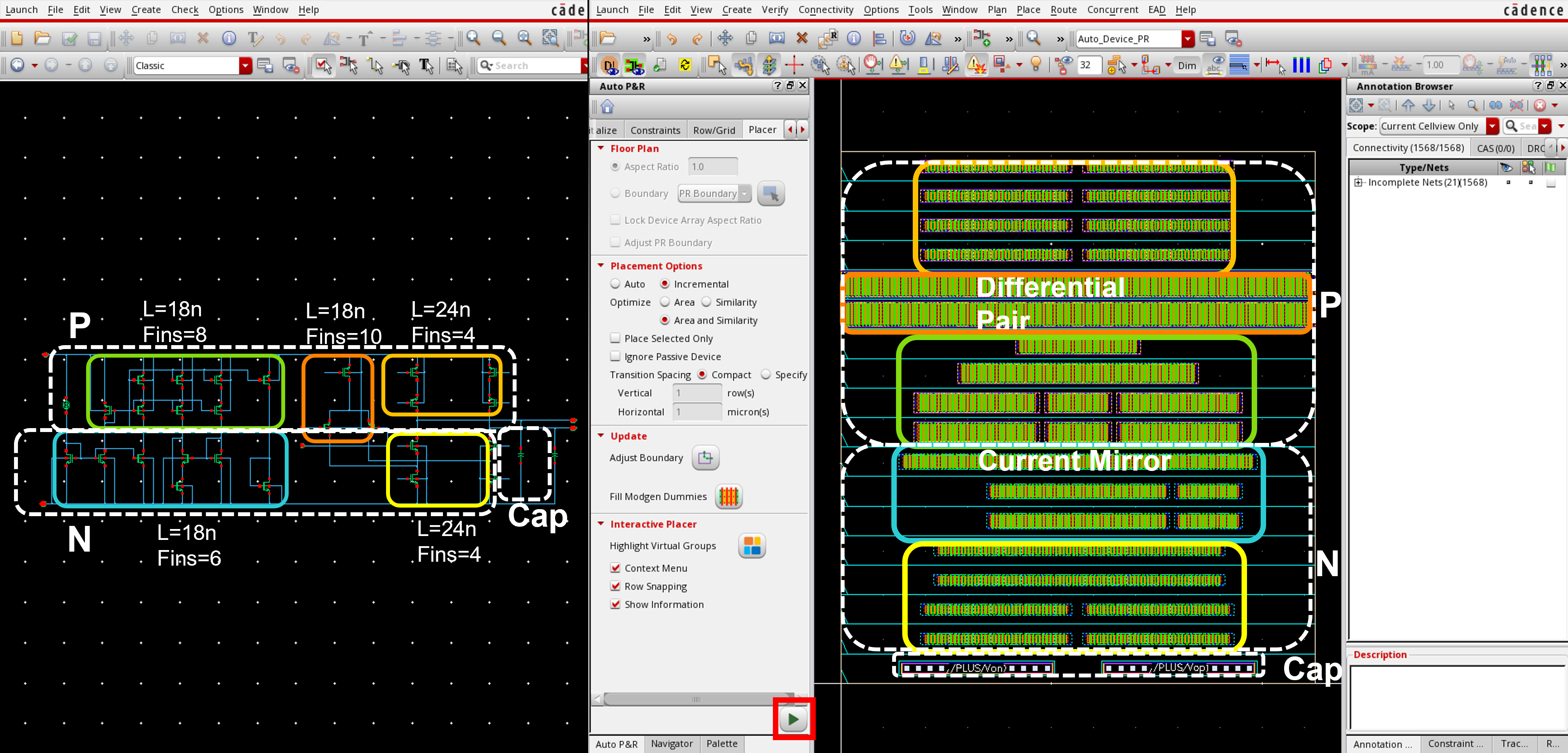

Virtuoso Layout Suite MXL

Virtuoso Layout Suite MXL unleashes the next frontier with new automation technologies for IC design and system-level design capabilities to address the “More than Moore” paradigm. With full automation for layout implementation across all design styles, efficient reuse of design intent to enable layout migration across process nodes, and tight integration of best-in-class tools, Virtuoso Layout Suite MXL covers the whole spectrum of custom layout from device to block to chip to package.

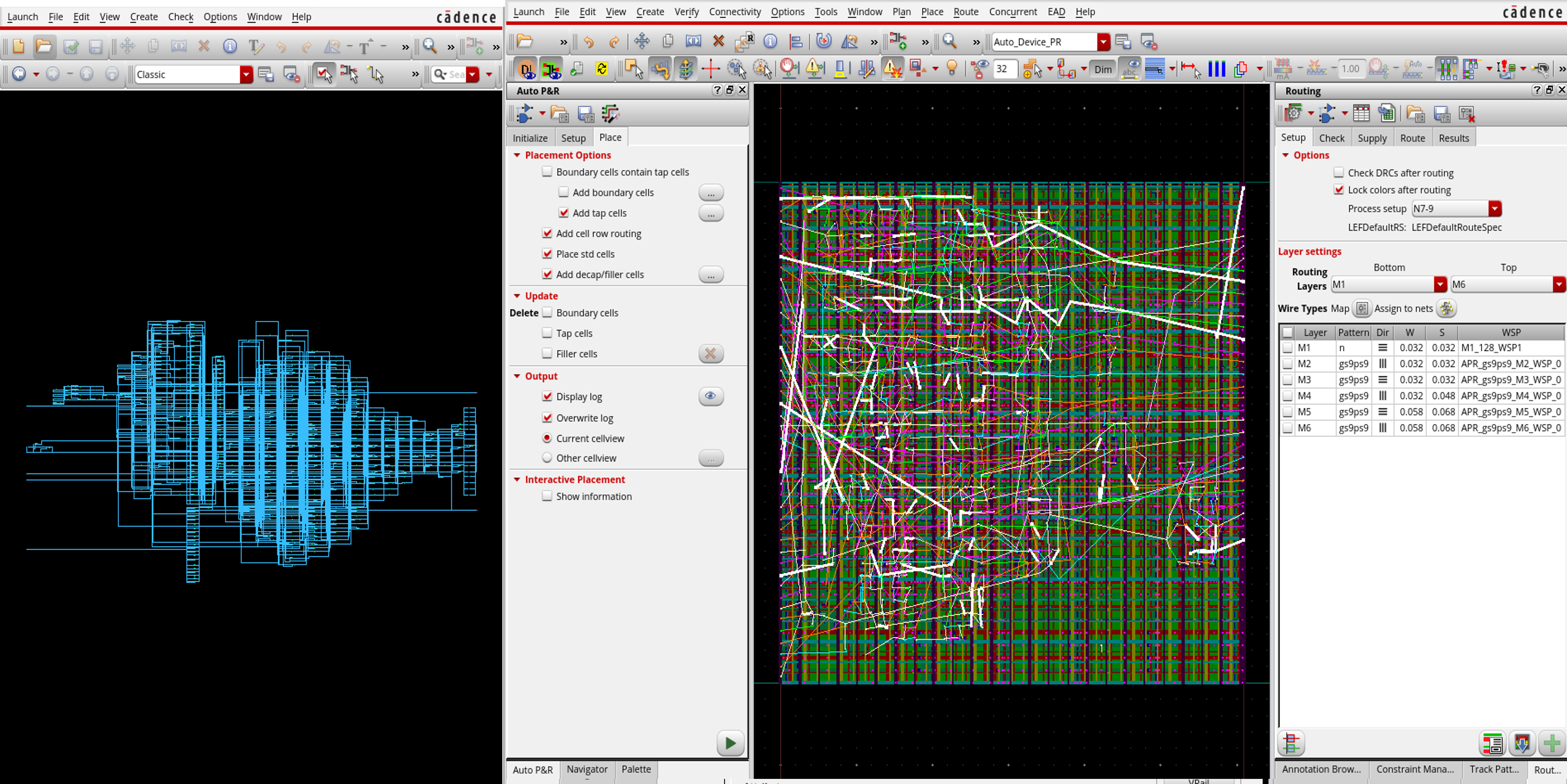

Advanced-node standard cell place and route

Complex design rule challenges on advanced process nodes impact the quality of results from automated standard cell placement and routing tools. Virtuoso Layout Suite MXL provides fast custom digital layout creation using the GigaPlace and NanoRoute engines from the Innovus Implementation System. The familiar graphical use model minimizes the learning curve and utilizes the powerful automation engines from the Innovus Implementation System, leveraging on the common underlying OpenAccess database.

Routing Assistant

The Routing Assistant in Virtuoso Layout Suite MXL is the unified interface to drive the auto-routing tools for different design styles – device, standard cell, and chip assembly. The assistant provides a common spreadsheet-style Routing Constraint Manager to set up routing constraints across all design styles. The different flavors of routing that can be done from the assistant include:

The Routing Assistant facilitates reviewing the connections created by the router, such as wire length and vias used, and checking whether the routing constraints are honored.

Layout migration

You can recreate the layout in your target process node while retaining the critical intents from the source layout within Virtuoso Layout Suite MXL. The tool captures the device groups and the placement and routing topologies from the source layout as templates and then applies the templates in the target process node to generate the target layout.