Datasheet

Cadence Virtuoso Digital Implementation

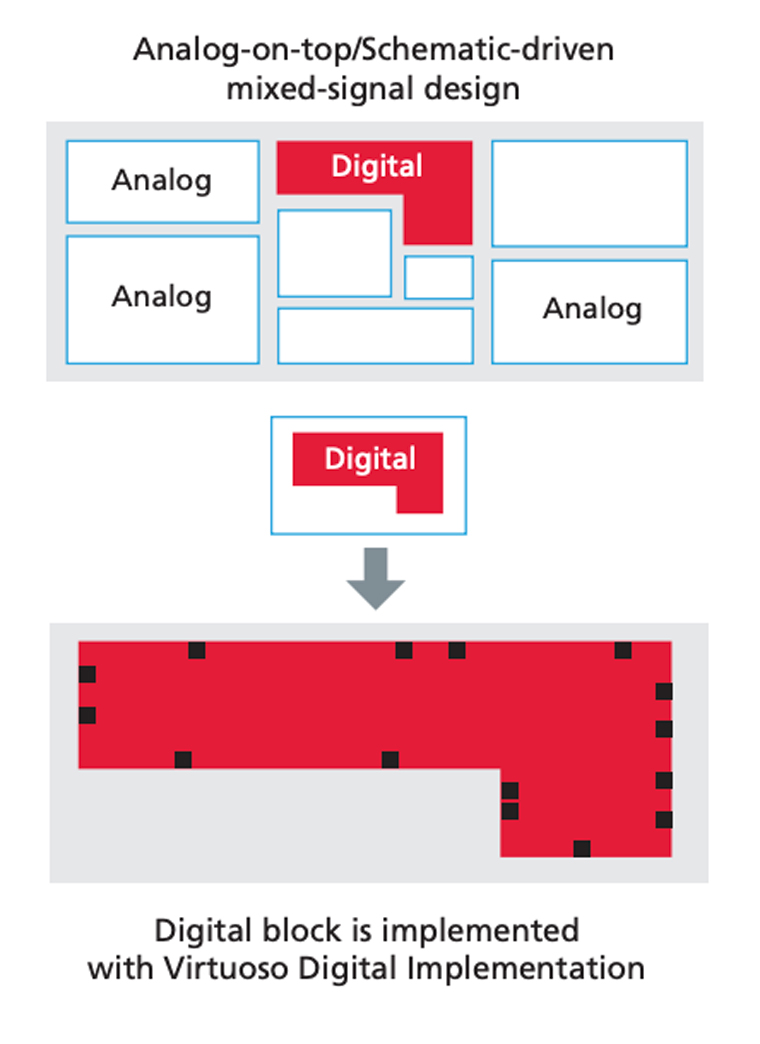

Timing-driven digital block implementation for a mixed-signal design methodology

Cadence Virtuoso Digital Implementation is a complete and automatic system for RTL-to-GDSII block implementation. Based on Encounter RTL Compiler and Encounter Digital Implementation System core technology with superb performance and accuracy in synthesis, implementation, and optimization, the system enables capacity-limited timing-driven block physical implementation from gate-level synthesis with design for test, to floorplanning, placement, routing, and optimization, in the context of an advanced analog-driven mixed-signal design.

Overview

Reach Fast Design Closure on All Objectives

As a part of Cadence’s interoperable mixed-signal methodology on OpenAccess common database, Virtuoso Digital Implementation automatically ensures digital blocks are implemented per timing, power, signal integrity (SI), and physical specifications correctly and consistently across digital and analog boundaries, and across multiple power domains at all time. This implementation allows customers to reach a fast design closure on all objectives for complex mixed-signal designs.