Datasheet

Spectre Simulation Platform

Comprehensive analyses for robust design and verification of analog, RFIC, memory, and mixed-signal designs

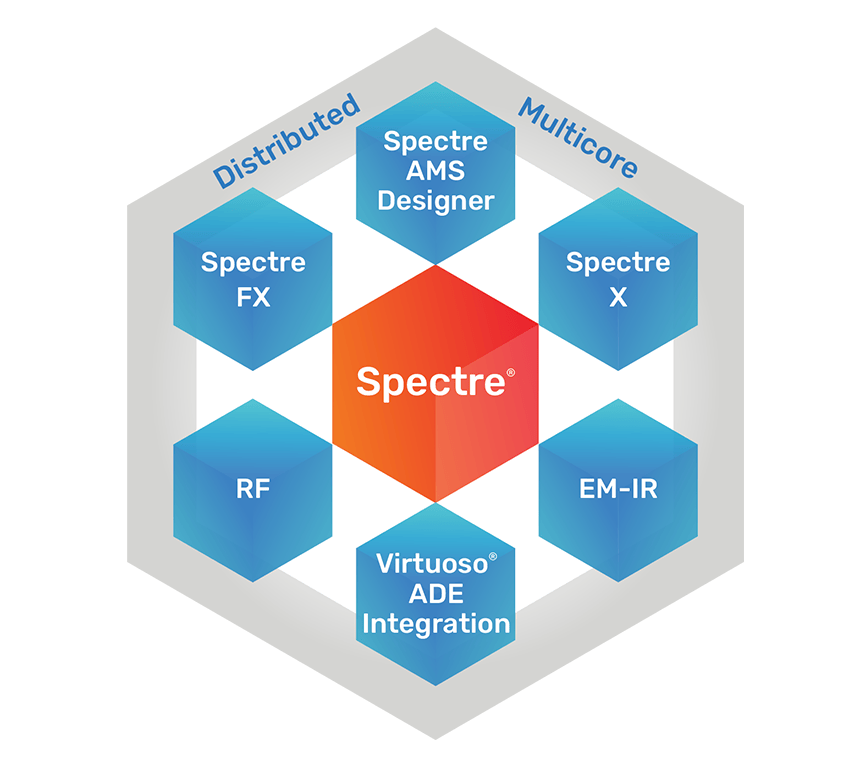

The Cadence Spectre Simulation Platform, built on an advanced infrastructure, combines industry-leading simulation engines to deliver a complete design and verification solution. It meets the changing simulation needs of designers by preserving results and IP as they progress through the design cycle—from architectural exploration, to analog and RF block-level development with flexible and reliable abstraction, including memory design, to final analog and mixed-signal full-chip verification for increased productivity and throughput.

Overview

Spectre Simulation Platform

As the industry’s leading solution for balancing high-performance and capacity needs with analog accuracy, the Cadence Spectre Simulation Platform encompasses multiple solvers that allow a designer to move easily and seamlessly between circuit-, block-, and system-level simulation and verification tasks. The foundation of the platform is a unified set of technologies shared by all of the simulators—the parser, device models, Verilog-A behavioral modeling, input data formats, output data formats, etc.—thereby guaranteeing consistent and accurate evaluation methods regardless of the simulator selected. In addition to the individual solvers, the Spectre simulation technology is well integrated into other Cadence technology platforms, including Xcelium Logic Simulation, Liberate Trio Characterization Suite, Legato Reliability Solution, Virtuoso ADE Product Suite, Voltus-Fi Custom Power Integrity Solution, and the Virtuoso RF Solution, to provide the industry’s most comprehensive cross-domain simulation solution.

Benefits

Features

Silicon-accurate modeling

The Spectre Simulation Platform offers the same device model equations across all simulators, eliminating model correlation issues and enabling faster convergence on simulation results. Common equations also ensure that new device model updates are available with all the simulators at the same time. Spectre device models are provided by the world’s leading foundries for all kinds of different technology nodes

Greater performance and capacity

The Spectre APS, Spectre X Simulator, Spectre RF Option, Spectre FX Simulator, and Spectre AMS Designer simulation engines provide the best combination of performance and capacity for verification of analog/RF and mixed-signal design without sacrificing accuracy of results.

Post-layout simulation

The Spectre Simulation Platform offers a flexible solution for SPICE-level post-layout simulations of complex and large designs—with millions of circuit devices dominated by parasitics. The Spectre Simulation Platform meets the SoC design verification challenge with a combination of unique parasitic stitching techniques and an accurate frequency-based parasitic modeling algorithm. This approach delivers the performance and capacity for post-layout verification of large designs. It also provides an optimized power-net simulation technique and methodology for analysis of effects such as EM-IR, signal integrity, timing, and substrate degradation.

Static and dynamic circuit checks

The Spectre Simulation Platform provides a comprehensive set of static and dynamic circuit checks. These circuit checks address two challenges designers have with simulation verification. Static checks are dedicated electrical rules checks that provide checks on the correctness of the structure of the design without simulation. Dynamic checks are electrical rules checks that run during the simulation and provide useful debugging information about hot spots in the design. Together these tools increase designer efficiency by helping them identify quickly where issues are in the design. These checks are available for Spectre X, Spectre APS, and Spectre FX simulators.

Native device reliability analysis

The Spectre Simulation Platform provides a full-chip native reliability simulation and analysis solution, enabling designers to consider reliability effects from the early stages of design until tapeout. Reliability analysis can simulate the degradation of device characteristics as a function of the circuit operation conditions and time, allowing for designers to ensure enough performance margin over the product’s operating lifetime. Spectre X Simulator and Spectre APS can be used in combination with the Cadence Legato Reliability Solution to extend its capabilities in aging, fault, and thermal analyses.

Native Verilog-A support

The Spectre Simulation Platform offers design abstraction for faster exploration of the design space, allowing better architectural decisions and supporting mixed-level simulation to accelerate top-level functional verification. The Verilog-A support is in full compliance with the Verilog-A 2.0 LRM.

Advanced analog and RF circuit analysis techniques

The advanced architecture of the Spectre Simulation Platform uses proprietary techniques—including adaptive time-step control, sparse matrix solving, and multicore processing—to provide high performance while maintaining signoff accuracy. Tight integration with the Virtuoso ADE Product Suite offers a user-friendly interactive set-up and advanced visualization of statistical results.

The Spectre RF Option to the Spectre X Simulator enhances the performance of the built-in Shooting Newton and Envelope Following Analyses. In addition, the Harmonic Balance solver can now take advantage of multiple cores and can be distributed across machines to maximize performance for fast results.

The Spectre Simulation Platform provides the flexibility to combine design IP from the different sources and abstraction levels necessary for the design and verification of today’s advanced mixed-signal SoCs. It accepts designs in combinations of various hardware description languages, allowing analog bottom-up and digital top-down design methodologies to link and enable complete analog/mixedsignal full-chip verification.