Datasheet

Spectre AMS Designer

Advanced mixed-signal simulation solution

The Cadence Spectre AMS Designer provides an advanced mixed-signal simulation solution for the design and verification of analog, RF, memory, and mixed-signal silicon realization. It is integrated with the Cadence Virtuoso full-custom environment as well as the Cadence Xcelium Parallel Logic Simulator. Spectre AMS Designer provides a single-simulation executable with flexible abstraction support through the standard mixed-signal languages (Verilog-AMS and VHDL-AMS), SystemVerilog, and/or SPICE-level models. As the bridge between the analog and digital domains, it enables users to choose the right analog solver for the right design or verification task. Designers can choose Spectre technologies for SPICEaccurate block-level analog and RF designs: Spectre Accelerated Parallel Simulator (APS), Spectre RF Option, Spectre X Simulator, and Spectre eXtensive Partioning Simulator (XPS).

Overview

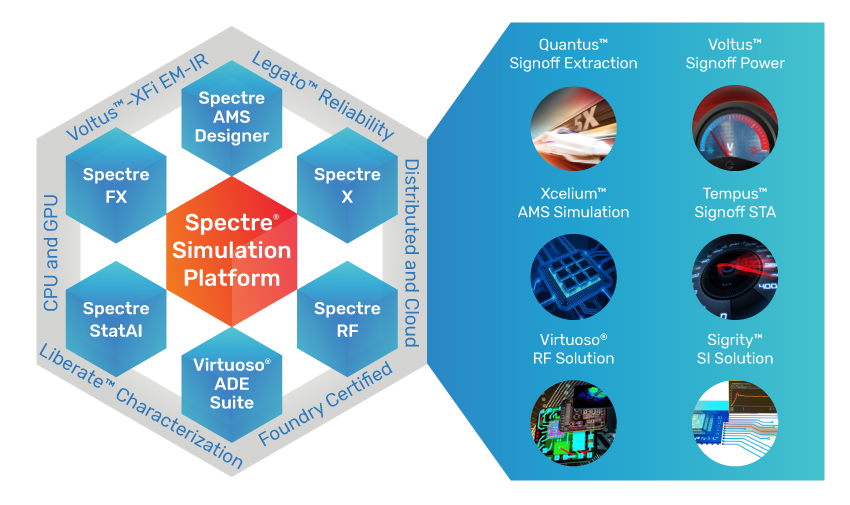

Spectre Simulation Platform

As the industry’s leading solution for balancing high-performance and capacity needs with analog accuracy, the Cadence Spectre Simulation Platform encompasses multiple solvers that allow a designer to move easily and seamlessly between circuit-, block-, and system-level simulation and verification tasks. The foundation of the platform is a unified set of technologies shared by all of the simulators—the parser, device models, Verilog-A behavioral modeling, input data formats, output data formats, etc.—thereby guaranteeing consistent and accurate evaluation methods regardless of the simulator selected. In addition to the individual solvers, the Spectre simulation technology is well integrated into other Cadence technology platforms, including Xcelium Logic Simulation, Liberate Trio Characterization Suite, Legato Reliability Solution, Virtuoso ADE Product Suite, Voltus-Fi Custom Power Integrity Solution, and the Virtuoso RF Solution, to provide the industry’s most comprehensive cross-domain simulation solution.

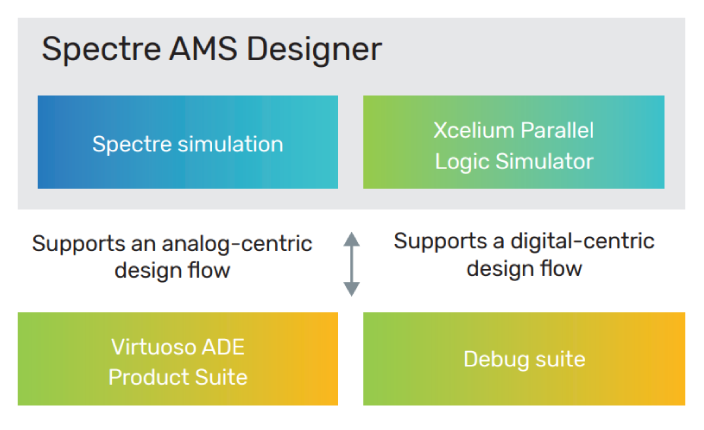

Spectre AMS Designer

Features

Methodology-independent design convergence

Spectre AMS Designer provides the flexibility to combine IP from different sources and in different formats for today’s SoC designs. It does more than just co-simulate analog and digital blocks. By treating Virtuoso Schematic Editor blocks and textual descriptions equally, Spectre AMS Designer allows different points of data entry. It accepts descriptions in the standard language formats of Verilog-AMS, VHDL-AMS, Verilog-A, Verilog, VHDL, SystemVerilog, and SystemC, as well as SPICE, and performs simulation on any combination of these languages. This allows bottom-up and top-down design methodologies to converge into a fully functional design.

Different levels of abstraction, such as Verilog-AMS or VHDL-AMS behavioral models and schematic representation, are easily interchangeable to allow the design to change over time from full behavioral to full transistor. The entire design is configured using the hierarchy editor, which facilitates the viewing and design preparation of a complex mixed-signal design. Automatically inserted interface elements are used to translate signals from one domain to the next, leaving the user free to simulate with different design configurations to easily trade off simulation speed for simulation accuracy.

The SpectreAMS Designer also supports IP encryption using RSA technology, which allows the user to establish both IP reuse and virtual-prototyping methodologies.

Integrated with proven Spectre and Xcelium simulation technologies

Spectre AMS Designer is a mixed-signal simulator based on the proven technology of the Spectre Circuit Simulator, Spectre APS, Spectre X Simulator, and Spectre XPS, and the Xcelium digital simulation capabilities. You can choose different releases of Spectre and Xcelium technologies for your mixed-signal simulation.

Analog-centric flow with Virtuoso environment

Spectre AMS Designer is tightly integrated with the Virtuoso ADE Product Suite for mixed-signal block design. It uses native Analog Design Environment netlisting technologies to combine schematics and behavioral views, enabling users to independently manage the level of abstraction of each block. The entire design is configured using the hierarchy editor, which facilitates the viewing and design preparation of a complex mixed-signal design.

Digital-centric flow with Xcelium simulation

Spectre AMS Designer works natively in the Xcelium environment for digital-centric verification. A single control file is used to define how analog blocks are integrated into the digital SoC. Analog and RTL blocks can be easily interchanged to trade off accuracy and performance. It supports all features in the Xcelium environment including testbench analysis, Cadence technology, and verification planning.