Datasheet

Legato Reliability Solution

Industry’s first complete analog IC design-for-reliability solution

The Cadence Legato Reliability Solution provides analog designers with the tools they need to manage their design’s reliability throughout the product lifecycle. Responding to the challenges of designing for mission-critical applications such as automotive, aerospace, and medical design, the Legato Reliability Solution includes new technology to simulate the manufacturing test’s ability to identify and eliminate defective parts, the effect of temperature on circuit electrical performance, and changes in devices over time including the effects of temperature and process variation on aging.

Overview

Overview

The Legato Reliability Solution addresses the challenges and evolving product lifecycle requirements of mission-critical systems such as automotive, medical, aerospace and defense, and communications. The Legato Reliability Solution targets three key issues designers face: how to eliminate early failures due to test escapes, how to ensure devices survive in extreme operating conditions, and how to extend product life. Analog defect simulation allows designers to simulate their designs with manufacturing defects to ensure the test eliminates bad dies. Electrothermal simulation allows designers to simulate the effect of extreme operating conditions on a circuit’s dynamic performance. And advanced aging analysis allows designers to include the effects that accelerate aging in the analysis.

Key Benefits

Electrothermal Simulation

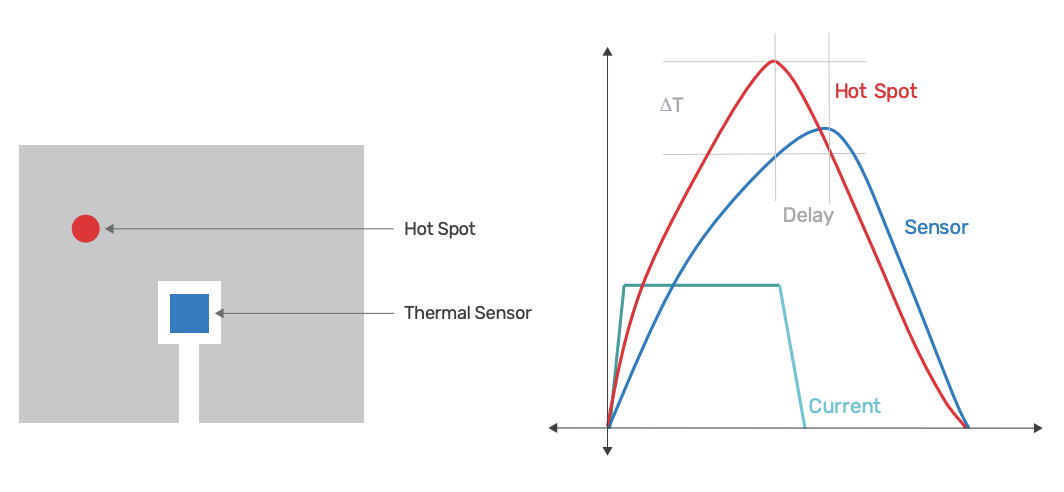

During the normal operating lifetime, one of the major sources of failures is thermal overstress. Devices that drive actuators operate at high power, which further increases the temperature of the device (Figure 2). The stress of operating at high temperature can cause devices that have been designed for a long operating lifetime to fail sooner. The Legato Reliability Solution’s electrothermal simulation provides two electrothermal simulation engines: static and dynamic. The static engine analyzes the average temperature rise of a die during normal operation. The dynamic engine analyzes the warm-up and cool-down temperature transients during normal operation. A built-in thermal extractor creates the thermal model of the die that is used in thermal simulation to simulate the temperature rise due to device power dissipation. Electrothermal simulation is based on the Spectre APS transient analysis, allowing designers to easily assess the effect of on-die temperature variation on circuit performance.

Advanced Aging Analysis

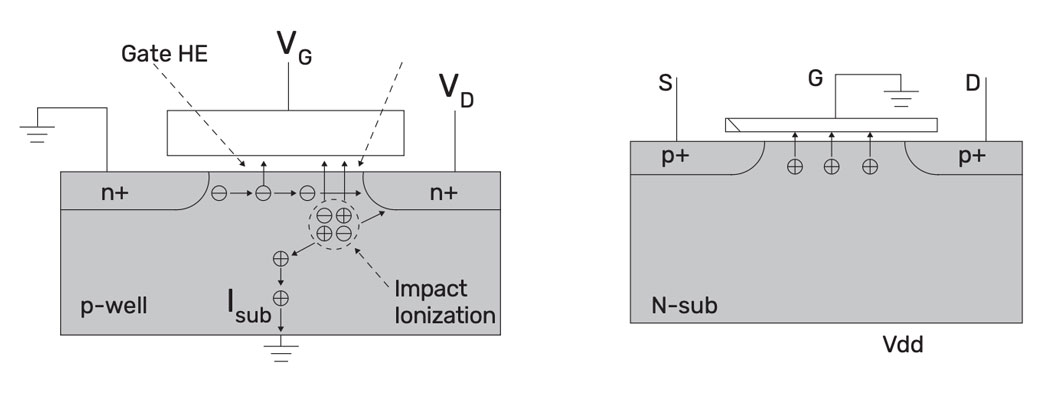

Device wear-out results in end-of-life failures. To extend device lifetime, designers need to accurately predict the effect of stress on a device lifetime. Until now, designers had to account for each source of device degradation in isolation. They use reliability analysis to estimate device in one analysis due to electrical stress, then de-rate the lifetime based on estimated die temperature and the effect of process variation. Advanced aging analysis unifies these analyses, so designers can include all the sources of device degradation. In addition, a new device aging model based on the most recent research in device physics provides better prediction of device degradation due to hot carrier injection (HCI) (Figure 3) and bias temperature instability (BTI). The Legato Reliability Solution’s advanced aging analysis provides designers the ability to better predict the operating lifetime of their designs.