Datasheet

Cadence First Encounter Design Exploration and Prototyping

A flexible, signoff-driven environment for fast implementation of giga-scale designs

Cadence First Encounter Design Exploration and Prototyping offers a comprehensive flat and hierarchical design planning, analysis, and debug environment for complex designs. Its GigaFlex technology adapts to growing capacity requirements while still retaining the relevant timing, placement, and congestion information to accurately plan and implement 100M+ instance designs. The latest advanced node and low-power capabilities make hierarchical implementation of high-speed and advanced node designs faster and easier, and produce designs that consume lower power. In addition, with unique partitioning and budgeting capabilities, First Encounter technology ensures convergence and provides a predictable path to design closure.

Overview

First Encounter Technology

Accommodating today’s chip design requirements within narrow market windows has led to a predictability crisis. How can engineers determine design feasibility for larger, higherperformance, power-hungry chips with an incomplete netlist, library, and constraints? And how can they quickly assess floorplans for congestion, timing, and power without having to go into real implementation?

First Encounter technology addresses these challenges and more. It spans silicon virtual prototyping, automatic floorplanning, physical synthesis, hierarchical controls for partitioning and budgeting, legal macro and standard cell placement, complete power-grid design and optimization, and hierarchical clock synthesis for high-performance, complex 100M+ instance designs. With such comprehensive capabilities, First Encounter technology helps customers meet their time-to-market requirements confidently, and with significant performance and productivity gains.

Benefits

Features

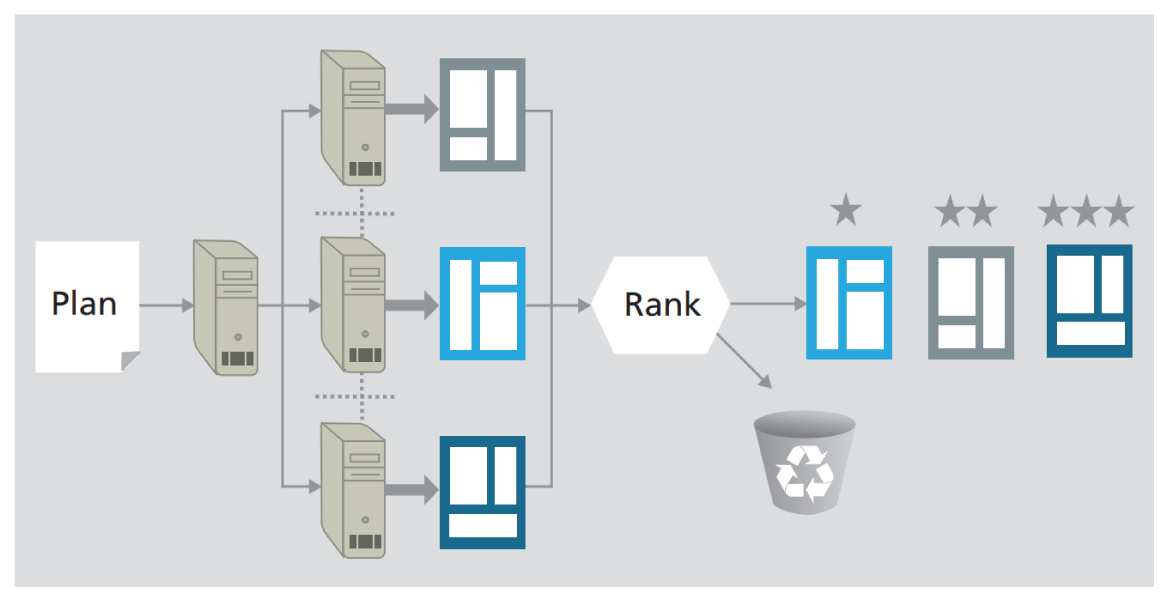

Early design exploration

Today’s physical design teams start physical implementation and design planning very early in the design cycle— with multiple versions of the design netlist—to determine design feasibility. Among their questions: Can the design be implemented in the required area? Can the design operate at the desired speed? Does it meet power requirements?

First Encounter technology addresses all of these issues and more:

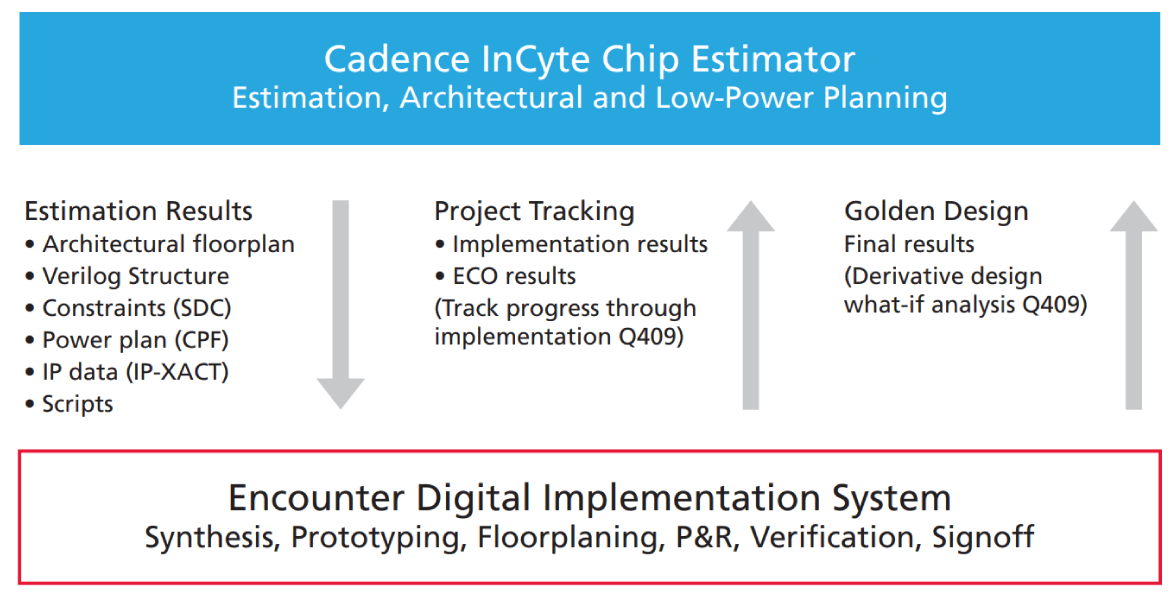

To bring physical predictability into your estimations, you can link into the First Encounter environment from the Cadence Chip Planning System.

Silicon virtual prototyping and hierarchical capabilities

First Encounter technology supports all implementation styles—from flat or hierarchical to single or multi-VDD. Capabilities for fast power-grid design and optimization, global routing, in-place optimization, and global timing debug provide a robust infrastructure to implement any methodology.

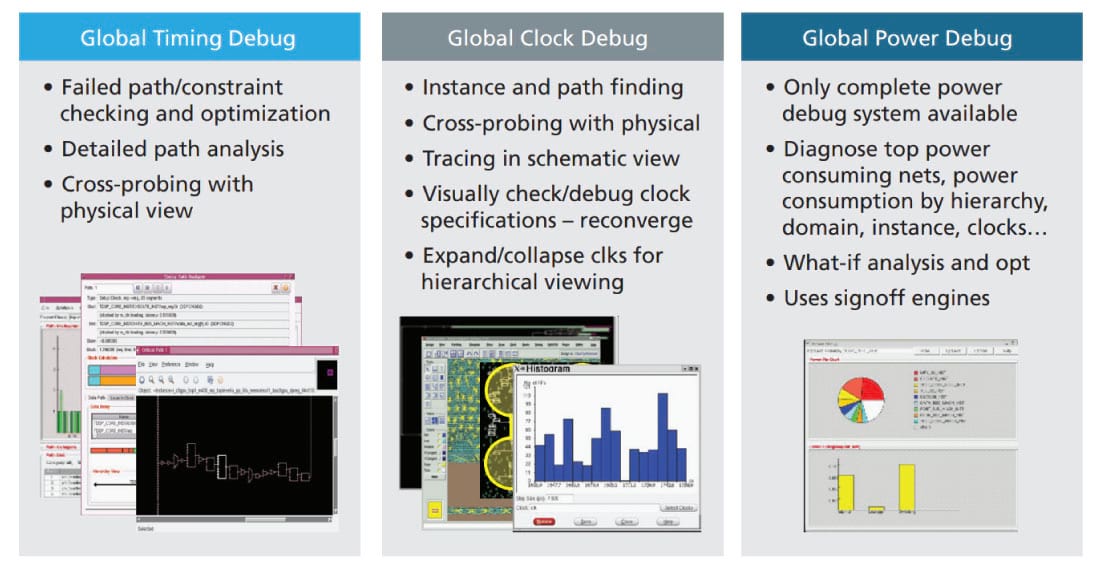

Fast and easy debug and analysis

The ability to debug and diagnose interdependent design closure issues is critical. The challenges often come late in the design cycle, along the critical path to final tapeout. First Encounter capabilities for timing, power, and clock debug and diagnostics enable you to quickly pinpoint and visualize interdependent timing, clock, and power issues, and then quickly resolve them using powerful “what-if” analysis techniques. You can implement the results immediately in the physical design.

Low-power design

Advanced low-power design techniques such as power gating (MTCMOS) and dynamic voltage and frequency scaling (DVFS) use multiple power domains. The underlying First Encounter infrastructure facilitates the implementation of low-power designs because it comprehends multiple power domain structures across the flow. This capability enables automatic placement of level shifters, with all power connections completed automatically. First Encounter technology also supports Common Power Format (CPF) and IEEE 1801 to specify advanced power-reduction techniques, from design and verification through final implementation and signoff.

Concurrent chip/package design and flip-chip support

First Encounter flip-chip floorplanning technology enables the concurrent design of chip and package by including package constraints and parasitic effects while designing the IC. With support for multiple I/O methodologies, concurrent optimization of I/O and core instances, automatic RDL routing (including 45-degree support), and accounting for RDL routing during signal/power routing, First Encounter flip-chip technology eliminates the manual steps in I/O placement and optimization. This mature technology has been proven through multiple customer tapeouts.