Datasheet

APLAC Circuit Simulation Technology

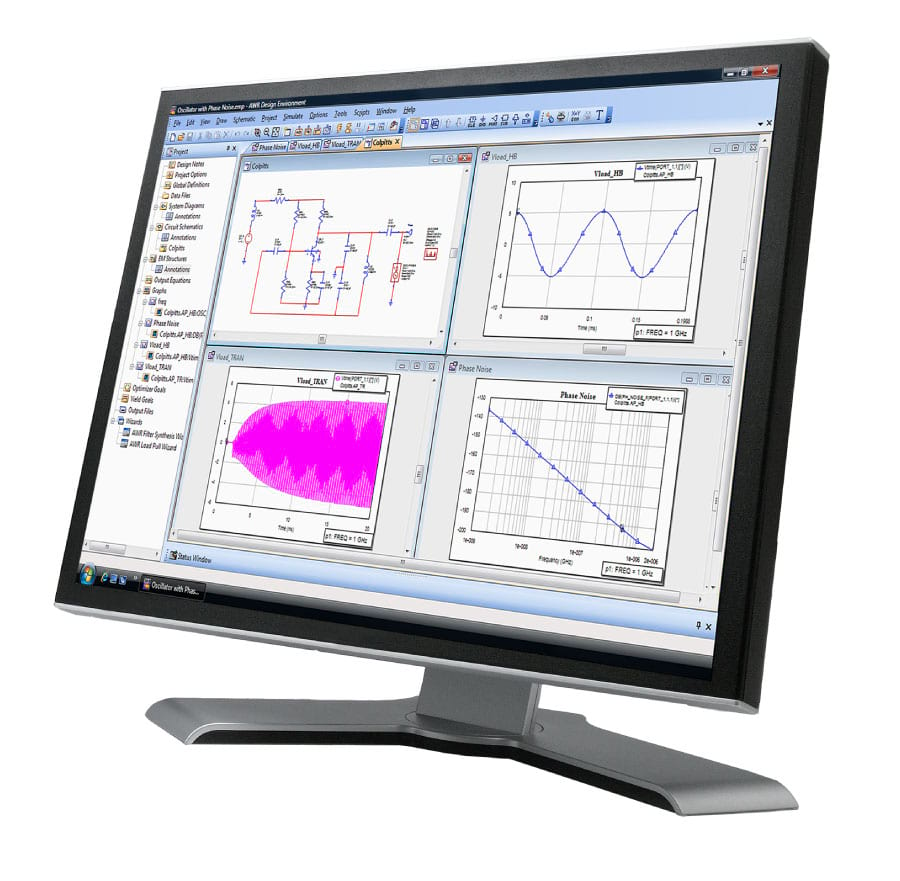

Cadence APLAC high-frequency circuit simulation technology brings the benefits of harmonic balance (HB) analysis to the design of complex, extremely nonlinear circuits. APLAC technology is used extensively for IC design at leading device manufacturers globally. The unique implementation of HB and transient analysis gives you extremely fast and exceptionally accurate results.

Overview

What is APLAC?

Multi-domain analysis

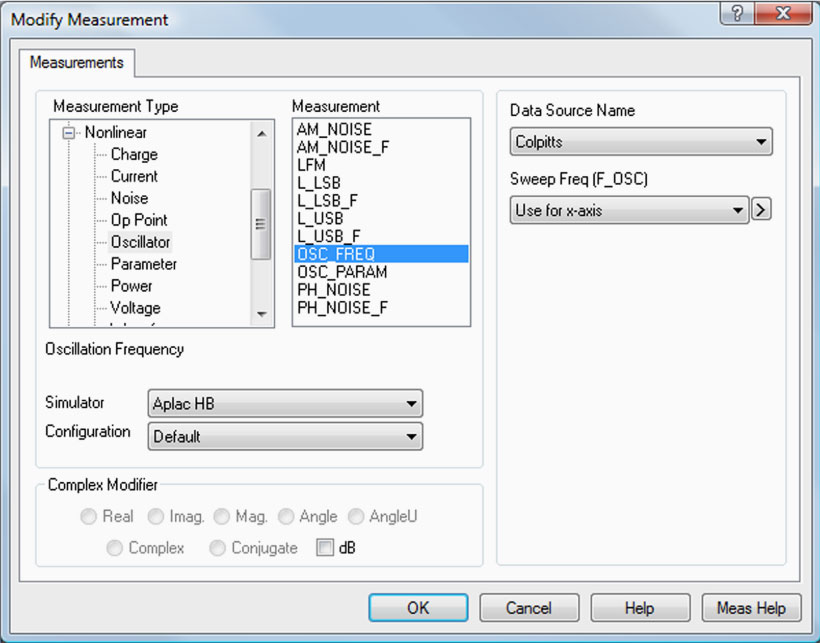

APLAC multi-domain analysis enables the simulation of any RF or analog circuit with a selection of analysis methods, including DC operation point, linear frequency domain, time domain, HB, phase noise, linear/nonlinear noise, and accurate yield predictions. Each circuit can be analyzed in multiple ways simply by altering the analysis definitions. Optimization, tuning, and a Monte Carlo statistical feature (for design yield) are available with every method. APLAC HB and time-domain solvers can be driven from the same schematic, with the same sources, and the same models.

High-Capacity HB and Time-Domain Simulators

The APLAC HB algorithm minimizes memory requirements and simulation time while maintaining a high degree of accuracy. APLAC technology embodies multiple HB engines, including an enhanced HB method, a TAHB method, and an MRHB method. The enhanced HB method enables the simulation of larger circuits faster than traditional microwave HB techniques. TAHB is for digital divider circuits and accurate nonlinear phase noise measurements for analog and RF applications. MRHB is a reformulation of the basic HB technique. It identifies the harmonic needs of the individual nonlinear components or signal paths and reduces the harmonic solution matrix accordingly. The overall effect is several orders of magnitude reduction in memory requirements by solving only the required harmonics for each component or signal path.