Datasheet

Allegro X Advanced Package Designer Silicon Layout Option

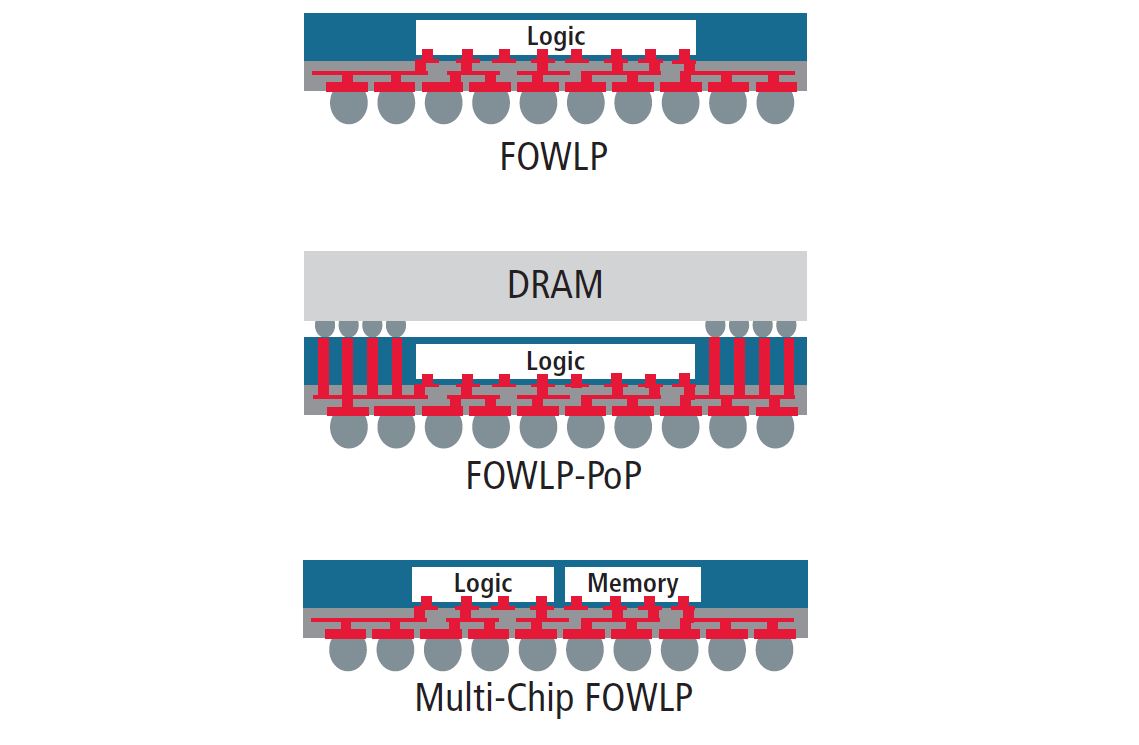

Fan-out wafer-level package (FOWLP) design places new demands on the IC backend and package substrate design teams and the design tools and flows that they use. The Cadence Allegro X Advanced Package Designer Silicon Layout Option provides a complete design and verification flow for the specific design and manufacturing challenges of FOWLP designs.

Overview

Overview

While wafer-level packaging (WLP) is not a new technology or process, as with all technologies, it evolves. In its latest evolution as foundry-driven FOWLP, it provides a number of new advantages for the handheld/mobile/ wireless/multimedia product market segment.

FOWLP technology, based on wafer molding and fine metal processes without substrate, enables the reduced thickness, optimized performance, and lower cost ideal for its initial target market, mobile computing products such as smartphones and tablets. Such devices are evolving at a rapid pace as faster and more powerful multi-core application processors become available. FOWLP enables a thinner PoP stack with better routing density, higher operating frequency (fMAX), higher memory bandwidth DRAM, and better heat dissipation than conventional chip-scale packaging methodologies.

Silicon Layout Option

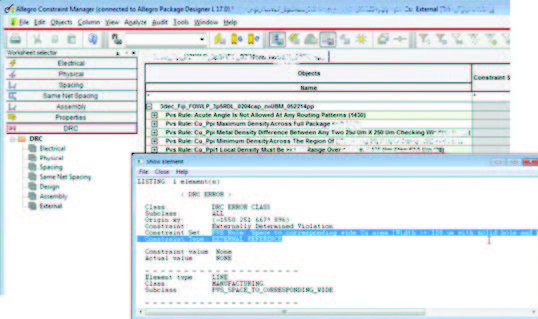

The majority of these emerging FOWLP designs may fall under the responsibility of the IC back-end design teams of the fabless semiconductor company. However, these designs may also place demands on the IC package substrate designer/teams. The IC packaging design tools must be extended to support the requirements of modern FOWLP designs. Through working with leaders in this emerging segment, Cadence has been able to develop the Silicon Layout Option, which provides a complete design through verification flow for the specific design and manufacturing challenges of FOWLP.

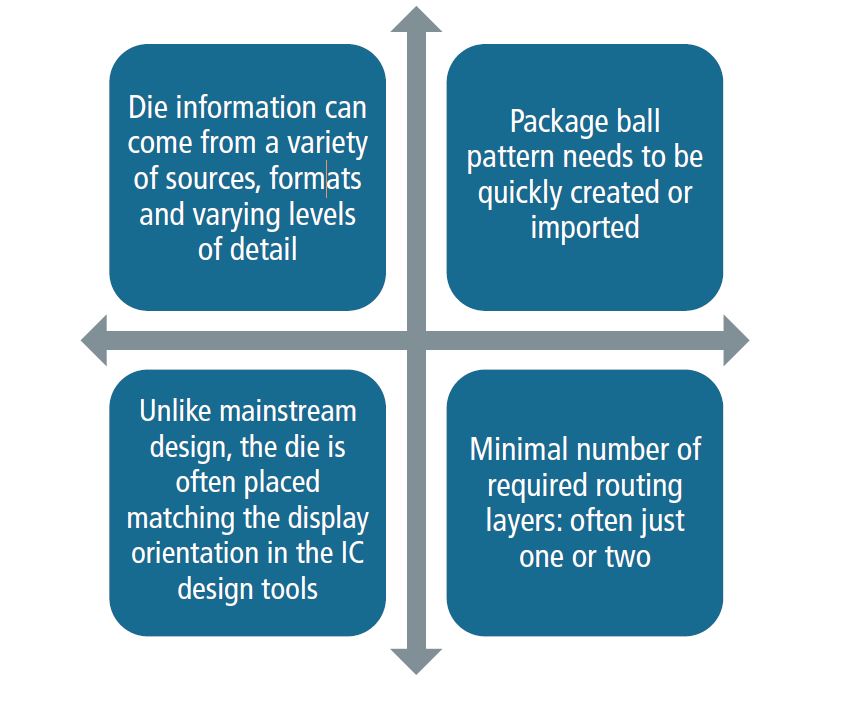

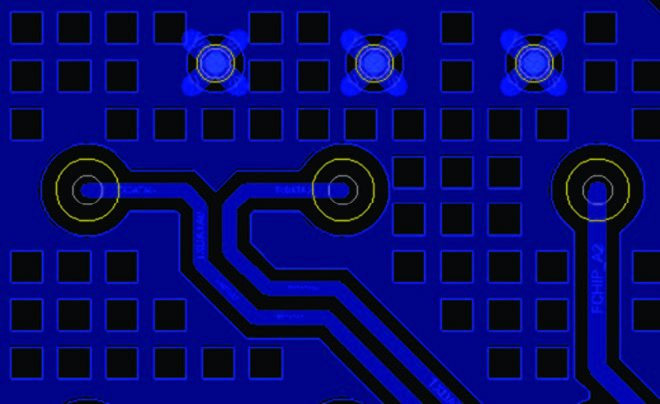

As the Silicon Layout Option uses a wafer-level implementation and process, the path to manufacturing is radically different from that of a typical organic substrate-based IC package manufacturing process. For the Silicon Layout Option, the manufacturing process is the same as, or very similar to, an IC manufacturing process. At the macro level, the differences and challenges from traditional organic IC package manufacture include:

Features

The Silicon Layout Option in conjunction with the Cadence Physical Verification System (PVS) enables designers to address these macro-level items. Some of the features specific to the Silicon Layout Option are:

Platforms

The Allegro X Advanced Package Designer Silicon Layout Option is available with Allegro X Advanced Package Designer and is designed to be used in conjunction with the Cadence PVS, which must be purchased separately. The Silicon Layout Option is available in these versions: