Brochure

Design IP for USB 2.0 OTG Controller

Overview

Overview

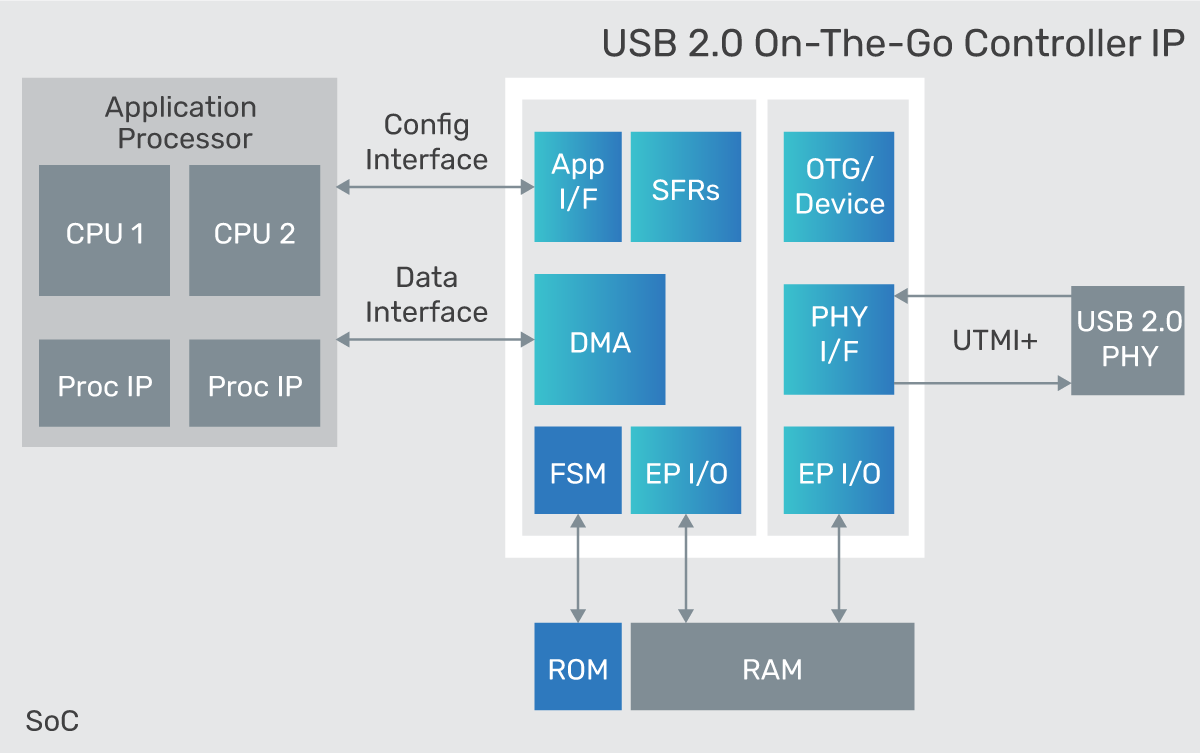

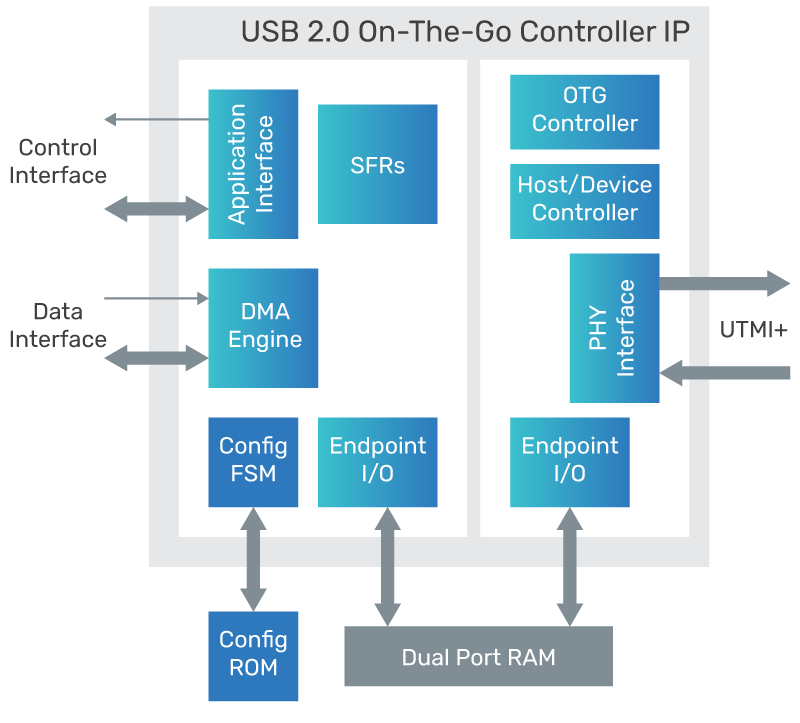

Certified for compliance with Universal Serial Bus Specification, Revision 2.0 and On-The-Go and Embedded Host Supplement to the USB Specification Revision 2.0, the Cadence Design IP for USB 2.0 On-The-Go (OTG) Controller operates dynamically as either a Device or embedded Host controller. The PHY interface complies with UTMI+ Specification, Revision 1.0.

The Controller IP, made for one of the most ubiquitous interfaces in electronics commonly used in consumer products, phones, and computers, is architected to quickly and easily integrate into any system on chip (SoC), and to connect seamlessly to a Cadence or third-party, UTMIcompliant PHY. Both configuration and data interfaces of the controller are compatible with industry-standard Arm AMBA AXI interfaces.

The Controller IP is delivered with a low-level driver to ease integration into the target application. Controller IP supports all available USB 2.0 classes.

The Controller IP is silicon-proven, and has been extensively validated with multiple hardware platforms.

Benefits

Key Features

Product Details

The Controller IP handles data transfer autonomously, and bridges the USB interface to a simple read/write parallel interface.

The Controller IP supports a DMA interface to optimize controller operation for your specific application.

OTG Controller

The Controller IP implements On-The-Go and Embedded Host functionality as defined in the USB 2.0 OTG supplement. Special Function Registers provide control of the Host Negotiation and Session Request protocols.

Embedded Host Controller

The Embedded Host Controller implements the USB 2.0 protocol for host devices, which includes initiation of data transactions on the USB, suspend and resume signaling, and USB reset signaling, and host-interrupt generation. In addition, the Embedded Host Controller automatically generates SOF tokens for frame and microframe timing, and device keepawake functions.

PHY Interface

The Controller IP connects to the PHY through an 8-bit UTMI+ interface

Application Interface

The Controller IP supports the AXI interface for configuration and data access. Access to the DMA engine is realized through a responder FIFO interface. The DMA engine features an AMBA AXI interface.