Brochure

Controller IP for NAND Flash

Overview

Overview

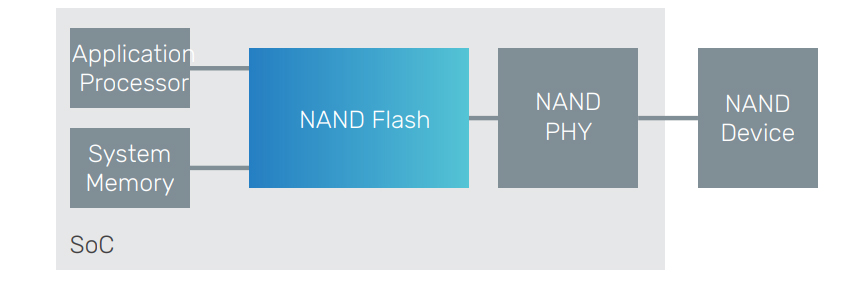

NAND Flash memory is widely used for data storage in computers and multiple consumer and enterprise applications. It is the basic building block for SSD applications, as well as USB drives, SD cards, etc. NAND Flash requires special handling and management, including error detection and correction, and the Cadence Controller IP for NAND Flash deals with those complexities, enabling our customers to create simple and quick system-on-chip (SoC) designs.

The Controller IP for NAND Flash provides the logic required to support ONFi 4.0/4.1-compliant memory in any SoC.

Supporting ONFI 4.x (excluding EZ-NAND), ONFI 3.x, ONFI 2.x., and Toggle Mode DDR-1/2 NAND Flash devices, the Controller IP for NAND Flash has many configurable features and input parameters to customize the controller for the specific needs of any application.

The Controller IP for NAND Flash is architected to quickly and easily integrate into any SoC through the industry-standard Arm AMBA 4 AXI protocol as a high-speed initiator interface and the AMBA APB and AXI-Lite protocols as register interfaces.

The Controller IP for NAND Flash is part of the comprehensive Cadence Design IP portfolio comprised of Interface, Memory, Analog, System, and Peripheral IP.

Benefits

Controller Core

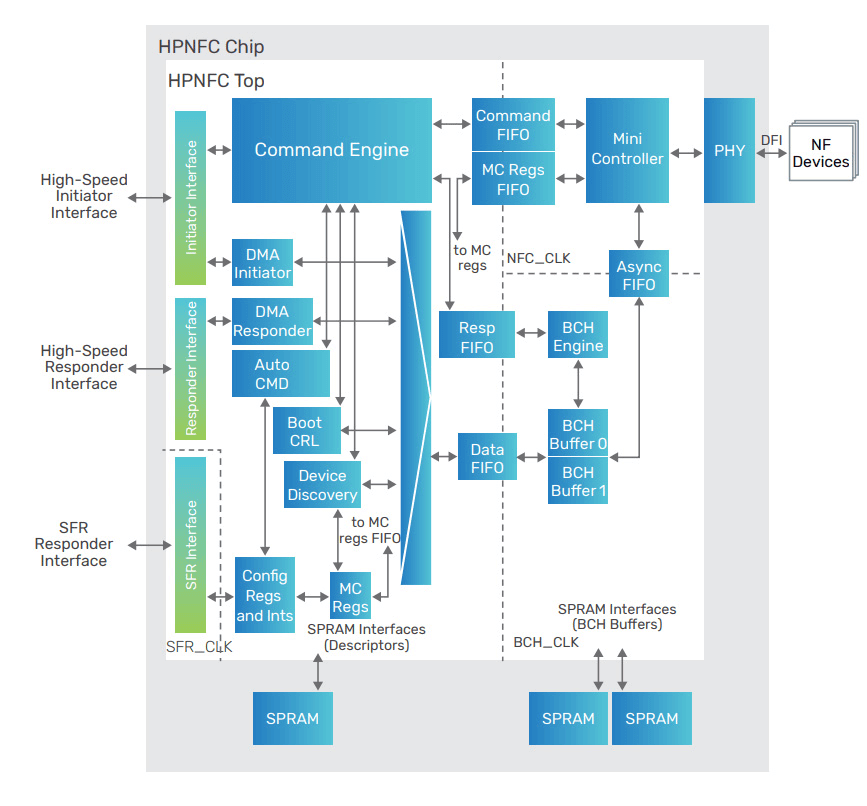

The controller core handles all command sequencing and flash memory device interactions, allowing intelligent hardware abstraction.

Initiator DMA Interface

The command and data DMA engines speed up data transfer between a device on the system bus and the NAND Flash memory, as well as decrease the CPU load.

Key Features

BCH Error Correction

The Controller IP for NAND Flash supports configurable BCH implementation. The BCH engine can be configured to support error correction up to 128 bits as well as support error correction across customer-defined sub-page sizes. The BCH mechanism can be configured to support multiple error correction strength and up to two subpage sizes.

Internal FIFO

Configurable, asynchronous FIFO is used for synchronizing clock domains within the Controller IP for NAND Flash, allowing the controller core and bus interfaces to operate independently of any connected NAND Flash devices.

Cadence NAND

Driver Cadence offers the NAND Flash Controller Software Driver, aC source code driver and testbench designed to work natively with the Controller IP for NAND Flash to offload hardware management from higher level applications.

Control Interface

The control interface provides access to the configuration and status registers in the Controller IP for NAND Flash.