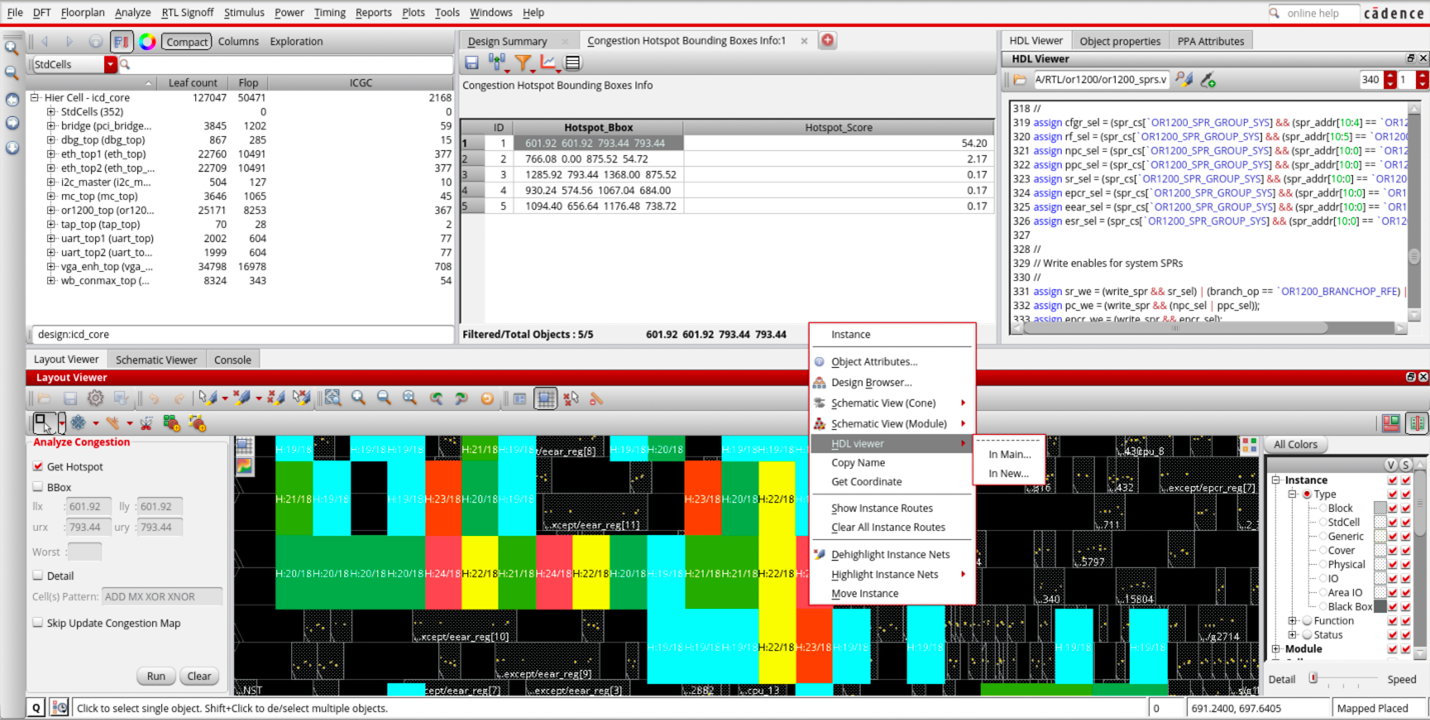

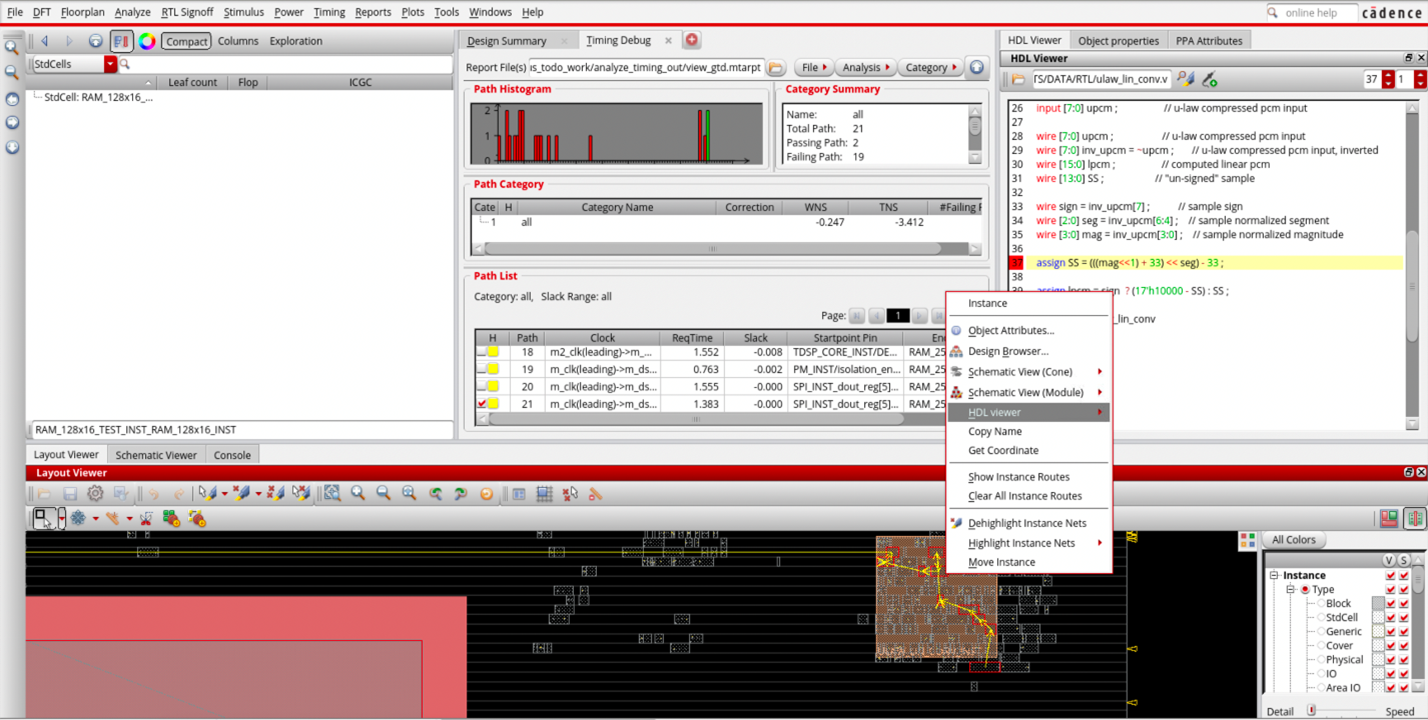

Cadence® Joules™ RTL Design Studioにより、RTL設計者は、電力、パフォーマンス、エリア、混雑 (PPAC)のフィジカル設計への影響を、早期かつ精度の高い洞察を迅速に得ることができます。フロントエンド設計者は、設計レイアウト内で発生する問題を特定し、ソースコードまで追跡し、より良いPPAC達成に向けて、RTLを改善するための実用的なガイダンスを自動的に提供できます。同時に、インプリメンテーション設計者は、この早期デバッグの恩恵により、RTLレベルでは修正できない問題の対応にリソースを割り当てることができます。

概要

Cadence® Joules™ RTL Design Studio allows RTL designers to rapidly get early and accurate insight into the physical design effects of power, performance, area, and congestion (PPAC). Front-end designers can locate problems in the design layout, trace them to the source code, and automatically give actionable guidance to improve RTL for better PPAC. Simultaneously, implementation engineers benefit from this early debugging because they can now allocate resources to fix issues that cannot be fixed at the RTL level.

以前は、RTL設計はインプリメンテーション設計者からは孤立しており、フロントエンドとバックエンドの間は遮断されていました。この遮断により、2つのチーム間で余分なやり取りが発生し、設計サイクルが延長され、市場投入までの時間が大幅に遅れる事態も発生していました。効果的なフィジカル実装を実現するためには、主要なタイミングと混雑の問題をハンドオフ前に解決する必要があります。精度の高い見積もりとインテリジェントなデバッグが早期に利用可能であれば、RTLコーディングとアーキテクチャにおけるフィジカル実装の課題の20%-40%を解決することができます。

Joules RTL Design Studioは、ソースコードのハンドオフが完全に最適化され、フロントエンド設計者のPPA目標達成を確実なものにします。このソリューションのPPAC見積もりは、業界をリードするケイデンスの Innovus™ Implementation System, Genus™ Synthesis Solution, そして Joules RTL Power Solutionのコアエンジンによって駆動されるため、ユーザの設計を行う上での決定の正確性を信頼できます。独自のインテリジェントなデバッグアシスタントシステムは、Joules RTL Design Studioを際立たせます. このエキスパートシステムは、違反の考えられる原因を優先順位付けし、追加の洞察により、設計者がRTL問題に対処する方法を理解できるようになり、よりスマートで効率的な製品の実現につながります。

Joules RTL Design Studioは、生成AIソリューションであるCadence Cerebrus™ Intelligent Chip Explorer, と緊密に統合されており、フロアプランの最適化や周波数と電圧のトレードオフ等の設計空間のシナリオを検討できます。さらに、 Cadence Joint Enterprise Data and AI Platform の統合により、異なるバージョンのRTLまたは過去のプロジェクト世代間の傾向や洞察の分析が可能になります。

OS Platform Support

Joules RTL Design Studio supports:

ケイデンスのサービスとサポート

参考

- Vanderlip, Jeff. "Physical RTL optimization solves problems early." EETimes DesignLines. November 15, 2002.