System Verification Scoreboard

Contact Us

Introduction

With the rapid evolution of chip design and verification, the system-on-chip (SoC) contains multiple processors with caches and cache-coherent agents beyond the multi-processor clusters. Cache coherency, long regarded as one of the most complex verification challenges due to the address changes and data transformations happening in the SoC, requires an advanced and highly automated approach at the SoC level.

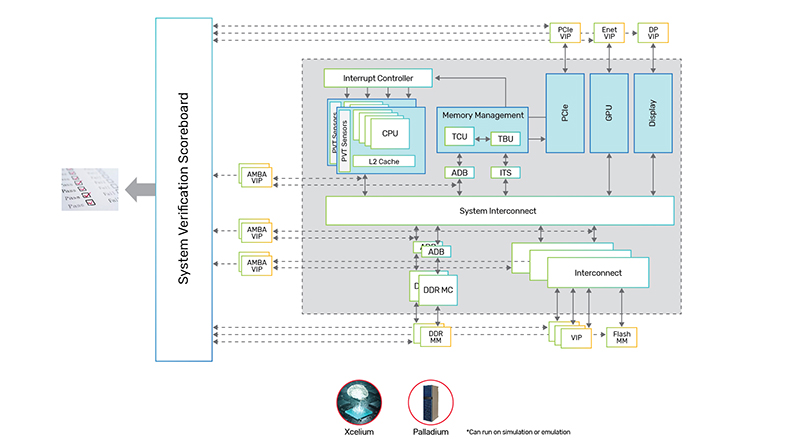

The System Verification Scoreboard enables the user to verify the data integrity of the system flows at the different levels of the SoC. The System Verification Scoreboard works in conjunction with Verification IP (VIP) that verify that each data flow strictly adheres to the given communication protocol. The System Verification Scoreboard checks for the proper functionality of coherent systems, flagging out all violations of coherency. The System Verification Scoreboard is a flexible system-level scoreboard that can be extended to verify any design specific functionality. The System Verification Scoreboard supports both real-time simulation as well as post-processing modes used in simulation and emulation environments, thus making it an ideal scoreboarding tool in any functional verification or performance validation tasks.

Use Flow

The System Verification Scoreboard provides data and cache coherency checkers, which allow users to check data consistency across the system, supporting both simulation and emulation flows. The automated scoreboard supports coherent interconnects, memories, and peripherals and is integrated with Cadence® VIP and AVIP. The System Verification Scoreboard can be used for the full SoC, interconnect, or subsystems in both simulation or emulation platforms.

Main Capabilities

The main System Verification Scoreboard features and capabilities include:

- Out-of-the-box support of coherent, non-coherent, and cascading interconnects

- Provides API allowing connection of customer proprietary VIP and/or bus monitors

- Seamlessly runs on Cadence Palladium® Z1, Xcelium™, and third-party simulators

- Supports any number of ingress, egress, and intermediate interfaces

- Supports all data transformations within and across protocol boundaries including splitting, upsizing, and downsizing

- Supports system-level "L3" cache (SLC)

- Supports Distributed Virtual Memory (DVM) transactions

- Enables user's extension for any design-specific checks

For further details, please contact our Cadence System Verification Scoreboard experts.