ケイデンスのデジタル設計フルフロー、マシンラーニングを活用し、 QoR改善、設計スループット最大3倍高速化の実現に向け最適化

Yokohama, 18 Mar 2020

要旨:

- 配置処理および物理設計最適化エンジンを一つの環境に統合した実績あるフロー。16nmから5nmさらにそれ以下のプロセスノードにおいても数百件ものテープアウトを完了

- 業界で初めてマシンラーニング機能を統合した物理設計最適化エンジン。従来のフローとの比較でPPAをさらに最大20%向上

- タイミングおよび電圧降下 (IR drop) に関するサインオフエンジンを備えた唯一のデジタル設計フルフロー。サインオフに向けてこれまでにない高い設計収束性をユーザーに提供

ケイデンス・デザイン・システムズ社(本社:米国カリフォルニア州サンノゼ市、以下、ケイデンス)は、3月17日(米国現地時間) 、先端プロセスノードで数百件ものテープアウト実績を持つケイデンスのデジタル設計フルフローの新バージョンリリースにおいて、車載、モバイル、ネットワーク、ハイパフォーマンスコンピューティング、人工知能 (AI) をはじめとする各種アプリケーションに向けたPPA (Power, Performance, Area) 最適化が強化されたことを発表しました。新しいフローには、配置処理および物理設計最適化の統合エンジンに加え、マシンラーニング (ML) 機能をはじめとする業界初の機能が複数搭載されており、設計スループットを最大3倍高速化するとともにPPAを最大20%向上し、卓越した設計を可能にします。

ケイデンスのデジタル設計フルフローの詳細については、www.cadence.com/go/digitalをご参照ください。

新しいケイデンスのデジタル設計フルフローは、以下の機能強化によりPPAおよび設計スループットを向上します。

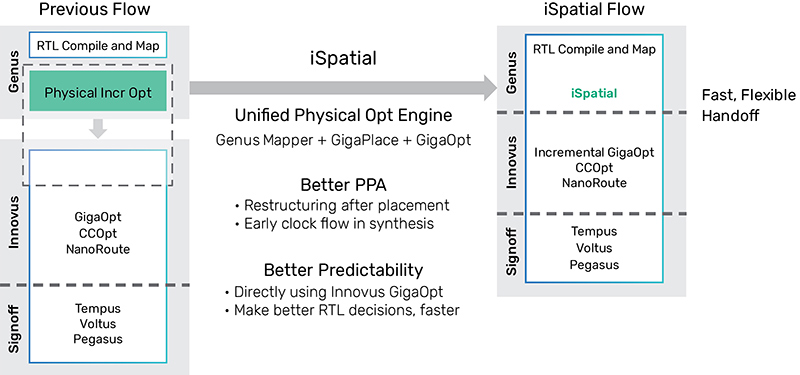

- デジタル設計フルフローを強化するiSpatialテクノロジ: iSpatialテクノロジはInnovus™ Implementation Systemに搭載されているGigaPlace™ Placement EngineおよびGigaOpt™ OptimizerをGenus™ Synthesis Solutionに統合。最適な配線レイヤー割り当て、クロックスキューおよびビアピラーなどのテクノロジをサポート。iSpatialテクノロジでは共通のユーザーインターフェイスおよびデータベースを使用しており、Genus Physical Synthesis環境およびInnovus Implementation System環境の統合により、シームレスな処理フローを実現

- マシンラーニング機能: マシンラーニング機能で既存デザインのトレーニングを行い、iSpatial最適化テクノロジを強化。従来の配置配線フローとの比較で設計マージンを最小限に抑えることが可能

- 最適なサインオフ収束: デジタル設計フルフローは、インプリメンテーション、タイミングおよび電圧降下(IR drop)に関するサインオフエンジンを統合し、フィジカル、タイミング、信頼性の目標すべてに対してデザインを同時に収束させることにより、最適なサインオフでの収束を実現。また、設計マージンを削減し、イタレーションを減らすことが可能

MediaTek社コメント

Dr. SA Hwang氏 (General manager of Computing and Artificial Intelligence Technology Group):

「厳しいパフォーマンス目標を満たすために、我々は高性能コアの設計チューニングにかなりの労力を費やしてきました。Innovus Implementation SystemのGigaOpt Optimizerに搭載された新しいマシンラーニング機能を使用することにより、CPUコアモデルのトレーニングを自動的かつ迅速に行い、最大周波数を向上するとともにマイナスのスラック値の総計を80%低減することができました。その結果、最終サインオフデザインクロージャーまでの期間が半分に短縮されました。」

Samsung Electronics社コメント

Jaehong Park氏 (Executive vice president of Foundry Design Platform Development):

「iSpatialテクノロジを搭載したケイデンスのデジタル設計フルフローでは、配置最適化においてPPAを高精度に予測してくれるので、RTL、制約作成、フロアプラン間でのイタレーションが削減され、総消費電力を6%低減すると同時にデザインの開発を1/3の期間で達成することができました。さらに、ケイデンス独自のマシンラーニング機能により、Samsung Foundryの4nm EUV ノードでのデザインのモデルに対するトレーニングを行った結果、さらにパフォーマンスを5%向上し、リーク電流を5%低減することができました。」

ケイデンス コメント

Dr. Chin-Chi Teng (Senior vice president and general manager of the Digital & Signoff Group):

「新しいデジタル設計フルフローは、市場で幅広く採用されている統合フローの上に構築されており、ケイデンスのデジタルおよびサインオフ設計におけるリーダーの地位をさらに高め、卓越したSoC設計を可能にする環境をお客様に提供します。我々は、ますます大規模化するデザインに加え、厳しいスケジュールを達成する必要があるお客様と緊密に協業し、さらに効率よくPPA向上を実現するために必要な機能を提供していきます。」

ケイデンスのデジタル設計フルフローは、Innovus Implementation System、Genus Synthesis Solution、Tempus™ Timing Signoff Solution、Voltus™ IC Power Integrity Solutionで構成されています。本フローは、デザインクロージャーへの最速パス、予測可能性をお客様に提供し、ケイデンスのIntelligent System Design™戦略を支え、卓越したシステムオンチップ (SoC) 設計を可能にします。

お問合せ