Cadence Verification Suite Enabled on Arm-Based HPC Datacenters

Providing a new level of flexibility to complete complex verification projects in the electronics industry

Key Benefits

- Improves semiconductor product quality and reliability with the capacity to run additional verification workloads within available project timeframes

- Maximizes limited IT budgets by deploying a compute option HPE indicates is up to 19% more cost-effective than other HPE servers

- Delivers improved farm utilization and better engineering productivity

Verifying that system-on-chip (SoC) designs function correctly prior to manufacturing is a massive task requiring high-performance computing (HPC). Engineers have multiple means to address this problem because verifying every state isn’t reasonable, but the most pervasive technology underlying these approaches is logic simulation.

Accounting for over 70% of the EDA compute workload, SoC verification is a key driver for growth and transformation of the datacenter. Datacenters need compute-dense platforms optimized for improved performance for a variety of different workloads that can be deployed and managed as cost effectively as possible. Datacenters that include Arm®-based servers can leverage tens of thousands of multi-core CPUs to execute massive numbers of HPC workloads, such as those needed to verify SoCs for mobile, IoT, cloud, 5G, and other applications.

An Ecosystem of Companies Solving your Compute Needs for SoC Verification

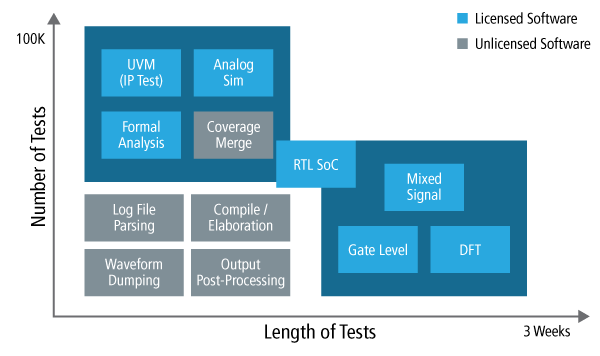

Cadence has been working with Arm, HPE, Marvell, and others to solve the compute needs of SoC verification on Arm-based server datacenters. Verification jobs generally fall into two classes. The first is short tests that are used to verify IP blocks. These tend to run easily on one core and address a fraction of the server memory, which means each core in a server can run one of the jobs and get high throughput. The other class is huge jobs that run for hours to weeks and take most or all of the memory on a server. For these jobs, they either run on a single core and consume the entire memory of the server or, with Cadence® Xcelium™ multi-core simulation, the job can be distributed across multiple cores so it runs faster. Beyond that, there are many other verification workloads that are unlicensed or not license limited including compile/elaboration, coverage merging, output post-processing and more. Each of these also require compute capacity in the datacenter.

Applying Xcelium Simulation and Arm Servers

A comprehensive verification suite running natively on Arm-based servers further extends the computational benefits by more efficiently executing both high-throughput and high-capacity workloads to reduce overall SoC verification time and costs.

The Xcelium simulation provides both a faster single-core engine, to speed up each workload in the high-throughput test group, and a multi-core engine, to reduce the runtime of long-latency workloads. As a result, Xcelium simulation is ideally suited to the high core count typical of Arm-based servers. For high-throughput tests, the high core count means that projects can run more tests in parallel on a given set of servers, so project teams can achieve better overall SoC quality and faster turnaround time to quality bug fixes. For high-capacity tests, Xcelium simulation can scale to all the cores available on a server, resulting in faster regression cycle time in the critical final days and weeks of a project cycle

By porting EDA tools to Arm-based servers, Cadence is providing the electronics industry with the tooling that can exploit innovative HPC servers to speed the verification of their SoCs.

The Marvell ThunderX2 processor is the industry’s most widely adopted Arm server processor and delivers best-in-class compute performance and memory bandwidth so critical for EDA workdloads like the Cadence Verification Suite. Our partnership with Cadence and HPE demonstrates the value of driving ...

Gopal Hegde, vice president and general manager, Server Processor Business Unit at Marvell

HPE Apollo 70 Systems with the Marvell ThunderX2 Arm-based processor provide a new multi-core and high job-throughput hardware choice for the EDA market. We look forward to collaborating with Cadence to offer our joint EDA customers a leading HPC Arm-based solution, enabling them to run the Cadence Verification ...

Bill Mannel, vice president and general manager, HPC and AI, Hewlett Packard Enterprise

We are using Cadence Xcelium Parallel Logic Simulation on Arm-based production servers, and the additional support from Cadence Verification Suite technologies not only reduces development costs but enables the deployment of additional resources needed for more complete verification. The deployment of the Cadence ...

Drew Henry, senior vice president and general manager, Infrastructure Business Unit, Arm

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums