Sigrity Advanced SI

Accelerate signal integrity analysis for PCB and IC packaging designs

Key Benefits

- Reduces cost and time by identifying potential reflection and crosstalk problems early

- Supports leading-edge SI interfaces with statistical and time-and frequency-domain analysis of serial and parallel links from DC to >56GHz

To help you quickly implement general topologies and standard interfaces, Cadence® Sigrity™ Advanced SI technology performs automated die-to-die signal integrity (SI) analysis in multiple modes:

- Source-synchronous for parallel buses

- Serial links, with an emphasis on SerDes channels

- Free-form general-purpose topology exploration environment for signal, power, or combined what-if analysis

Covering the range DC to over 56GHz (112Gbps), our Advanced SI technology uses frequency domain, time domain, and statistical analysis methods.

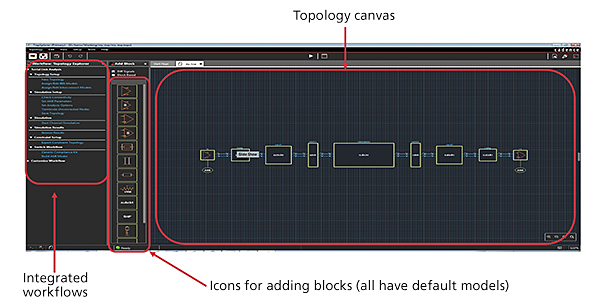

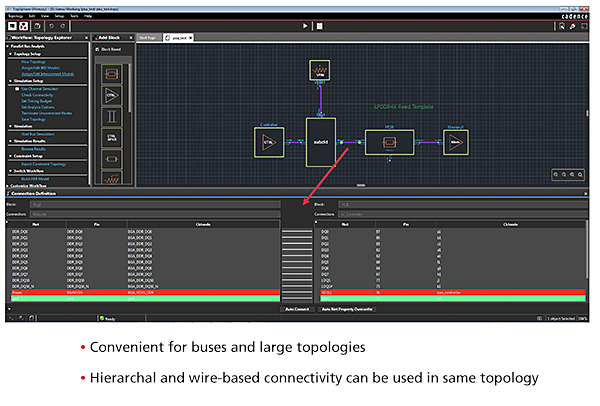

Sigrity Topology Explorer

This general-purpose topology exploration function is ideal for exploring end-to-end signal and power topologies, including letting you perform SI or transient power integrity (PI) analysis together. Also, you can include complex interconnect models and connect them to a single driver/receiver/discreet symbol that automatically replicates the circuit for each of the ports on the interconnect model. This functionality is included with Sigrity Aurora, where nets can be automatically extracted from a physical PCB or IC package design.

Sigrity SystemSI Parallel Bus Analysis

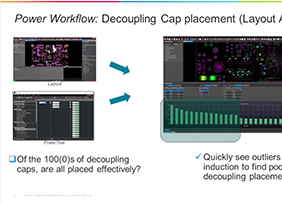

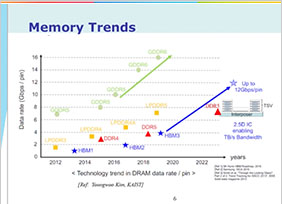

This end-to-end analysis targets source-synchronous parallel interfaces such as designs with DDRx memory. Pre-layout capabilities (including a via wizard) enable you to begin with models that are quickly generated and connected. As the design is refined, you can swap in more detailed models to reflect actual hardware design. Advanced SI includes the ability to:

- Create interconnect models for reflection analysis and crosstalk analysis

- Perform simultaneous switching noise (SSN) analysis, using finite-difference time-domain direct (FDTD-direct) that supports accurate SSN analysis without the use of S-parameters (you can import S-parameters using tools such as those included in Cadence Extraction Suites)

- Create SPICE models from S-parameters with Cadence Sigrity Broadband SPICE® utility, part of the Advanced SI technology

- Add equalization effects in both the read and write transmissions. IBIS-AMI models may be added, and channel simulation can be applied to run million-bit simulations to perform bit error rate (BER) simulations

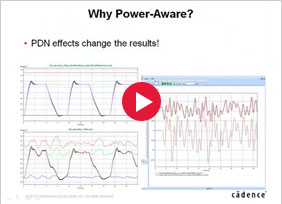

The concurrent simulation accounts for the effects of dielectric and conductor losses, reflections, inter-symbol interference (ISI), crosstalk, and SSN. These simulations can fully account for the effects of non-ideal power-delivery systems. Graphical outputs and post-processing options give insight for rapid system improvements.

Simulation results can be compared against common JEDEC standard requirements, such as DDR4 and DDR5, to ensure that the design meets the standard compliance requirements. If desired, additional tests can be configured to augment a compliance test or create a custom compliance kit for proprietary IP.

Sigrity SystemSI Serial Link Analysis

Make early assessments using basic templates with this award-winning chip-to-chip analysis that focuses on high-speed SerDes designs such as PCI Express® (PCIe®), HDMI, SFP+, Xaui, Infiniband, SAS, SATA, and USB. Industry-standard IBIS-AMI transmitter and receiver model support lets you perform simulations of channel behavior for serial links with chips from multiple suppliers. If you’re a chip model developer, you have access to techniques that assist in IBIS-AMI model development. You can add models of multiple packages, connectors, and boards to reflect the entire channel. Simulations identify crosstalk issues and show the effectiveness of chip-level clock and data recovery (CDR) techniques. Full-channel simulations, including millions of bits of data, confirm overall BER to determine if jitter and noise levels are within specified tolerances. You can get compliance kits for popular interfaces (i.e., PCIe 5.0) to automate the required signal quality checks. You can also configure a custom compliance kit if it is not available for your preferred standard.

interconnect models through signal, power, and ground port connectivity

Features

- Accurate handling of non-ideal power delivery system influences on SI

- Concurrently evaluate SI effects such as losses, reflections, crosstalk, and simultaneous switching output (SSO)

- Support for industry-standard IBIS-AMI transmitter and receiver models enables simulations of channel behavior for serial links with chips from multiple suppliers

- Highly automated measurement and reporting capabilities

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.