Analog Defect

Key Benefits

- Quickly identify potential sources of device manufacturing defects

- Multiple fault injection methods to optimize the simulation resolution and performance

- Calculate the test program’s defect coverage based on simulation

- Choose the minimum set of tests to provide maximum fault coverage

- Supports different defect models (open, short, or bridge)

- Select defects based on criteria such as device type, parameter value, terminals, etc.

- Correct-by-construction fault identification

- Defect detection based on the production test limits (range, >, etc.)

- Customizable measurement test based on preprocessing, calibration, etc.

Manufacturing testing is a critical step in the time-to-market of a product. Test costs make up a significant portion of the die recurring cost and is directly proportional to the time spent on the tester.

The Cadence® Legato™ Reliability Solution is built on Spectre® APS and the Virtuoso custom IC design platform for fast, easy adoption. You can quickly and easily analyze manufacturing tests before tapeout and improve test coverage to eliminate bad die before they become field failures. Integration of the Spectre and Virtuoso ADE Product Suite tools allows simulation of defects in the analog partition in a mixed-signal context, while also providing a unique and fast simulation tool to reduce simulation time for fault coverage analysis.

The Legato Reliability Solution supports layout-based fault analysis for signoff or schematic-based fault analysis for design for testability. Additionally, it provides coverage analysis to display the percentage of faults detected by the test program, test optimization to reduce test cost by minimizing the number of tests for maximum coverage, and simulation of faults in the analog partition in a mixed-signal context.

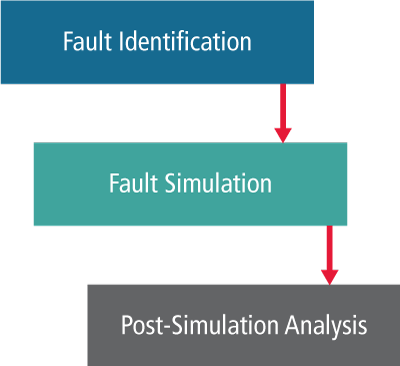

For post-simulation analysis, the Legato Reliability Solution supports two methods of failure detection, one based on the test limits and one based on comparison of fault results data and the golden data to evaluate the difference. In post-simulation fault detection, the faults get detected in Virtuoso ADE Assembler due to user-specified expressions and specification limits. The measurement can either be based on a single signal or can be built to cover multiple signals, depending upon the requirement.

With this one-of-a-kind solution, you can identify testability issues early in the design cycle to maximize test coverage and eliminate test escapes.