Datasheet

Sigrity OptimizePI

Cost-based power-delivery network design

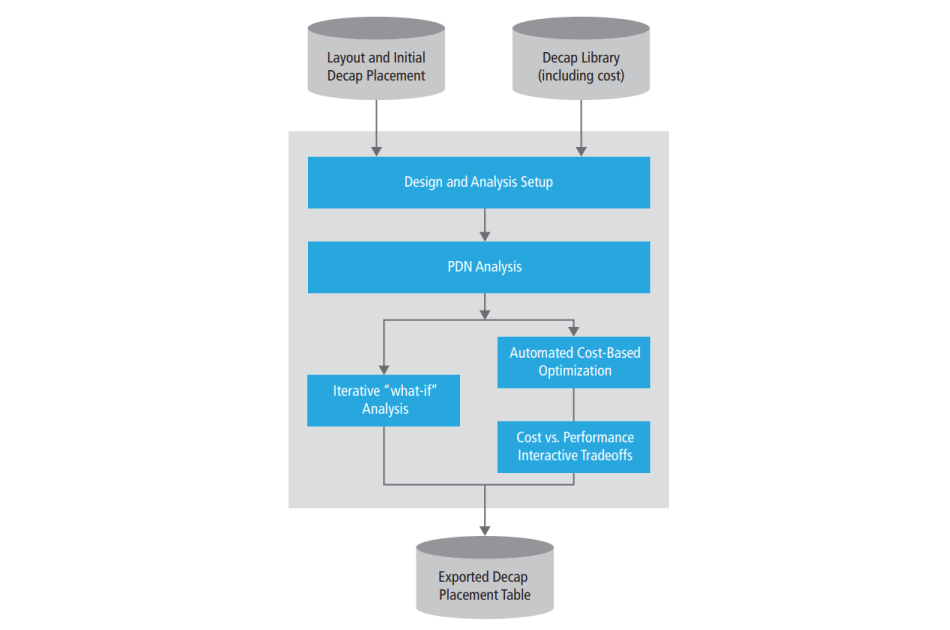

The Cadence Sigrity OptimizePI environment automates the selection and placement of decoupling capacitors (decaps) to assure products meet power-delivery network (PDN) performance targets at the lowest possible cost. The Sigrity OptimizePI approach may be applied to PCBs and IC packages, or a combination thereof. Cadence’s proprietary and proven Sigrity analysis technologies are augmented with an efficient optimization engine to uniquely enable cost-based PDN design. The Sigrity OptimizePI capabilities can fully explore the feasible design space and identify a range of candidate decap implementations, enabling users to pinpoint the ideal approach.

Overview

Benefits

Unprecedented Cost Savings

Eliminate decap over-design

Decap cost savings of 15% to 50% are typical with the Sigrity OptimizePI environment. Designs with a large number of decap components and those manufactured in volume benefit most. Cost savings are achieved by reducing the number of decaps placed and by targeting lower-priced components where practical. Device suppliers may suggest general guidelines such as “one decap per power pin” or describe preferred decap implementation schemes. Both approaches typically lead to an overly robust system. The Sigrity OptimizePI approach helps companies capitalize on this margin to gain market advantage.

Assure PDN performance

The Sigrity OptimizePI tool’s cost savings are achieved while analytically assuring PDN performance.

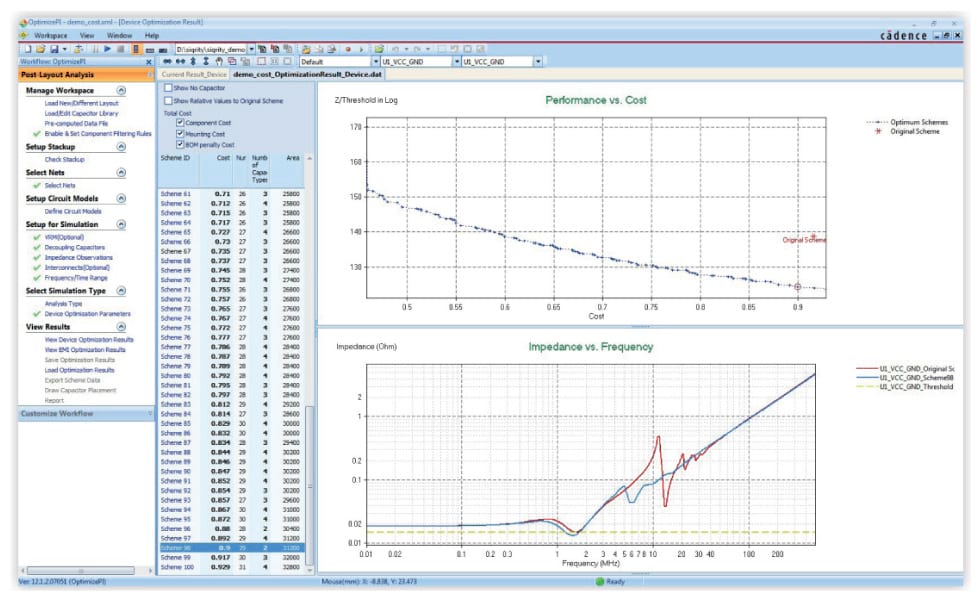

Alternatively, the Sigrity OptimizePI tool may be configured to maximize performance or reduce decap area without regard for cost. Complex interactions among performance, decap selection, component cost, and placement expense are considered. The Sigrity OptimizePI design schemes are the best-performing alternatives from all feasible designs. Analysis results are based on aggregate PDN performance averaged across frequency. Users can set device-specific targets and identify critical frequencies for further refinement. Time-domain results confirmation is also included.

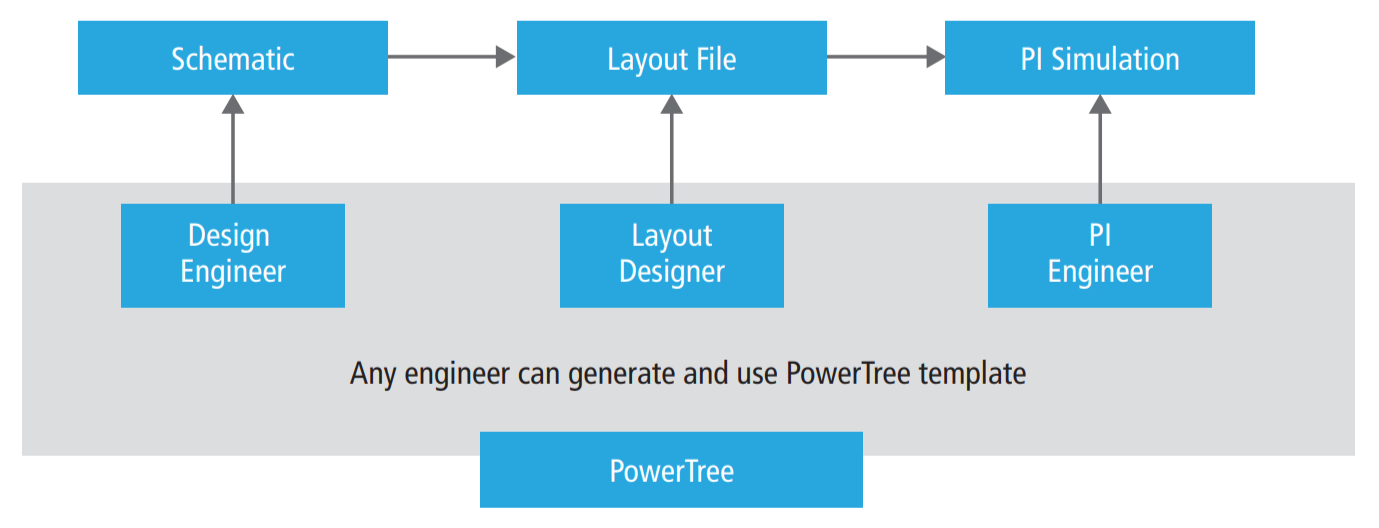

Use Model

While primarily targeting post-layout PDN optimization, pre-layout design scenarios can also be explored. This helps to eliminate decap over-design earlier in the design flow and supports development of analytically based decap placement design guides for individual devices. While the design is being implemented, PowerTree information, captured during the design’s logical design (schematic) stage, can be called on to simulate individual power rails as they are developed. Because the simulation set-up will be automated, either the layout designer or PI engineer can validate that target impedance constraints are being met as an in-design task. For post-layout applications, the Sigrity OptimizePI approach works from an initial design imported from a layout database. Sigrity OptimizePI capabilities can also be applied by manufacturing engineers for postproduction cost reduction. The optimized decoupling scheme can be automatically updated in Cadence PCB design tools.

Task-Focused Workflow

Setting up a design in the Sigrity OptimizePI environment typically requires less than 30 minutes of engineering time. Users are guided step by step through each task in the workflow. Initial set-up involves importing the PCB or IC package design and identification of an Sigrity OptimizePI library corresponding to a corporate decap preferred parts list. Decap component and placement costs are included in this library along with vendor-supplied electrical models. Set-up options enable decap selection filtering, biasing the importance of a device to overall PDN performance, and so on. Individual decap selections may be limited to a subset of the library or restricted by decap size. An interactive results window enables exploration of alternate design schemes. The Sigrity OptimizePI results can be exported to a spreadsheet for back annotation to the layout system.