Datasheet

Joules RTL Power Solution

Unified power calculator for accurate RTL power and signoff-quality gate power

Getting an accurate measure of RTL power consumption during design exploration has long been a major challenge for SoC design teams. Another challenge is getting consistent power through the design progress from RTL to P&R, because different tools are used at different stages of the design. System-level verification tools have the capacity to exercise real use cases but they are disconnected from the implementation tools that translate RTL to gates and wires. The Cadence Joules RTL Power Solution closes this gap by delivering timebased RTL power analysis with system-level runtimes and capacity, as well as high-quality estimates of gates and wires based on production implementation technology.

Overview

Overview

The Joules RTL Power Solution integrates seamlessly with the Cadence Palladium emulation platforms and the Stratus High-Level Synthesis (HLS) platform for early system-level power 2.0% analysis and optimization.

The Cadence Genus Synthesis Solution integrates the Joules solution for accurate power analysis and unrivaled dynamic power efficiency results

Key Features and Benefits

Ideal Power

The Joules solution’s Ideal Power feature is able to not only report the actual power of the design but, using deep analysis of the stimuli, can also report what the theoretical ideal power would be. This analysis can then be used by designers to improve the power efficiency of their RTL. Due to the integration with the Genus solution, the Joules solution is able to take into account the area and timing impacts of power efficiency opportunities, thereby saving precious schedule and designer bandwidth.

Replay Flow

Achieving power closure on advanced SoCs that integrate multiple IP over many advanced workloads can be a challenge. The Joules solution’s Replay Flow feature allows designers to integrate the result of multiple block-level changes with high accuracy—without forcing the whole system to be re-simulated. The system-level power analysis is incrementally updated with only the new module-level stimuli. Multiple functional scenarios can even be managed in one power view.

Multi-Threaded Frame-Based Architecture

Power analysis is parallelized across multiple CPUs, accelerating in-depth power exploration. Multiple stimulus files can be analyzed simultaneously and each stimulus file can be timesliced into frames to enable time-based power reporting.

Accurate RTL Power Estimation

The Joules solution performs an ultra-fast design synthesis using a new integrated prototype mode of the Genus solution, including physically aware clock tree and datapath buffering.

Single Power Calculator for Entire Design Flow

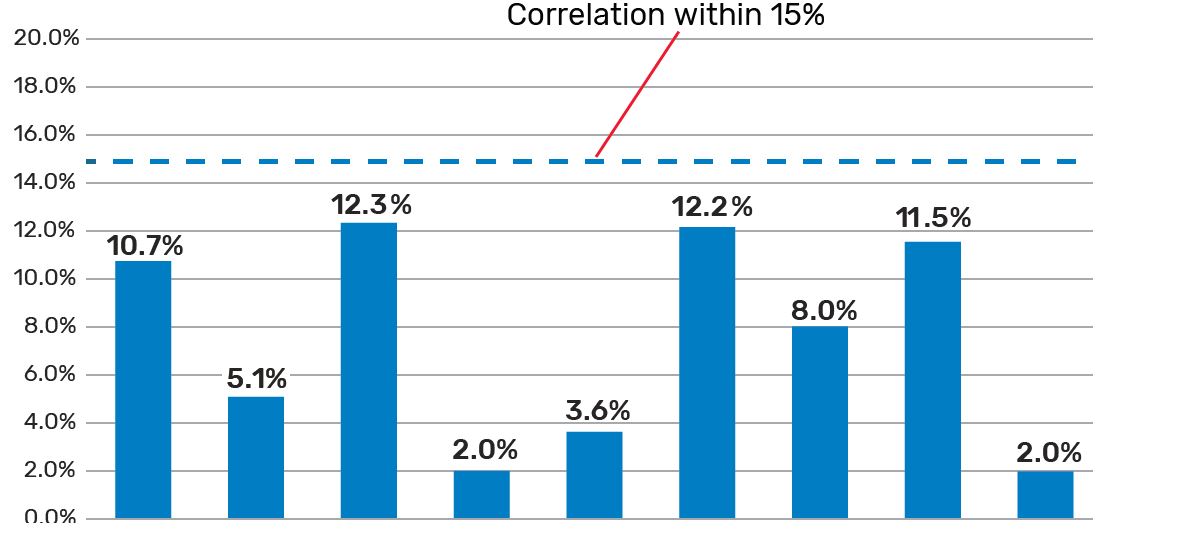

The Joules solution can also compute power accurately on a gate-level netlist and correlate to within 2-5% of signoff power.

Adjustable Power Analysis Resolution

Power-critical frames of a large system-level simulation can be zoomed in on with increasing resolution to identify the correct narrow time slice for IR drop and thermal signoff. Full gate-level-accurate SAIF or TCF can be exported for this identified narrow time slice only for use in power signoff.

Advanced Data Mining and Debug

Power can be reported at the bit level or register level, and can be categorized based on logic cell type, power category, design hierarchy, clock domain, power domain, or timing mode. A rich suite of library analysis tools is also included, which allows profiling of cells by drive strength versus area or delay or power.

Hardware-Accelerated System-Level Power Analysis

The Joules solution can be invoked directly from within the Palladium DPA solution GUI, where it can natively report time-based power waveforms.

SystemC-Level Power Analysis

The Stratus HLS platform is able to automatically leverage the Joules solution during high-level synthesis to provide SystemC-level power profiling and performance versus power tradeoff dashboarding.