Designers are actively involved in making a greener world for the future by pushing the boundaries of “low-power” enablement. Cadence is providing fast and accurate power analysis tools to enable new and revolutionary ideas on power reduction. The Cadence® Voltus™-XFi Custom Power Integrity Solution is a transistor-level electromigration and IR drop (EM-IR) tool that delivers foundry-supported SPICE-level accuracy for power integrity signoff.

Overview

Designers are actively involved in making a greener world for the future by pushing the boundaries of “low-power” enablement. Cadence is providing fast and accurate power analysis tools to enable new and revolutionary ideas on power reduction. The Cadence® Voltus™-XFi Custom Power Integrity Solution is a transistor-level electromigration and IR drop (EM-IR) tool that delivers foundry-supported SPICE-level accuracy for power integrity signoff.

Transistor-level EM-IR analysis presents unique challenges ranging from complex EM rules to the high cost of simulating large post-layout RC networks. Integrated with Cadence’s Quantus™ Extraction Solution, Spectre® X Simulator and Virtuoso® ADE Product Suite and Virtuoso Layout Suite, the Voltus-XFi solution delivers the productivity needed to reach aggressive time-to-market goals.

Benefits

Features

A central cockpit for EM-IR flow

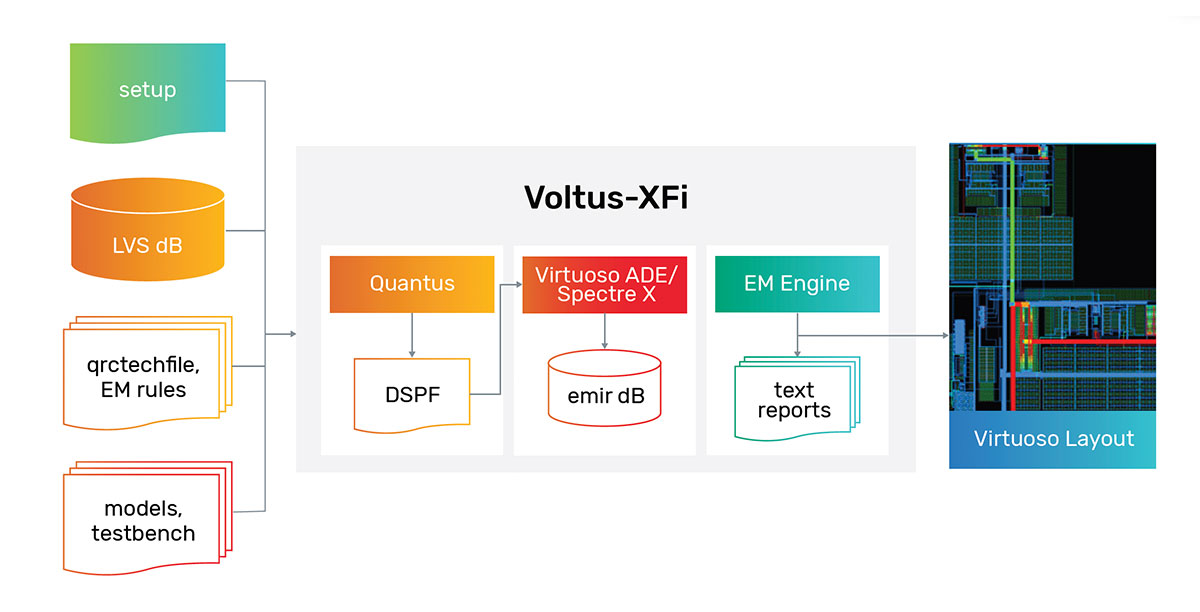

An EM-IR flow involves many different products, including extraction, design environment, circuit simulation, debugging, and layout viewing. Traditionally, designers must set up each tool and track/handle each product interaction individually, and there is no single place to check EM-IR flow consistency across all the tools. The Voltus-XFi solution solves these problems with a central EM-IR cockpit. It provides a unified setup for the flow by automatically deploying foundry-supported settings. Using the central cockpit, designers can set up and run Quantus extraction, perform EM-IR analysis on a generated or existing DSPF netlist using the Spectre simulator, and invoke and analyze results in Virtuoso Layout Suite (Figure 1).

Best-in-class use model with minimum tuning

The Spectre X and Voltus-XFi integration supports the accuracy, performance, and capacity that today’s advanced-node designs require. Like Spectre X, the Voltus-XFi solution balances an accuracy and performance tradeoff for custom IC, mixed-signal, and analog designs with a preset option. In addition, an enhanced method is used to provide a robust and accurate solution: the Spectre solver is used in the first stage, while the second stage uses a specialized RC network solver with Cadence-patented technology. The method can support larger designs and better performance than the direct method while maintaining Spectre trusted accuracy. For example, complex power-gated networks can be accurately modeled with power-gates switching during the analysis, unlike traditional approaches that model power-gates using as a constant on/off resistance.

Comprehensive debugging options

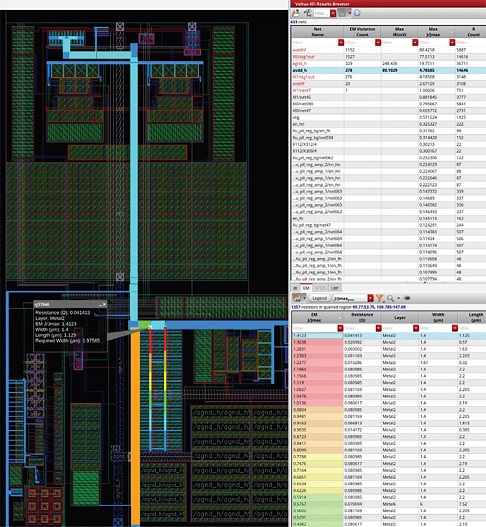

The Voltus-XFi solution has a built-in option to ensure that input data are EM-IR ready. An integrated EM-IR results browser (Figure 2) summarizes the EM-IR information and highlights violations, along with details on resistance value, metal layer, width, and length information. The EM-IR results are directly annotated in Virtuoso Layout and make it easy to identify and fix the problem area.

Full chip support with Voltus integration

The Voltus-XFi solution can generate a power-grid-view (PGV) macro model for the transistor block/IP being analyzed and pass this to the Voltus IC power integrity solution for full-chip signoff. A PGV macro model is a binary model that describes an IP’s grid characteristics. It contains geometric views, port information, current information, and multi-mode multi-corner (MMMC) features in capturing various operational modes, voltages, and clock frequencies. The Voltus-XFi solution generates the most accurate views, and the Voltus IC power integrity solution applies the correct view for full-chip signoff.