## SUCCESS STORY

1/20

# **cādence**°

## Toshiba and Cadence

Innovating Push-Pull RF PA Using AWR Software

MANAMANAN

Toshiba Research Europe Limited operates Toshiba's Cambridge Research Laboratory and the Telecommunications Research Laboratory in Bristol, UK. Since its inception in 1998, the Telecommunications Research Laboratory has been at the cutting edge of research into technologies such as next-generation wireless networking, reconfigurable device architectures, and "smart" systems for energy, mobile, and medical applications.

### Key Challenge

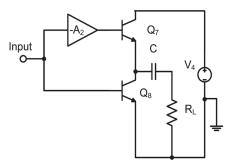

Wireless communications systems require RF power amplifiers (PAs) to overcome the transmission path loss that exists between transmitter and receiver. The PA offers a simple and convenient way to produce high transmit powers. At RF frequencies, it usually consists of two transformer-coupled common-source devices operating in antiphase. An alternative is the push-pull architecture, shown in Figure 1, which features two devices of the same polarity driven by an active driver stage. The additional current consumption of this driver stage results in low RF efficiency.

Toshiba designers used Cadence's AWR® software to investigate the push-pull PA with the long-term objective of producing an integrated push-pull RF PA in a single package that is the same size as a conventional RF transistor. This would result in a PA size reduction of over 90%, suitable for many high-density applications where large numbers of these PAs operate together in a small space, such as phased array radars and 5G massive multiple-in-multiple-out (MIMO) communications systems.

#### Application

Push-pull RF power amplifier

#### Cadence<sup>®</sup> Technologies

- AWR Design Environment<sup>®</sup> Software Portfolio, including:

- Microwave Office® Circuit Design Software

#### Benefits

- Quality of results

- Ease of use

- Speed of simulation

- Proficient support services

Figure 1: Push-pull architecture

In this work, two N-channel field-effect transistor (FET) devices were used, one of which operated in a source-follower configuration, which is not normally covered by the datasheet or the simulation model. Although the low-frequency transistor models complied, moving up in frequency to the RF region led to problems, as the source follower's parasitic components were not sufficiently characterized. The source follower also had a very high input impedance (approximately 1k $\Omega$ ). This was significantly higher than the typical 50 $\Omega$  domain of RF circuitry, making the circuit layout susceptible to the influence of stray capacitance and inductance.

### Solution

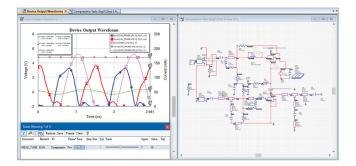

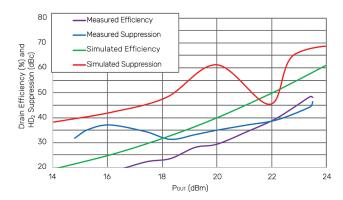

Using the AWR Design Environment platform, specifically Microwave Office circuit design software, the designers successfully imported the transistor models and simulated the circuit, as shown in Figure 2. Operation was confirmed by the current waveforms and the suppression of the second harmonic, shown in Figure 3.

The software enabled the designers to characterize the gain and phase relationship between the two signal paths. This was very important, since the two transistors in the PA must operate in antiphase, but with the same magnitude for correction push-pull operation. It was also clear from the current waveforms that the distortion generated by operating the transistors in two different modes (common source for one and source follower for the other) introduced different distortion profiles. This was previously unknown.

Figure 2: Microwave Office schematics and simulation results

"We use Cadence AWR software on a daily basis in our research activities, which are projects that are typically five to 10 years away from market. The software enables us to take rough ideas for future products and develop them into prototypes."

Dr. Gavin Watkins, Toshiba Research Europe Limited

Figure 3: Optimum amplifier performance

### Conclusion

The Toshiba designers successfully proved the feasibility of a push-pull PA at RF frequencies with AWR software. Using two gallium arsenide (GaAs) N-channel devices in simulation, 69.5% DC-to-RF efficiency at a P1dB of 25.1dBm was achieved. A practical prototype achieved 48.1% efficiency at 23.5dBm P1dB with a second harmonic distortion (HD2) suppression relative to the fundamental component of -47dBc.

The lead designer has been using AWR software for more than a decade. He commented that the software is easier to use and offers greater coherence between the simulation engines than the alternatives. The most positive feature is the intuitiveness of the software. It is very straighforward to start a new simulation with ideal components and then gradually increase the complexity by adding in realistic models for components and substrates.

Toshiba Research Europe Limited designers use AWR software on a daily basis in their research activities. These are projects that are typically five to 10 years away from market, and the software enables them to take rough ideas for future products and develop them into prototypes. Toshiba, like most companies, invests heavily in long-term research to ensure that it can release products that offer a better price/performance ratio than competitors. The original paper for this application, written by Dr. Gavin Watkins of Toshiba Research Europe, can be found at ieeexplore.ieee.org/document/8283349/.

Special thanks to Dr. Gavin Watkins for his contributions to this success story.

## cādence<sup>°</sup>

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world's most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications. **www.cadence.com**

© 2021 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners. 16836 07/21 SA/UV/PDF