# cādence<sup>°</sup>

# Multi-Chip Module Design, Verification, and Yield Optimization Using AWR Software

As wireless communications systems evolve, smaller devices with better performance are required that incorporate multi-technology-based module designs with different integrated circuit (IC) and PCB process technologies. Front-end module (FEM) manufacturers are now integrating gallium arsenide (GaAs), silicon germanium (SiGe), or radio-frequency complementary metal-oxide semiconductor (RF CMOS) power amplifiers (PAs), CMOS or silicon-on-insulator (SOI) switches, and acoustic filters—all mounted on a single laminate package.

# Design Overview

This application note presents a unified design flow that streamlines full module simulation, inclusive of all process technologies, enabling designers to leverage the strengths of specialized electromagnetic (EM) modeling and circuit analysis tools to address various functional block technologies, maintaining all through a single user-interface environment. The application is a dual band, 1.9GHz (cellular)/ 2.5GHz wireless local area network (WLAN) FEM that includes two PAs (GaAs and SiGe), surface-mount bulk acoustic wave (BAW) filters, and a laminate substrate.

The designer used full-design simulation, inclusive of EM verification and yield optimization, enabling him to not only understand the design sensitivity to specific component and manufacturing tolerances but also to compensate for the impact of these variations on the overall design performance in order to achieve a more robust end product.

## Multi-Chip Module Design Issues

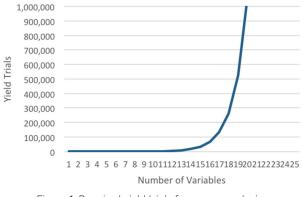

Multi-chip module designers face a multitude of design challenges relating to the manufacturability of complex multi-layer substrates. Included in these challenges are many uncorrelated factors associated with substrate fabrication such as registration errors or etch-tolerance of the package trace metals. While a corners analysis would be a typical process for IC design, doing it for yield analysis of a module with a large number of variables becomes impractical very quickly, as the number of yield trials required grows exponentially with the number of variables (Figure 1).

For example, consider a five-layer module with 10 surface-mount components. Here there might be five variables each for registration, under/over etch, and dielectric variation, as well as 10 variables for the variation of the surface-mount parts, resulting in 33.55 million yield trials. No reasonable designer could wait for the simulation results for such a large amount of simulation trials.

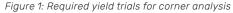

Another challenge concerns capturing the component-to-component interactions in a module design that often contains multiple technologies that are analyzed with separate, specialized IC- and PCB-focused simulation tools/design flows (Figure 2).

Figure 2: In module design, there are usually multiple technologies, as well as the PCB technology of the module itself

While designers rely on tools that are efficient for designing each constituent part of the module, at some point in time, they do need to bring all of these disparate designs together in order to perform a full system simulation and verification. If the component tools are interoperable, designers are able to quickly simulate and verify the full system design more readily. A simple example of this would be a case where an RFIC is designed using the Cadence® Virtuoso® ADE Product Suite and Cadence Spectre® Simulation Platform and the PCB is designed with the Cadence AWR Design Environment® platform, specifically the Cadence AWR® Microwave Office circuit design software.

## AWR Microwave Office Design Flow

To address these challenges, the AWR Microwave Office software offers an integrated design flow for harnessing multiple simulation technologies developed specially to address individual components found in multi-chip module design. Tool interoperability between AWR Design Environment platform and third-party specialized tools allows designers to incorporate existing IC designs represented as blocks within the overall multichip/substrate simulation. In the example discussed above, the RFIC was imported as a Virtuoso platform-generated Spectre simulation netlist into the AWR Design Environment platform, which then directly simulated the Spectre netlist block using the Cadence AWR APLAC® harmonic balance / transient circuit simulation engine.

Designers can therefore turn their attention to optimizing off-chip design, interconnect, and matching network modeling, as well as yield or corners analysis. Design centering for improved yield analysis can also take place through surface-mount component (SMC) selection or laminate redesign directly in AWR Microwave Office software. Alternatively, a parameterized Spectre netlist containing S-parameter data sets from the yield analysis can be exported from the AWR Design Environment platform and used within the Virtuoso ADE Product Suite to address design centering for higher yields at the RFIC level.

To expedite yield analysis with a more efficient alternative than corners analysis, the AWR Microwave Office software provides Monte Carlo analysis, which can give meaningful yield results with many fewer yield trials. In addition, even though Monte Carlo analysis is more efficient, there will still be a large number of yield simulations that need to be performed, which can be very time consuming. Thus, the AWR Microwave Office software also provides the ability to distribute and parallelize these simulations among remote servers, thereby further reducing the amount of time it takes for engineers to obtain their yield results.

### Monte Carlo Analysis

Monte Carlo yield analysis consists of performing a series of trials or iterations. Each trial results from randomly generating parameter values according to its specified statistical variation, performing a simulation, and evaluating the result against stated performance specifications. It is easy to compute the number of yield trials required to achieve a specific yield percentage with an acceptable error percentage for a particular confidence level. For example, if the yield is 90%, a 1% error in results is acceptable, and the confidence level is 95.4%, with the equivalent number of yield trials at 3600, as shown in Equation 1.

$$N = \left(\frac{C_{\sigma}}{\varepsilon}\right)^2 \cdot Y(1-Y)$$

Equation 1: Where  $C_{r}$  is the confidence expressed as a number of standard deviations

The sample or trial size, N, is then calculated from:

- Confidence level (standard deviations)

- ▶ % error (ε)

- ► % yield (Y)

- Number of trials (N)

A confidence level of 95.4% equals a standard deviation of two, therefore the number of trials is calculated at 3600, or in equation form:  $N = (2/.01)^2 \times .9(1-.9) = 3600$ .

Given that Monte Carlo analysis is not a function of the number of variables, the designer can get meaningful yield analysis results for problem spaces with a large number of independent variables with much fewer trials than a corners analysis.

#### Laminate Yield Analysis

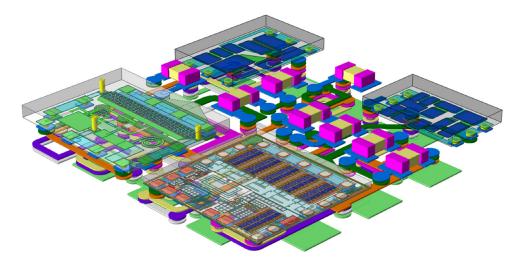

The AWR Design Environment software supports the analysis of manufacturing variations, which is especially useful in laminate design. The software offers layer-based modifiers that shift entire layers, making setup very straightforward when looking at the registration error, over/under etch factor, particular manufacturing variations, parametric material dielectric variations, or surface-mount part tolerances. Because they are simply parameters, the designer can do a parametric sweep or set up a particular yield distribution for these parameters. Even more conveniently, the environment provides a viewer with connectivity for visual verification of these geometry modifications.

#### Layer-Based Shape Modifiers

To elaborate on layer-based shape modifiers, when looking at the spiral inductor on the left in Figure 3, it can be seen that the metals are all the same width and, in addition, are all aligned with each other in the Z axis. It can be seen that there is no registration error. In the spiral inductor on the right, however, the layers have shifted independently of one another in the X and Y axis. In addition, the pink one has become thicker and the gold one has become thinner. These issues correspond to the registration error as well as the over/under etch.

Figure 3: Metals are the same width/aligned on the Z-axis in the spiral inductor (left), and layers have shifted in X/Y independently of one another (right)

For each layer, there might be one modifier and then the amount that it moves each layer can be assigned a parameter based on a statistical variation, as shown in Figure 4.

| dit Equation                                   |                                                                                                                                               | $\times$ |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| /ariable Name                                  | Variable Value                                                                                                                                |          |  |  |  |

| U1_X =<br>Variable Type<br>Variable definition | 0 Parameter Definition Description                                                                                                            |          |  |  |  |

| O Parameter definition<br>O Display value      | Does not affect layout Unit Type Scalar Data Type Real                                                                                        | ~        |  |  |  |

|                                                | Statistics         Distribution Type           pper bound         Optimize yield         Uniform           In percent         +/-         N/A | ~        |  |  |  |

Figure 4: Statistical variation for each layer

#### **Statistical Parameters**

Setting up the statistical variation for the dielectric constant in this module example is also quite easy. The designer need only indicate that this variable is enabled for statistics, specify a distribution type, and assign it a standard deviation or variation percentage. This variable is then used in the material stack-up profile. When a yield analysis is performed, the value of the dielectric constant will assume a value based on its statistical variation.

#### Visual Inspection with Connectivity

When manipulating layers, as is done with the layer-based modifiers feature, incorrect numbers can be entered that result in shorts or opens in the circuit. The connectivity highlighter tool in AWR Microwave Office software shows if the metal connectivity is changing, enabling designers to ensure that there are no opens or shorts in the circuit prior to simulation. (Figure 5).

Figure 5: The connectivity highlighter in AWR Microwave Office software highlights if the metal connectivity is changing to ensure there are no opens or short in the circuit when using the layer modifiers tool

#### **Distributed Parallel EM Simulations**

To speed up simulation run times, the distributed EM capabilities within the AWR Design Environment software enable users to send all of the EM simulations to a remote server and distribute those simulations across any number of computers, significantly reducing simulation wait time since the amount of time it takes to get the results back is divided by the number of computers being used for parallel simulations (Figure 6). The results that come back are in the form of data sets that can be used later.

Figure 6: EM capabilities enable users to send EM simulations to a remote server for parallel simulations, which reduces simulation times

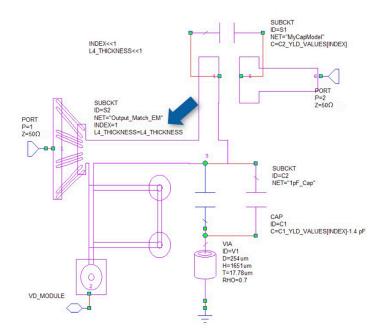

#### Virtuoso ADE Product Suite-Compatible Models

The output of the yield analysis in the AWR Design Environment software is a parameterized Spectre netlist of S-parameters that correspond to the yield analysis trials (Figure 7). This allows module representation resulting from the yield analysis to be utilized in the Virtuoso environment for design optimization of the RFIC power amplifier.

Figure 7: AWR Microwave Office software outputs the results of yield analysis as Spectre simulation-compatible netlists

#### Load-Pull Model

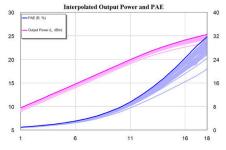

AWR Microwave Office software-generated load-pull data files can be used in conjunction with yield analysis to study the impact of module manufacturing tolerances on nonlinear behavior using load pull. These load-pull files contain the A and B waves of the device as a function of load and source impedance presented to the device. A and B waves are used to derive other performance metrics of the device, such as power-added efficiency (PAE), gain, and output power. The performance metrics can be interpolated for an arbitrary load presented to the device. This method can be used during yield analysis and is a great way to quickly get circuit performance metrics for arbitrary loads.

This capability enables users to simulate the performance of an active device (transistor or PA) without actually having a device model in the environment, so there is no need to translate the model or have cross-tool process design kit (PDK) support. In addition, the simulation speed is more like a linear simulation rather than a harmonic balance nonlinear simulation, even though the user is looking at nonlinear results like output power or PAE. When performing a yield analysis, designers are able to leverage the simulated load-pull data, which allows them to apply an arbitrary load and provide the required interpolated performance metrics. The graph in Figure 8 shows the actual PAE and output power for a yield analysis where the variations in results are due to changing impedances presented to the output of the chip PA by the laminate, highlighting the interactions that occur between the MMIC/RFIC and module/packaging.

|         | C1     | C2      | Er   | M1 Etch | Cont |

|---------|--------|---------|------|---------|------|

| Nominal | 1pF    | 100pF   | 4.47 | 0µm     |      |

| Outlier | 1.28pF | 119.6pF | 4.58 | -5µm    |      |

Figure 8: The actual PAE and output power for a yield analysis, where the impedances presented to the device were arbitrary and the output power and PAE were interpolated

## Design Centering

Once the yield analysis is performed, the designer can identify the parameter sets that lead to yield failures or correspond to the outlier traces shown in Figure 8. Then the tolerances of the yield variables can be changed or the design can be centered so the yield is higher.

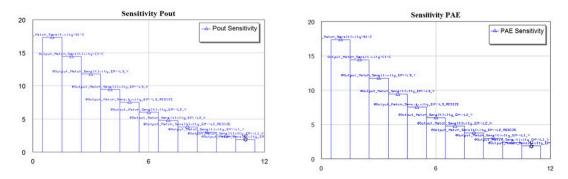

## Sensitivity Analysis

In addition to yield analysis, AWR Design Environment platform users are able to do a full sensitivity or Pareto analysis. The benefit of this is that all the variables that are set up for yield are weighed against one another, enabling designers to look at which particular parameters in the yield analysis are causing the most change or degradation of particular performance metrics. For example, in Figure 9, the sensitivity of the output power and PAE are being examined over all the variables in that particular yield analysis, and those variables are going to be different for each performance metric.

Figure 9: The sensitivity of the output power and PAE are examined over all the variables in that particular yield analysis

## Design Methodology Scales to Design Variables

This same methodology corresponds to design as well as yield. The PCB/module designer can perform a parametric design and export it as a parameterized netlist into the Virtuoso environment, where the IC designer can understand the design constraints and optimize the IC in order to get the best performance out of the total module (Figure 10). With a parameterized laminate, the IC designer working in the Virtuoso environment is not constrained to a "fixed" laminate model and can explore different variations within a single, parameterized laminate model block.

Figure 10: The PCB design can be exported to the Virtuoso environment, where the IC designer can optimize the PCB to the IC

## Conclusion

This application note has described a unified design flow, inclusive of EM verification and yield optimization, for a front-end module involving several process technologies. Using the AWR Design Environment software enabled the designer to understand sensitivity to specific component and manufacturing tolerances and to compensate for the impact of the variations on the overall design performance to achieve design goals of small size and optimum performance.

Because of the large number of independent variables in module design and analysis, it is important to leverage a design flow that can handle yield analysis with many independent variables. The Monte Carlo approach within the AWR Microwave Office software provides a more efficient analysis than traditional corners analysis. AWR Microwave Office shape/layer modifiers enable designers to look at the actual manufacturing variances that occur in modules, such as registration error or edge tolerance. In order to minimize simulation time and get results back more quickly, designers can leverage remote simulation servers in order to take advantage of distributed parallel EM simulation. Finally, by creating Virtuoso ADE Product Suite-compatible models and parameterized Spectre netlists, the AWR Design Environment software further enables designers to combine simulations and look at the full system simulation and verification.

## Acknowledgment

Special thanks to Shane Coffman, Cadence.

cādence°

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world's most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications. **www.cadence.com**

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide; Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners. 14720 06/20 SA/RA/AN-MWO-MCM/PDF