### **DESIGN IP BROCHURE**

# cādence°

## 32/25Gbps Multi-Link and Multi-Protocol PHY IP for TSMC 5nm FinFET

#### Overview

The Cadence® 32/25Gbps Multi-Link and Multi-Protocol PHY IP for TSMC 5nm FinFET is a high-performance SerDes operating from 1.25Gbps to 32Gbps and specifically designed for infrastructure and data center applications. It features long-reach equalization capability at very low active and standby power. The SerDes offers very low latency for time-critical applications for enterprise-level data communications, networking, and storage systems.

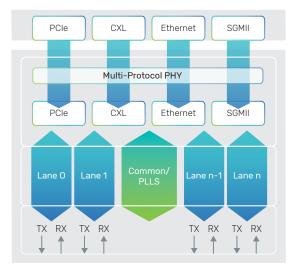

The PHY IP provides extensive flexibility to mix and match protocols within the same macro. The PHY IP is designed to run PCI Express® (PCIe®), Compute Express Link (CXL), 25G-KR, and 10G-KR. Multiple test features are embedded and easily accessible by the end user. A user-friendly graphical interface called EyeSurf provides convenient access to real-time and non-destructive eye scope and bathtubs for monitoring the bit error rate (BER) and the link performance during live traffic.

The PHY IP quickly and easily integrates into any system on chip (SoC) and connects seamlessly to the Cadence controller for full flexibility. This minimizes time and risk of device development. It offers integrators the advanced capabilities, flexibilities, and support for advanced, high-performance designs.

Figure 1: Example system-level block diagram

#### Benefits

- Flexibility Maximum flexibility and reconfigurability

- Maturity Silicon proven and robust SerDes architecture

- Ease of use Faster to integrate, bring up, and support

#### **Key Features**

| High-performance PHY for data center applications                                                            | <ul> <li>Non-destructive on-chip EyeSurf oscilloscope interface</li> <li>Extensive set of isolation, test modes, and loop-backs including APB and JTAG</li> </ul> |  |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Low-latency, long-reach, and low-power modes                                                                 |                                                                                                                                                                   |  |

| <ul> <li>Wide range of protocols that support networking,<br/>storage, and computing applications</li> </ul> | Supports 20-bit and 32-bit PIPE and non-PIPE interfaces                                                                                                           |  |

| <ul> <li>Multi-protocol support for application flexibility</li> </ul>                                       | <ul> <li>Selectable serial pin polarity reversal for both transmit<br/>and receive paths</li> </ul>                                                               |  |

#### **Product Details**

The PHY IP provides performance, reliability, and robustness for the most demanding applications.

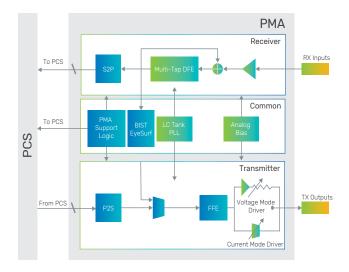

The PHY IP is architected as a hard PHY macro with a physical media attachment (PMA) layer and a soft physical coding sublayer (PCS) available for various processes. The PHY IP supports a long-reach (LR) backplane with insertion loss in excess of 36+dB for rates up to 32G. It is specifically optimized to minimize end-to-end latency and power. Low-power modes are also supported (e.g., PCle L1 substrates) for energy-efficient applications. For robustness, the PHY is designed to operate from -40°C to 125°C, features superior ESD protection, and is designed to exceed the stringent reliability requirements of data center applications.

The PCS complies with the latest PCIe PIPE specification and provides support for the dynamic equalization features of different interface protocols. The PHY IP is designed for handling multiple protocols on one single PHY macro (see table below).

#### **PHY Architecture**

The PHY IP architecture provides greater control over floorplanning, placement, packaging, and I/O integration than other hard PHY solutions, while maintaining the reliability and ease of use associated with GDSII macros.

Figure 2: IP-level block diagram

#### Availability

The PHY IP is available with various configurations and supports the following protocols:

| Protocol                 | Data Rate (Gbps/Lane) | Process Node |

|--------------------------|-----------------------|--------------|

| CXL                      | Up to 32              | 5nm FinFET   |

| PCle 5.0/4.0/3.1/2.1/1.1 | Up to 32              | 5nm FinFET   |

| 25G-KR                   | Up to 26.5625         | 5nm FinFET   |

| 10G-KR                   | 10.3125               | 5nm FinFET   |

| QSGMII/SGMII             | 5/1.25                | 5nm FinFET   |

\*Base product supports one protocol. Additional protocol support available as options.

#### **Related Products**

- Controller IP for CXL

- Controller IP for PCIe 5.0, 4.0, 3.1, 2.1, 1.1

#### Deliverables

- Integration Views: Verilog behavioral model, GDSII, CDL, and power models

- Synthesizable RTL

- DFT-Verilog netlists with SS/FF, CTL, and BSDL

- Reference Verilog testbenches used for generating SoC-level VCD ATE test patterns for PHY

- IBIS-AMI kit

- Documentation: XML, integration and user guide, release notes

- Test boards available on demand

For more information, visit cadence.com/designip

Cadence is a pivotal leader in electronic systems design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world's most creative and innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic applications. **www.cadence.com**

© 2022 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners. J12584 11/22 SA/VY/PDF