# cādence

## Controller IP for Quad Serial-Peripheral Interface

### Overview

Flash memory now utilized frequently in computers and electronic devices found in automotive, IoT, drones, connected home, and other emerging applications is demanding ever higher transfer rates and lower latency. Expanding the flash Serial Peripheral Interface (SPI) accesses from the current 4 I/Os (Quad SPI) to 8 I/Os (Octal SPI) increases the Serial NOR Flash throughput and provides a more efficient solution for emerging applications, while providing backwards compatibility with support for single, dual, quad, or octal I/O interfaces.

The Cadence<sup>®</sup> Controller IP for Quad Serial-Peripheral Interface (QSPI) can be used to provide access to Serial Flash devices. Standard Serial Peripheral Interface (SPI) is supported along with high performance Dual and Quad SPI variants.

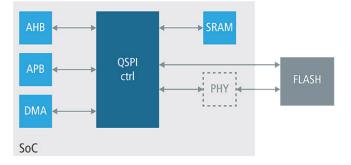

The Controller IP connects to system-on-chip (SoC) environment through its AMBA® AHB® bus and APB bus interfaces. The AHB interface is used to transfer data, either in a memory mapped direct fashion (for example a

Figure 1: Example System-Level Block Diagram

#### **Benefits**

- · Low-risk solutions—silicon-proven design

- Ease-of-use—customizable with easy integration

- Efficiency—optimized data transfer ensured

processor wishing to execute code directly from external Flash memory), or in an indirect fashion where the controller is setup via configuration registers to silently perform some requested operation, signaling its completion via interrupts or status registers.

For indirect operations of the Controller IP, data is transferred between system memory and external Flash memory via an internal SRAM which is loaded for writes and unloaded for reads by an AHB master within the system-on-chip (SoC) environment at low latency AHB system speeds.

An optional DMA peripheral bus is also available to optimize the data transfers between an external master and the Controller IP during indirect transfers.

| Key Features                                                                                                                              |                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Local SRAM of configurable size to reduce AHB<br/>overhead and buffer Flash data during indirect<br/>transfers</li> </ul>        | • Support for XIP (Execute in Place), DDR mode, single,<br>dual or quad I/O instructions, BOOT and legacy modes    |

| Optional DMA peripheral interface to communicate<br>indirect mode status with external DMA                                                | <ul> <li>Supports any device clock frequency, including current<br/>market device frequencies of 133MHz</li> </ul> |

| <ul> <li>Programmable: device sizes, write protected regions,<br/>delays between transactions, interrupt generation</li> </ul>            | <ul> <li>Set of software APB accessible FLASH control registers<br/>to perform any Flash command</li> </ul>        |

| <ul> <li>Serial clock with programmable polarity,<br/>programmable baud rate generator, up to four<br/>external device selects</li> </ul> | Compliant with AMBA2 specification                                                                                 |

#### Product Details

The Controller IP is a controller that enables access to Serial Flash devices, while providing various modes of operation and improved high speed read data capture mechanism.

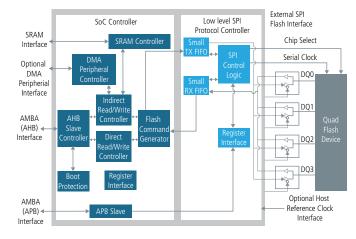

#### **APB Interface and Register Module**

The APB interface is used to configure the core and perform software controlled Flash accesses using the Flash Command Control register. The APB interface feeds a single register block containing the programmable register set. The register block is timed to the APB clock. All control or enable bits that are triggered by APB writes and cause an event to trigger, or an operation somewhere in the QSPI controller to be enabled are synchronized to the destination clock. Static configuration bits that have no effect while a separate enable bit is low do not require synchronization.

#### AHB Control Interface

The AHB slave controller validates incoming AHB accesses, responds to invalid requests, performs any required byte and half-word reordering, blocks writes that violate the programmed write protection rules (only for direct access) and forwards the transfer request to either the direct access controller or the indirect access controller.

### **Direct Access Controller (DAC)**

Direct access refers to the operation where AHB accesses directly trigger a read or write to Flash memory. It is memory mapped and can be used to both access and directly execute code from external Flash memory. Any incoming AHB access that is not recognized as being within the programmable indirect trigger region is assumed to be a direct access and will be serviced by the direct access controller.

### Indirect Controller (INDAC)

The aim of the indirect mode of operation is to read significant numbers of bytes from Flash memory without requiring an AHB access to trigger it. Instead indirect operations are controlled and triggered by software via specific APB control/configuration registers. This block will communicate with an embedded low level SPI protocol state machine module to perform an efficient and optimized Flash read burst, placing the read data into the local SRAM module ready for fast and low latency delivery to any external AHB master. Indirect transfer can be optionally performed along with external DMA Module. DMA Peripheral Controller ensures effective low-latency AHB transfers.

#### Availability

The Controller IP is available with various configurations and supports the following protocols:

- QSPI + Soft PHY

- QSPI Controller

#### **Related Products**

- Cadence VIP for Quad-Serial Peripheral Interface

- Cadence Controller and PHY IP for Octal SPI Flash

- Cadence Controller and PHY IP for Quad-Serial Peripheral Interface

#### Deliverables

- Clean, readable, synthesizable Verilog HDL

- Cadence Encounter® RTL Compiler synthesis scripts

- Documentation—integration and user guide, release notes

- Sample verification testbench

- IP-XACT xml file

For more information, visit ip.cadence.com

Cadence Design Systems enables global electronic design innovation and plays an essential role in the creation of today's electronics. Customers use Cadence software, hardware, IP, and expertise to design and verify today's mobile, automotive, cloud, and connectivity applications. www.cadence.com

© 2017 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, Encounter and the Cadence logo are registered trademarks of Cadence Design Systems, Inc. in the United States and other countries. AMBA and AHB are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. All other trademarks are the property of their respective owners.