# CAE Flow in the Development for the Digital Equipments

Motochika Okano PC Development Center Toshiba Corporation 2008/09/19 (Fri )

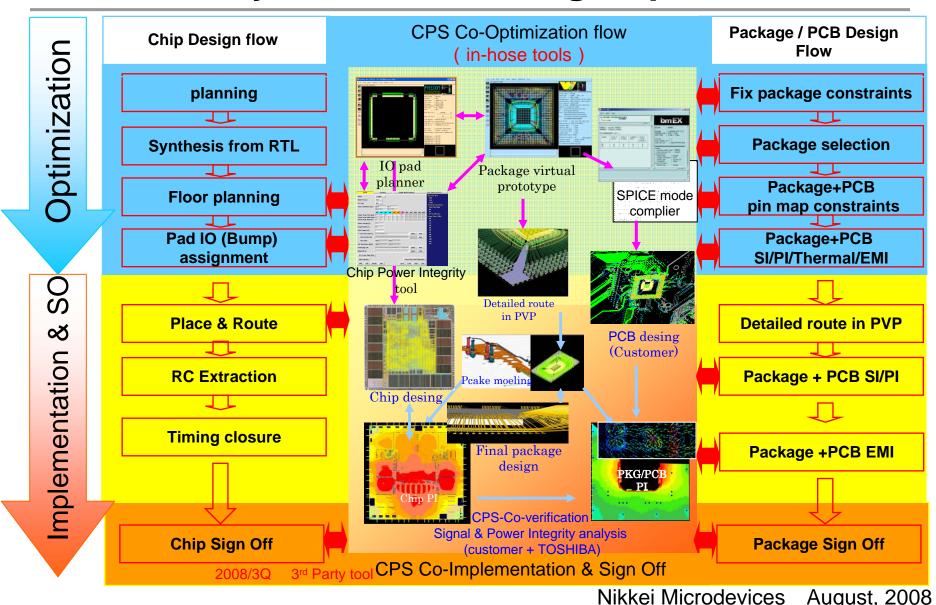

- CAE Flow for PCB Design

- Chip / Package / PCB Modeling

- CAE Flow for PCB Design

- Chip / Package / PCB Modeling

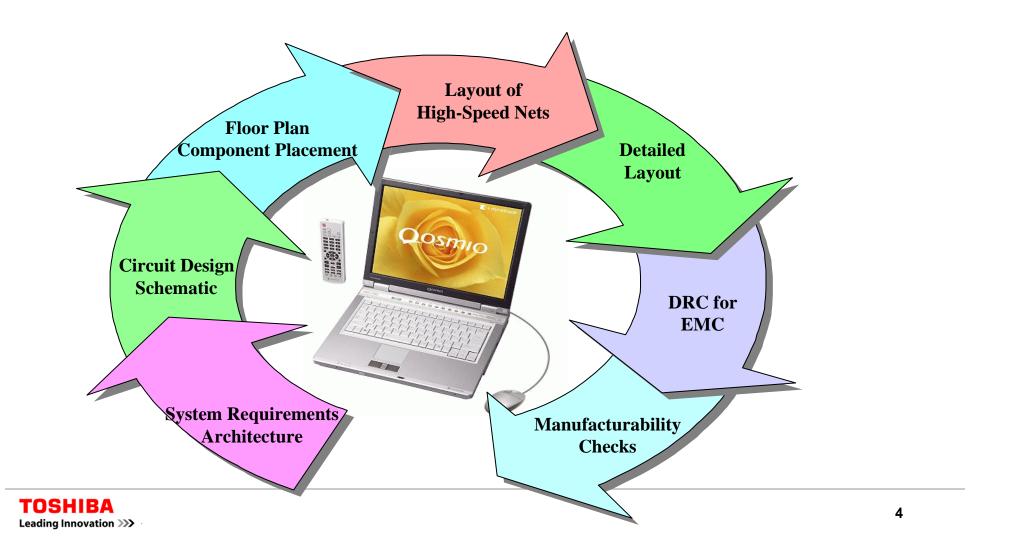

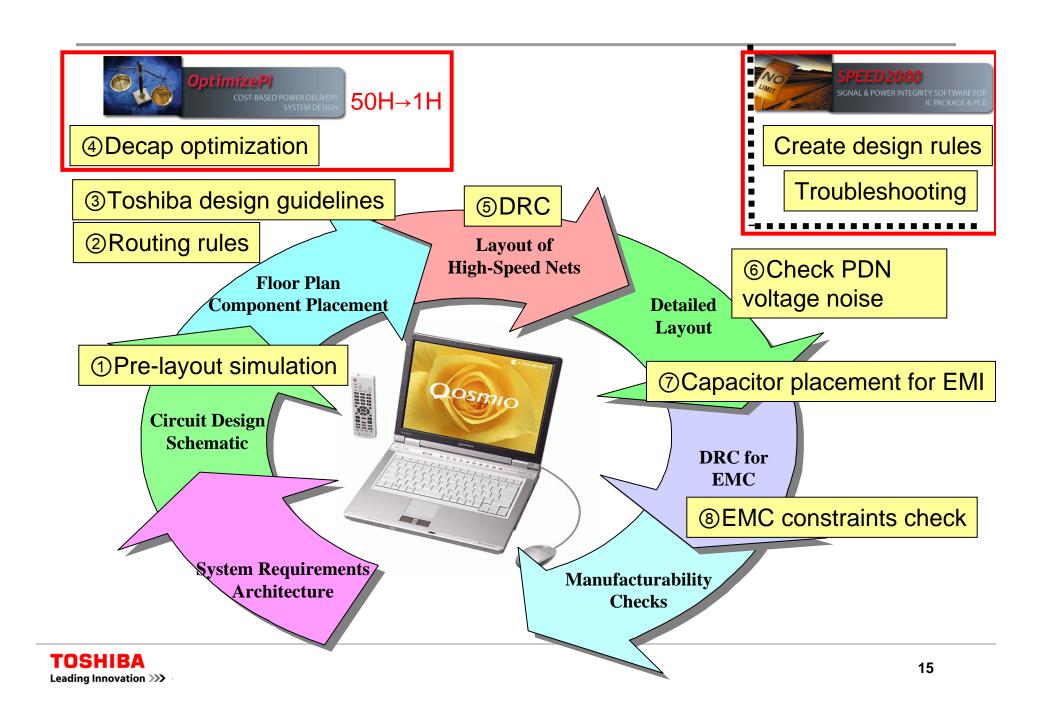

### **PCB Design Flow**

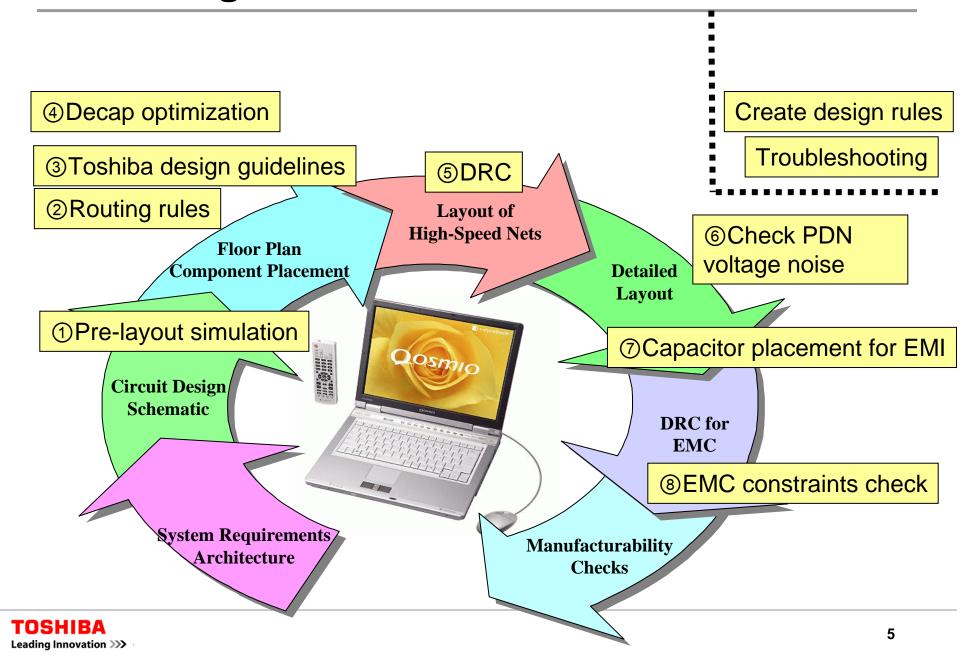

### **PCB Design Flow**

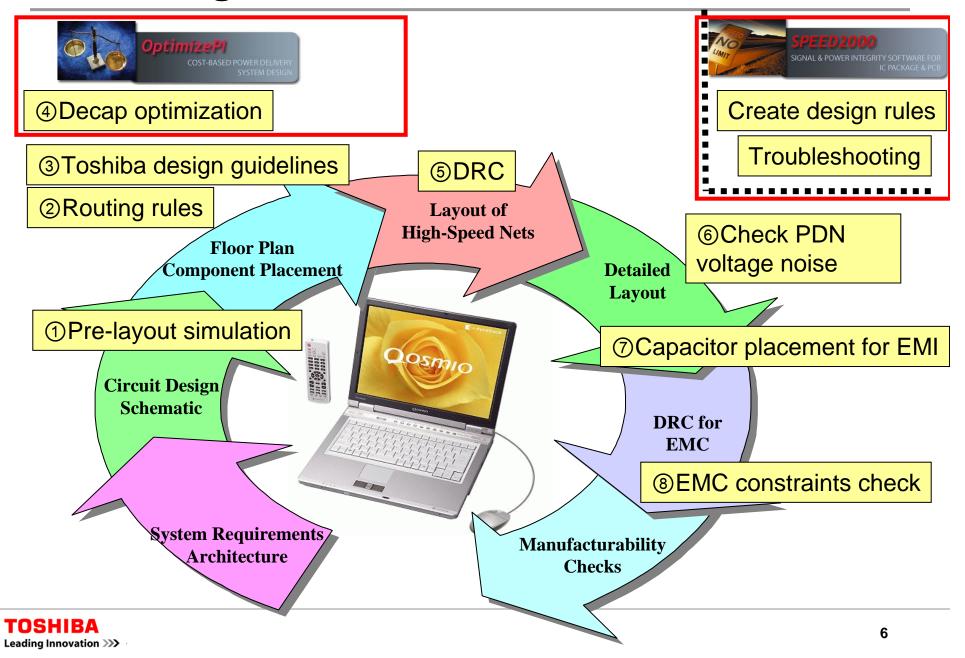

### **PCB Design Flow**

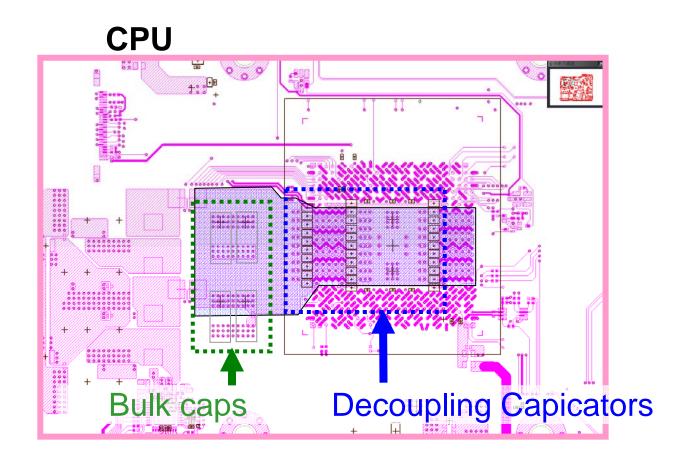

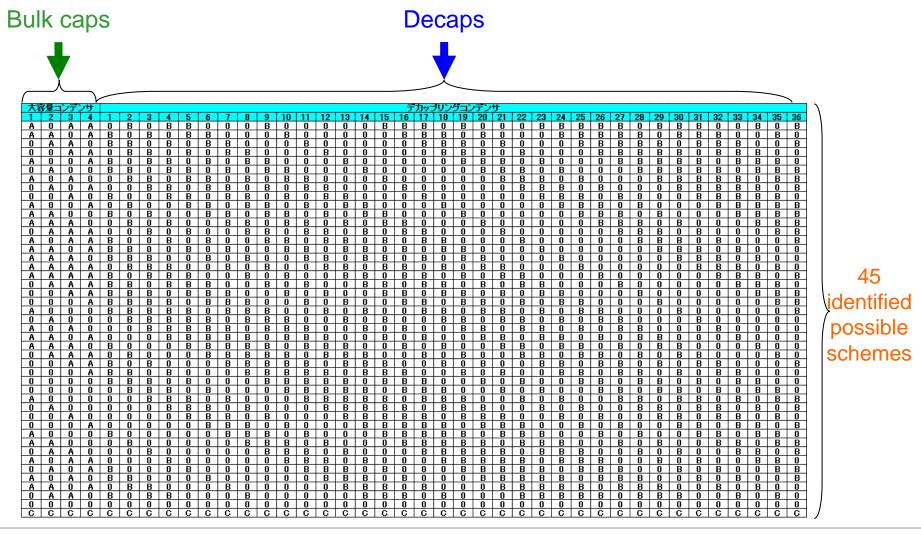

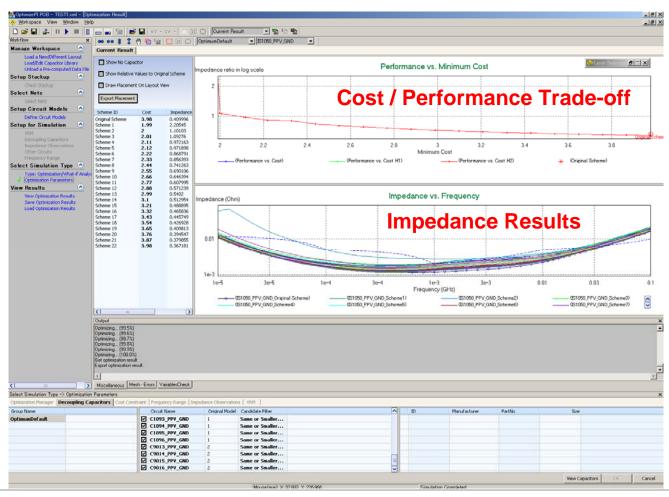

### **Case Study for Decap Optimization**

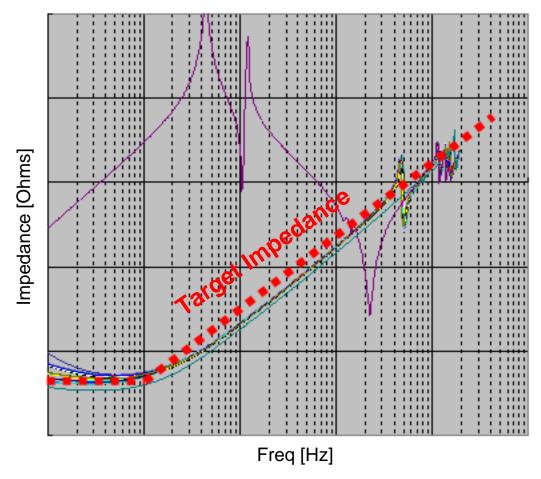

### < Typical Methodology (before OptimizePI) >

1. Identify decap placement locations from CPU supplier specifications

2. Pickup possible decap combinations based on Design of Experiment approach (1 hour for this design)

3. Simulation of impedance for all 45 combinations one by one. (1 hour per combination. This takes about 45 hours in total.)

4. The best scheme, based on performance and cost, is identified by engineers. (This typically takes 4 hours.)

A typical project takes 50 hours for decap optimization.

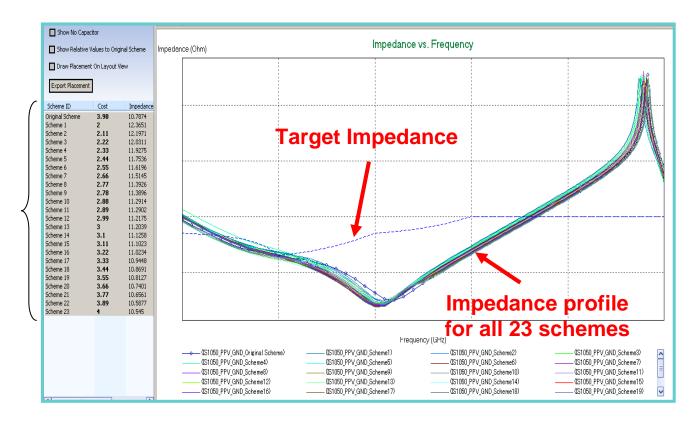

### < OptimizePI is now used instead >

1. Automatically identify the best scheme in 1 hour.

Extract 23 optimized schemes

2. Result with OptimizePI enables engineer to quickly select the best scheme from the 23 candidates

OptimizePI gives results in 1 hour compared to 50 hours Toshiba spent before.

It is also important that Toshiba's basic flow is the same. OptimizePI adoption does not require a flow change.

OptimizePI results match with prior method for accuracy.

- CAE Design Flow for PCB Design

- Chip / Package / PCB Modeling

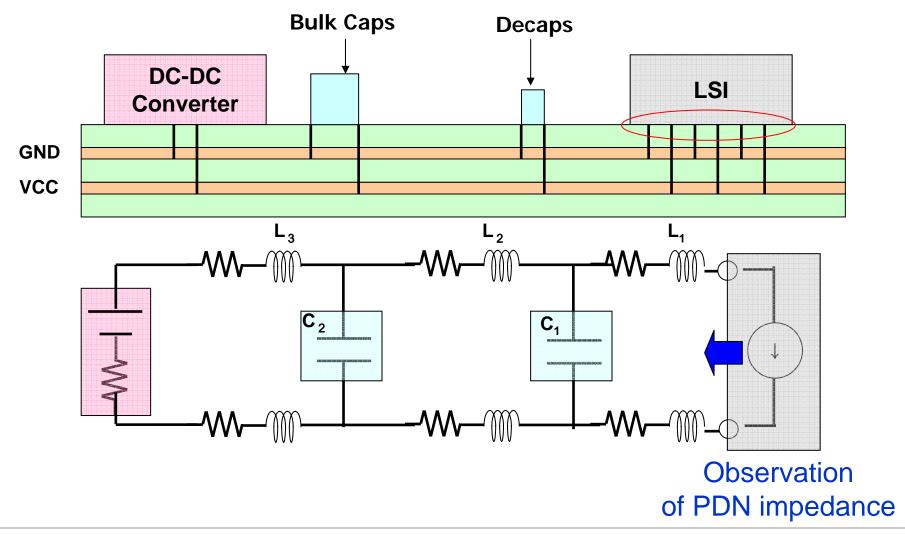

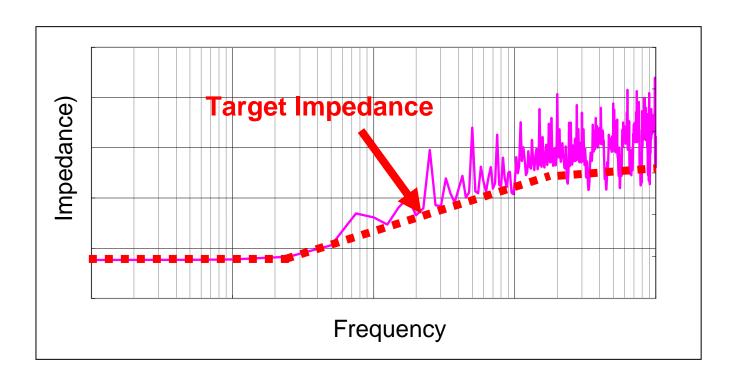

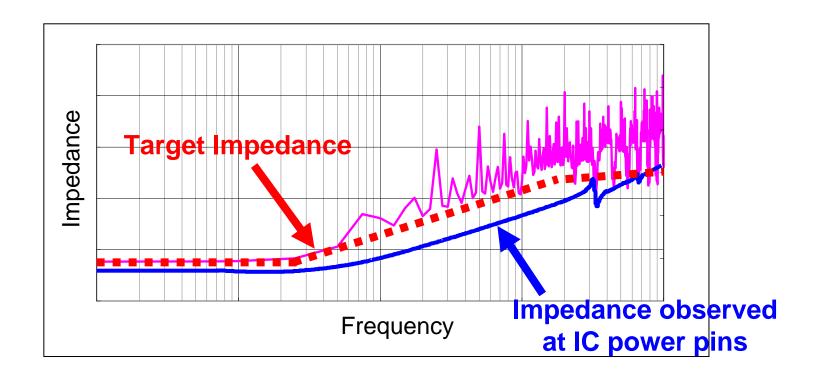

## Methods to determine the target impedance for PDN optimization

- LSI vendor provides We use their information.

- LSI vendor doesn't provide We make our own calculations.

#### CAE Effort by Semiconductor group at Toshiba

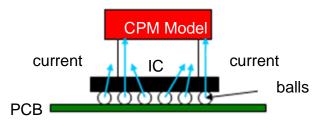

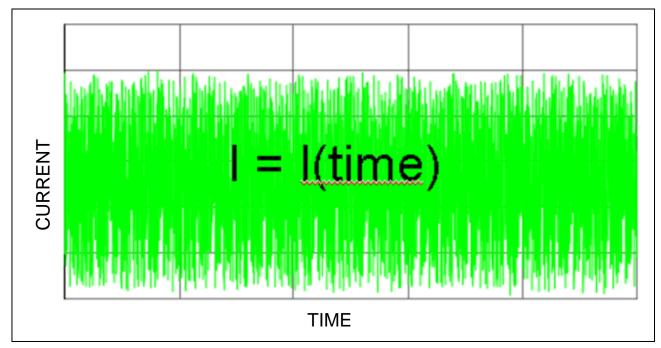

The total chip power current is extracted from all the power pin current observations.

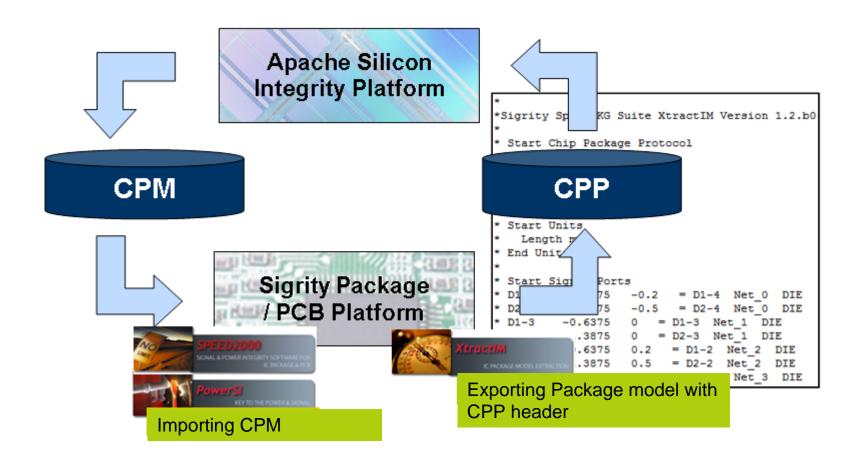

CPM (Chip Power Model) includes parasitic of entire chip power delivery network

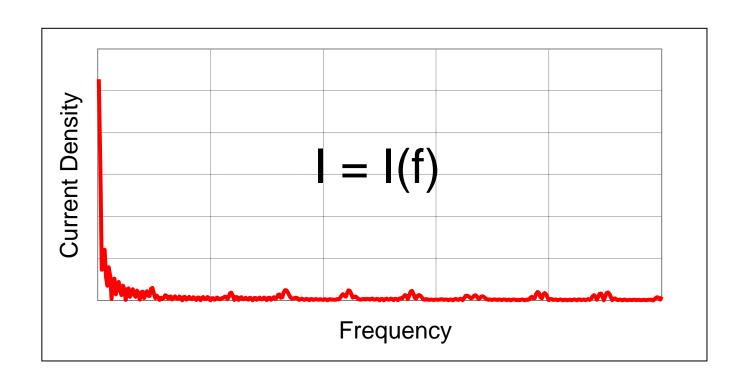

Fourier transform of CPM current waveforms

The current spectrum in frequency domain is used to calculate target impedance.

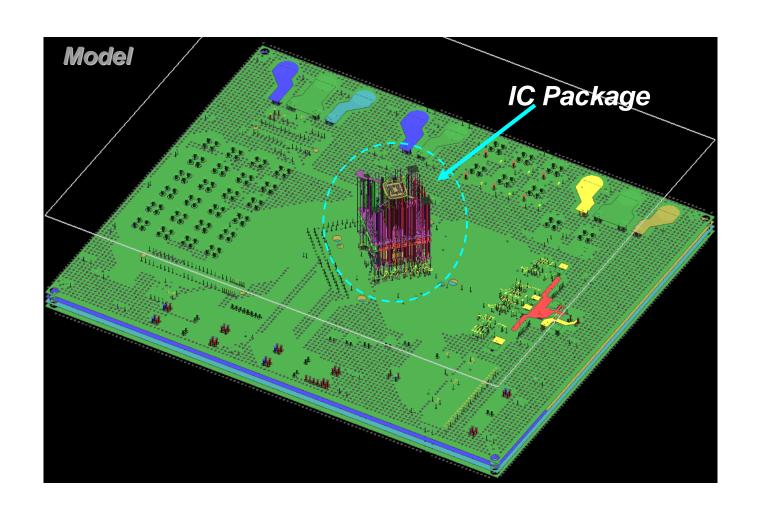

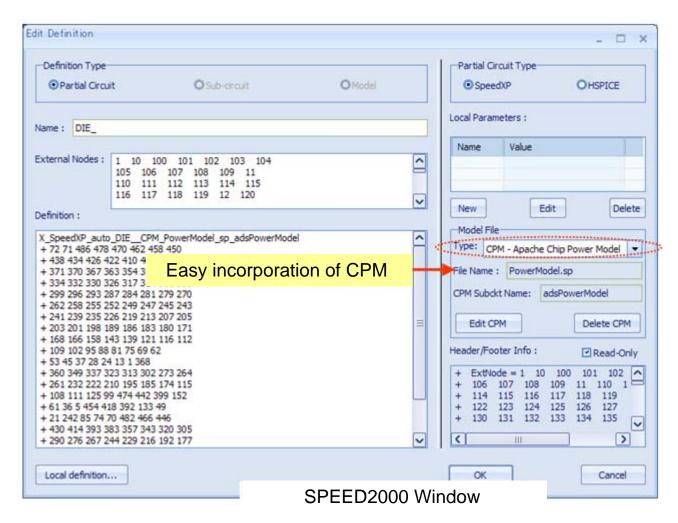

CPM and SPEED2000 used together

Using CPM Model in SPEED2000

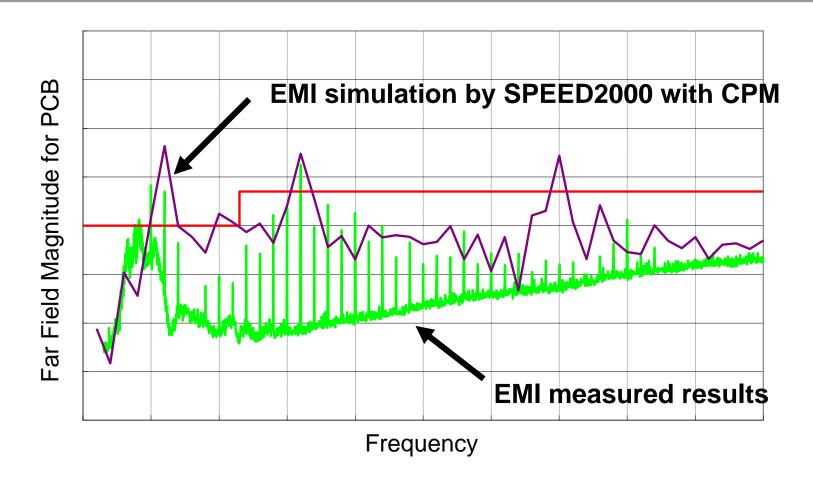

CPM model used as a noise source in SPEED2000 simulation. Far Field results show good correlation to measurements.

### Summary

- CAE Utilization in PCB Design

- Decap optimization flow with OptimizePI

- CPM can help in calculating target impedance

- CPM can be used with SPEED2000 for EMC analysis

# TOSHIBA

**Leading Innovation** >>>>