### Application Note: Best Practices for S-Parameter Extraction to Improve Time-Domain Convergence with Allegro Sigrity Tools

November 2013

© 2005-2013 Cadence Design Systems, Inc. All rights reserved.

Printed in the United States of America.

Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA

**Trademarks**: Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522.

All other trademarks are the property of their respective holders.

**Restricted Print Permission**: This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used solely for personal, informational, and noncommercial purposes;

- 2. The publication may not be modified in any way;

- 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

- 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer**: Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights**: Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

### Contents

| Overview                                               | 4  |

|--------------------------------------------------------|----|

| Translation of Cadence Layouts                         | 5  |

| PowerSI GUI Setup                                      | 6  |

| Stackup                                                | 9  |

| Enforce Causality                                      | 10 |

| Per-layer Special Voids                                | 11 |

| Padstacks                                              | 11 |

| Net Management                                         | 13 |

| Trace Coupling                                         | 14 |

| Differential Pairs                                     | 16 |

| Capacitor Models                                       | 17 |

| Trace-to-Via Transitions (Fillets)                     | 18 |

| Ports                                                  | 18 |

| Port Reference Impedance                               | 19 |

| Simulation Frequencies                                 | 20 |

| Simulation Options – BNP Format                        | 21 |

| Simulation Options – CPUs                              | 21 |

| Simulation Options – Special Voids                     | 22 |

| BGA Setup                                              | 23 |

| Flip-Chip Bumps                                        | 23 |

| Wirebond Die Height                                    | 24 |

| Wirebond Encapsulate / Molding                         | 24 |

| Wirebond Conductivity                                  | 24 |

| Wirebond Model Library                                 | 25 |

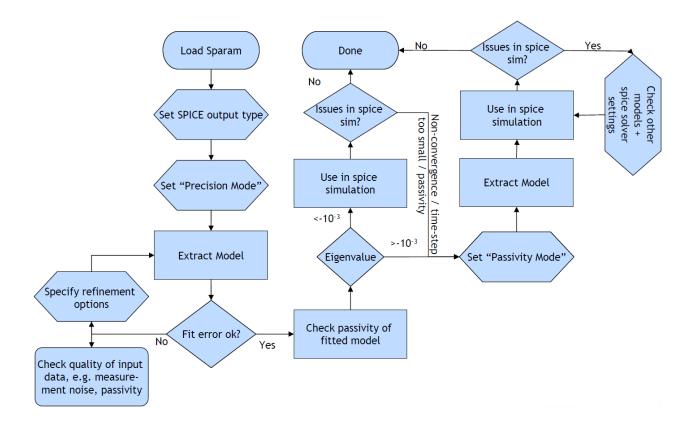

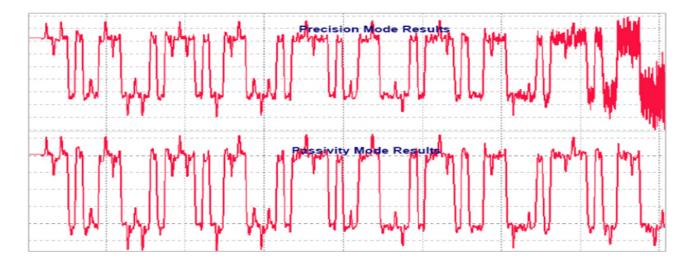

| Precision Mode                                         | 26 |

| Passivity Mode                                         | 26 |

| Broadband SPICE's Output File Formats                  | 27 |

| Using S-Parameters Directly in Time-Domain Simulations | 27 |

| Summary / Checklist                                    | 28 |

### Overview

For Cadence<sup>®</sup> Sigrity<sup>™</sup> SystemSI<sup>™</sup> users, it is common practice to use Cadence Sigrity PowerSI<sup>™</sup> as an extraction engine to produce S-parameter models that are used in SystemSI to build die-to-die topologies. One challenge in such a flow is non-convergence by the time-domain circuit simulator, especially when the S-parameter models involved have a large numbers of ports. There are a number of best practices that have emerged through experience that can make this process more robust. The purpose of this application note is to document those here. They fall into several categories:

- PowerSI recommendations applicable to both PCB and IC packages

- PowerSI IC package setup recommendations

- Wirebonds

- Flip-chip bumps

- BGA balls

- Broadband SPICE conversion recommendations

This document does not cover basic usage of PowerSI and assumes intermediate experience with the tool. New users are encouraged to go through the PDN Impedance Extraction (PowerSI) Rapid Adoption Kit material as a prerequisite. A number of different Allegro<sup>®</sup> Sigrity workshops are also available that introduce PowerSI.

## Section 1: PowerSI Recommendations for PCBs and IC Packages

This section covers steps applicable to both PCB and IC packages:

- Translation options

- Stackup options

- Padstacks

- Net management

- Decoupling capacitor models

- Ports and their reference impedances

- Frequency sweep options

- S-parameter file formats

- Special voids

### **Translation of Cadence Layouts**

The first step is to convert the Cadence database to the Sigrity "SPD" format. Before translation, check the design in Allegro for any short circuits and other design rule checks (DRCs).

Typically the checked boxes below should be selected.

| Sigrity BrdExtractor                              | x                 |

|---------------------------------------------------|-------------------|

| Settings                                          |                   |

| Translate MIXED Layer to: Plane or Signa          | al 🔻              |

| Allow patches on Signal layers                    |                   |

| Distinguish shapes of different nets by color     |                   |

| Add pseudo plane(s) if lack of plane or patch     |                   |

| Append net name to objects                        |                   |

| Include elements with no net names                |                   |

| Create Partial Ckt Names based upon Compor        | nent Part Number  |

| Calculate via plating using "Drill/Slot symbol" v | alues             |

| Split vias into several 2-layer vias              |                   |

| Translate antipads as voids                       |                   |

| Translate only voltage nets                       |                   |

| Treat pad on dielectric layer as drill            |                   |

|                                                   |                   |

| Unionize traces shorter than:                     | 0 mm              |

| Maximum arc length replaced by line segment:      | 0.2 mm            |

| Name affix :                                      |                   |

|                                                   |                   |

| Cadence Extracta Path:                            |                   |

| env File Path:                                    |                   |

| C:\Cadence\SPB_16.6\share\pcb\text\env            | Open              |

| extracta.exe Path:                                |                   |

| C:\Cadence\SPB_16.6\tools\pcb\bin\extracta.e>     | Copen             |

|                                                   |                   |

|                                                   |                   |

| OK Restor                                         | e Settings Cancel |

#### Notes:

Via plating can also be translated if specified in the Allegro database "Drill / Slot symbol" information.

If non-functional pads will not be removed, select option "split vias into several 2-layer vias". Note that this may significantly increase the size of the .spd file.

### **PowerSI GUI Setup**

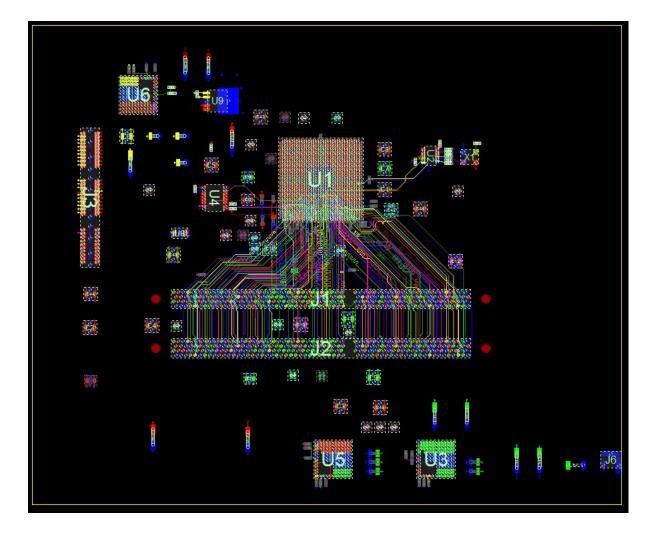

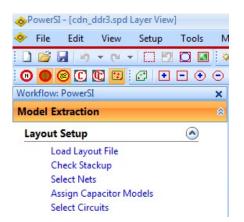

This section will walk through the major steps of the setup.

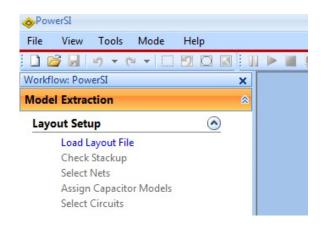

Under the Model Extraction workflow, click Load Layout File.

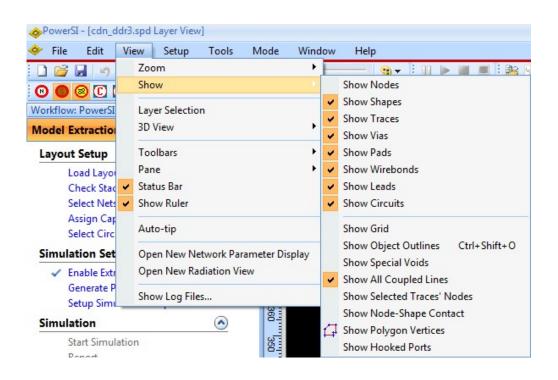

Under View > Show, turn items on or off to match the settings below. These are the typical view settings.

Note that "Show Nodes" is turned off. They are typically only turned on whenever circuits or ports are edited.

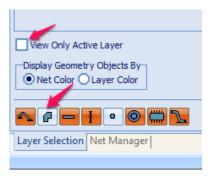

In the Layer Selection window pane, you can *LMB* on the layer name text (NOT the eye icon) to change the active layer.

| Lay | er Selection     | × |

|-----|------------------|---|

| ۲   | Signal\$TOP      |   |

| ۳   | Signal\$GND_2    |   |

| ۳   | Signal\$POWER_3  |   |

| ۳   | Signal\$SIG_4    |   |

| ۲   | Signal\$SIG_5    |   |

| ۳   | Signal\$GND_6    |   |

| ۲   | Signal\$SIG_7    |   |

| ۳   | Signal\$GND_8    |   |

| 9   | Signal\$SIG_9    |   |

| Ð   | Signal\$GND_10   |   |

| Ð   | Signal\$POWER_11 |   |

| Ð   | Signal\$BOTTOM   |   |

You can go through the layers as desired to get familiar with the stackup and routing.

At the bottom of the Layer Selection window pane, you can *clear the check* on *View Only Active Layer* and *disable Show Shapes*. This will show all layers without shapes. This is useful to view only trace routing (see next page).

At the bottom of the Layer Selection window pane, *check View Only Active Layer* and *enable Show Shapes*. This returns the GUI to the typical view settings.

### Stackup

On the Workflow, click *Check Stackup*.

Inside the Stackup window, *change units to mils* with the drop-down selector. Using *shift-LMB or ctrl-LMB* select multiple cells and adjust their values at the same time.

| Layer #     | Color      | Layer Icon    | Layer Name       | Thickness(mil) | Material | Conductivity(S | Fill-in Dielectric | Permittivity                    | Loss Tangent     |

|-------------|------------|---------------|------------------|----------------|----------|----------------|--------------------|---------------------------------|------------------|

| 1           |            |               | Signal\$TOP      | 1.2            |          | 5.959e+007     |                    | [1]                             | [0]              |

|             |            |               | Medium\$41       | 8              |          |                |                    | 4.5                             | 0.035            |

| 2           |            |               | Signal\$GND_2    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$43       | 8              |          |                |                    | 4.5                             | 0.035            |

| 3           |            |               | Signal \$POWER_3 | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$45       | 5              |          |                |                    | 4.5                             | 0.035            |

| 1           |            |               | Signal\$SIG_4    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$47       | 8              |          |                |                    | 4.5                             | 0.035            |

| 5           |            |               | Signal\$SIG_5    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$49       | 5              |          |                |                    | 4.5                             | 0.035            |

| i           |            |               | Signal\$GND_6    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$51       | 8              |          |                |                    | 4.5                             | 0.035            |

| 7           |            |               | Signal\$SIG_7    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$53       | 5              |          |                |                    | 4.5                             | 0.035            |

| 3           |            |               | Signal\$GND_8    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$55       | 8              |          |                |                    | 4.5                             | 0.035            |

| )           |            |               | Signal\$SIG_9    | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$57       | 5              |          |                |                    | 4.5                             | 0.035            |

| .0          |            |               | Signal\$GND_10   | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$59       | 8              |          |                |                    | 4.5                             | 0.035            |

| 1           |            |               | Signal\$POWER_11 | 1.2            |          | 5.959e+007     |                    | [4.5]                           | [0.035]          |

|             |            |               | Medium\$61       | 8              |          |                |                    | 4.5                             | 0.035            |

| 2           |            |               | Signal\$BOTTOM   | 1.2            |          | 5.959e+007     |                    | [1]                             | [0]              |

| •           |            |               | 111              |                |          |                |                    |                                 |                  |

| Total Thick | ness: 9.04 | 100e +001 mil |                  | Thickn         | ess: 5   | Enforce        |                    | ew Material<br>yer Special Void | Import<br>Filter |

### **Enforce Causality**

A frequency-independent material property with non-zero loss tangent is non-causal. In Cadence Sigrity SPEED2000<sup>™</sup> (by default) and in PowerSI (by user option) we apply causal Debye material properties. In PowerSI this Debye model is applied only when the "Enforce Causality" checkbox is selected in the stackup editor.

|                   | 111                        |        |

|-------------------|----------------------------|--------|

| Enforce causality | View Material              | Import |

| Au                | ito Set Layer Special Void | Filter |

| m V OK            | Cancel                     | Apply  |

Permittivity and loss tangent values can be constant or frequency dependent. Click View Material to and then Show Library's Material to see examples.

For the case of non-zero constant loss tangent, we apply a single-pole Debye frequency dependence with an extremely high resonance frequency that does not noticeably change the user-specified permittivity and loss tangent values at user simulation frequencies. The vast majority of customers fall into this category.

For the case of frequency-dependent material specification, we curve fit to a multi-pole Debye behavior to correspond as closely as possible to the user-specified data. There are no knobs for the user to turn other than adding more points to the table. But that's not usually an option unless you're measuring the dielectric materials; otherwise you could be using physically impossible values.

### **Per-Layer Special Voids**

One of the most overlooked capabilities of the Stackup window is the ability to automatically set per-layer special voids. Special voids will be discussed in detail in a later section, but for now know that this option is highly recommended to help automate a more accurate setup. Just click *Auto Set Layer Special Voids*.

| (mm)   | Trapezoidal Angle(°)   | Roughness Upper | Roughness Lower        | RLGC | Dogleg Hole | Thermal Hole  | Small Hole    | Via Hole Thres. |

|--------|------------------------|-----------------|------------------------|------|-------------|---------------|---------------|-----------------|

|        | 90                     | None            | None                   |      | 1.5         | 1.5           | 1.5           | 1.5             |

|        |                        |                 |                        |      |             |               |               |                 |

|        | 90                     | None            | None                   |      | 1.5         | 1.5           | 1.5           | 1.5             |

|        | 90                     | None            | None                   |      | 1.5         | 1.5           | 1.5           | 1.5             |

|        | 90                     | None            | None                   |      | 1.5         | 1.5           | 1.5           | 1.5             |

|        | 90                     | None            | None                   |      | 1.5         | 1.5           | 1.5           | 1.5             |

|        | 90                     | None            | None                   |      | 1.5         | 1.5           | 1.5           | 1.5             |

|        |                        |                 |                        |      |             |               |               |                 |

|        |                        |                 |                        |      |             |               |               |                 |

| otal T | hickness: 1, 1989e+000 | ) mm            | DogLeg Hole Threshold: | 1.5  | Enfo        | rce causality | View Material | Import          |

### Padstacks

For simulation to create the most accurate via models, via plating, pad, and antipad sizes must be defined in the padstack library. Unfortunately pad stacks are not always set up in the layout database as there are multiple ways to define clearances in Allegro tools. It is highly recommended to update the layout database with complete pad stack information if at all possible.

There are two ways to enter data in the padstack library. The "DefaultLibLayer" is an easy way to make the same entries for all layers at once.

| PadStacks 🔺 🕹                                  | ection View | Layer               | PadType | Shape | Width          | Height       | OffsetX    | OffsetY |

|------------------------------------------------|-------------|---------------------|---------|-------|----------------|--------------|------------|---------|

| ~DefaultPadStack                               |             | D DefaultLibLayer   | Regular | Cirde | 0.762          | 0.762        |            |         |

| 16X60                                          |             |                     | Anti    | Cirde | 1.27           | 1.27         |            |         |

| 30X150                                         |             |                     | Thermal |       |                |              |            |         |

| 30X150B                                        |             |                     | Regular |       |                |              |            |         |

| AD60CIR36D                                     |             |                     | Anti    |       |                |              |            |         |

| SMD50_25                                       |             |                     | Thermal |       |                |              |            |         |

| SMD50_87_Mirrd                                 |             | Signal\$GND         | Regular |       |                |              |            |         |

| SMT_TP                                         |             |                     | Anti    |       |                |              |            |         |

| AIV                                            |             |                     | Thermal |       |                |              |            |         |

| AD60SQ36D                                      |             | Signal\$IS3         | Regular |       |                |              |            |         |

| SMD50_63_Mirrd                                 |             |                     | Anti    |       |                |              |            |         |

| 16X60_Mirrd                                    |             |                     | Thermal |       |                |              |            |         |

| 30X150B_Mirrd                                  |             | Signal\$IS4         | Regular |       |                |              |            |         |

| 30X150_Mirrd                                   |             |                     | Anti    |       |                |              |            |         |

| 109                                            |             |                     | Thermal |       |                |              |            |         |

| 109_Mirrd                                      |             | Signal\$VCC         | Regular |       |                |              |            |         |

| PAD60CIR36D_Mirrd                              |             |                     | Anti    |       |                |              |            |         |

| AD60SQ36D_Mirrd                                |             |                     | Thermal |       |                |              |            |         |

| SMD 50_25_Mirrd                                |             | Signal\$BOTTOM      | Regular |       |                |              |            |         |

| SMD 50_63                                      |             |                     | Anti    |       |                |              |            |         |

| SMD 50_87                                      |             |                     | Thermal |       |                |              |            |         |

| SMD60REC40                                     |             |                     |         |       |                |              |            |         |

| SMD60REC40_Mirrd                               |             |                     |         | 10    |                |              |            |         |

| SMT_TP_Mirrd                                   |             | Outer Diameter: 0.4 | 1064    |       | mm             |              |            |         |

| /IA_Mirrd                                      |             |                     |         |       |                |              |            |         |

|                                                |             | Plating thickness:  |         |       | mm (Solid Via) |              |            |         |

| Current default pad stack:<br>~DefaultPadStack |             | Conductivity: 5.8   | 3e7     |       | S/m 🗹 Us       | e default co | nductivity |         |

| Set As Default                                 |             | Select material:    |         |       | -              |              |            |         |

| New Delete                                     |             |                     |         |       |                |              |            |         |

The other option is to specify per-layer values.

### **Net Management**

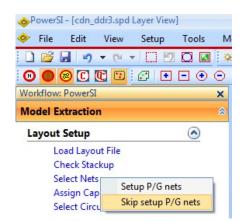

On the Workflow, click **Select Nets**. A pop-up will appear. Select **Skip setup P/G nets** if you know the net names of interest. Choosing Setup P/G nets will open a wizard to identify nets for simulation.

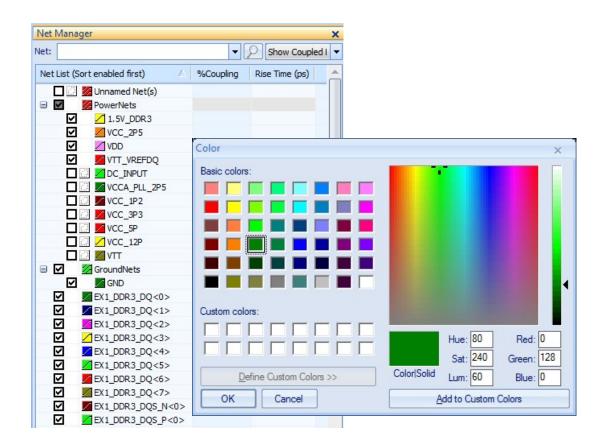

If all nets were translated, it is usually best to first disable all nets and then selectively enable only the nets of interest. It is not common to enable all nets for simulation as that would yield unnecessarily long simulation time. RMB anywhere in the spreadsheet area of the Net Manager and select *Disable All Nets*.

| Enable Selected Nets  |

|-----------------------|

| Disable Selected Nets |

| Enable All Nets       |

| Disable All Nets      |

|                       |

**IMPORTANT:** Note that you can still see the planes in the layout. At the bottom of the Net Manager, *clear the check* for *Keep shape enabled when the net is disabled.*

| General                                     |               |

|---------------------------------------------|---------------|

| Keep shape enabled when the net is disabled |               |

| Gray Disabled                               | Hide Disabled |

When enabled, this option includes all planes in the simulation. This can lead to unacceptably long simulation times. This option is on by default to ensure good results for new users. It is better to take the time to selectively enable the necessary power nets to achieve the best balance between setup time and simulation time.

*Check Hide Disabled* if you don't want to see the disabled nets displayed in gray.

Change the power and ground nets display colors by *LMC* the *colored square* next to the net name. This is typically done to make it easier to identify a net's identity. The PowerSI port display uses red and green icons, so it's best to use *dark green* for the GND net as shown below and **anything other than red** for power nets.

**Classify Net Groups** – **classify at least one net to the Ground Net Group**. This is typically the largest digital ground net of the design. Power nets should be classified to the Power Net Group. These net groups are used by setup wizards such as assign capacitor models, port setup, and port reference impedance. While this step is not technically required, the wizards and automated setups will not work without it.

### **Trace Coupling**

At the top right of Net Manager, click the pull-down and change the view mode to Show Coupled Line.

| N  | et N  | Mana         | iger                |           | ×                                     |

|----|-------|--------------|---------------------|-----------|---------------------------------------|

| Ne | t:    |              |                     | -         | Show Coupled I 🔻                      |

| N  | let l | List (S      | Sort enabled first) | %Coupling | Default Mode<br>Ris Show Coupled Line |

|    | Ŀ     | 2            | 💹 Unnamed Net(s)    |           | Show Volt & P/G                       |

| E  | 0     | 2            | 💯 PowerNets         |           |                                       |

|    |       | $\checkmark$ | 1.5V_DDR3           |           |                                       |

In Hybrid Solvers, there are various switches available to make the computations for large/complex designs more efficient. Trace to trace coupling is one of these switches in Sigrity tools. By default, trace-to-trace couplings are unaccounted for unless the user specifies the Coupled Lines parameters. For many single-ended designs, this is acceptable since most trace couplings fall off quickly with separation distance. When trace coupling was first implemented, we did not want to force every computation to be prohibitively large... especially when large computer resources were costly.

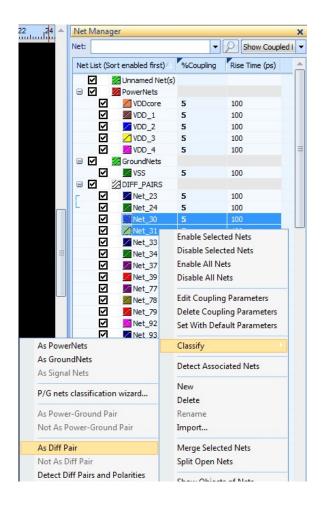

To enable trace coupling, highlight the first signal net with *LMC*. Then group-select all enabled signal nets with *shift-LMC*. Then *RMC* anywhere in the blue highlighted area and select *Set with Default Parameters*.

|                         | EX1 DDR3 DO<0>                                                                                                                                                                                                                                             |                                 |                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------|

| $\overline{\mathbf{V}}$ | EX1_DDR3_DQ<0>                                                                                                                                                                                                                                             | Enable Select                   | ed Nets                                              |

| $\square$               | EX1 DDR3 DQ<2>                                                                                                                                                                                                                                             | Disable Select                  | ted Nets                                             |

|                         | EX1_DDR3_DQ<3>                                                                                                                                                                                                                                             | Enable All Ne                   | ts                                                   |

| $\checkmark$            | EX1_DDR3_DQ<4>                                                                                                                                                                                                                                             | Disable All N                   | ets                                                  |

| $\checkmark$            | <pre>EX1_DDR3_DQ&lt;5&gt;</pre>                                                                                                                                                                                                                            |                                 |                                                      |

| $\checkmark$            | EX1_DDR3_DQ<6>                                                                                                                                                                                                                                             | Edit Coupling                   | Parameters                                           |

| $\checkmark$            | EX1_DDR3_DQ<7>                                                                                                                                                                                                                                             | Delete Coupl                    | ing Parameters                                       |

| $\checkmark$            | EX1_DDR3_DQS_N<0                                                                                                                                                                                                                                           | Set With Defa                   | ult Parameters                                       |

|                         | AFVI DDDD DOC DVD                                                                                                                                                                                                                                          |                                 |                                                      |

|                         | <pre>ZEX1_DDR3_DQS_P&lt;0</pre>                                                                                                                                                                                                                            |                                 |                                                      |

|                         | EXI_DDR3_DQS_P<0                                                                                                                                                                                                                                           |                                 |                                                      |

|                         | EX1_DDR3_DQ<0>                                                                                                                                                                                                                                             | 5                               | 200                                                  |

|                         | EX1_DDR3_DQ<0><br>EX1_DDR3_DQ<1>                                                                                                                                                                                                                           | 5                               | 200                                                  |

|                         | EX1_DDR3_DQ<0>                                                                                                                                                                                                                                             |                                 |                                                      |

|                         | EX1_DDR3_DQ<0><br>EX1_DDR3_DQ<1>                                                                                                                                                                                                                           | 5                               | 200                                                  |

|                         | EX1_DDR3_DQ<0><br>EX1_DDR3_DQ<1><br>EX1_DDR3_DQ<2>                                                                                                                                                                                                         | 5<br>5                          | 200<br>200                                           |

|                         | EX1_DDR3_DQ<0><br>EX1_DDR3_DQ<1><br>EX1_DDR3_DQ<2><br>EX1_DDR3_DQ<2><br>EX1_DDR3_DQ<3>                                                                                                                                                                     | 5<br>5<br>5                     | 200<br>200<br>200                                    |

| NNN                     | EX1_DDR3_DQ<0><br>EX1_DDR3_DQ<1><br>EX1_DDR3_DQ<2><br>EX1_DDR3_DQ<2><br>EX1_DDR3_DQ<3><br>EX1_DDR3_DQ<4>                                                                                                                                                   | 5<br>5<br>5<br>5<br>5           | 200<br>200<br>200<br>200<br>200                      |

|                         | <ul> <li>EX1_DDR3_DQ&lt;0&gt;</li> <li>EX1_DDR3_DQ&lt;1&gt;</li> <li>EX1_DDR3_DQ&lt;2&gt;</li> <li>EX1_DDR3_DQ&lt;3&gt;</li> <li>EX1_DDR3_DQ&lt;4&gt;</li> <li>EX1_DDR3_DQ&lt;4&gt;</li> <li>EX1_DDR3_DQ&lt;5&gt;</li> </ul>                               | 5<br>5<br>5<br>5<br>5<br>5      | 200<br>200<br>200<br>200<br>200<br>200               |

|                         | <ul> <li>EX1_DDR3_DQ&lt;0&gt;</li> <li>EX1_DDR3_DQ&lt;1&gt;</li> <li>EX1_DDR3_DQ&lt;2&gt;</li> <li>EX1_DDR3_DQ&lt;3&gt;</li> <li>EX1_DDR3_DQ&lt;4&gt;</li> <li>EX1_DDR3_DQ&lt;4&gt;</li> <li>EX1_DDR3_DQ&lt;5&gt;</li> <li>EX1_DDR3_DQ&lt;6&gt;</li> </ul> | 5<br>5<br>5<br>5<br>5<br>5<br>5 | 200<br>200<br>200<br>200<br>200<br>200<br>200<br>200 |

The % coupling value is a threshold. Anything larger will be included in simulation. Anything smaller will be discarded to improve simulation efficiency.

The default values of 200ps / 5% are a compromise between simulation time and accuracy. Smaller rise time and lower percentage can be applied for higher accuracy at a cost of longer simulations. Some users never change the values, while others often make the values much smaller (could potentially include <u>much</u> more coupling). There are no precise numerical values we can suggest to assure success; thus, our making available the two high-level specs to control coupling level and selecting a compromise default value for each.

The **coupled lines report** tells/shows you which couplings will be considered in the simulation. It's not an exact science, but if you look at the report and it intuitively seems that some couplings you suspect will be important are missing in a given region of your design, then simply use a lower coupling threshold and/or smaller rise time. After you specify such a low coupling level, it is always a good idea to look at the report before launching off a simulation, since you are at risk of including a LOT of couplings and getting a very slow simulation.

This is further described in the SPD layout user guide under section Show Coupled Lines Mode.

### **Differential Pairs**

PowerSI can optionally calculate and display differential S-parameters. To enable these features, differential pairs must be identified in the Net Manager. Simply *highlight the two nets of a pair, RMB in the blue area > Classify > As Diff Pair.* The diff pair has been classified when a blue bracket appears to the left of the two net names.

### **Capacitor Models**

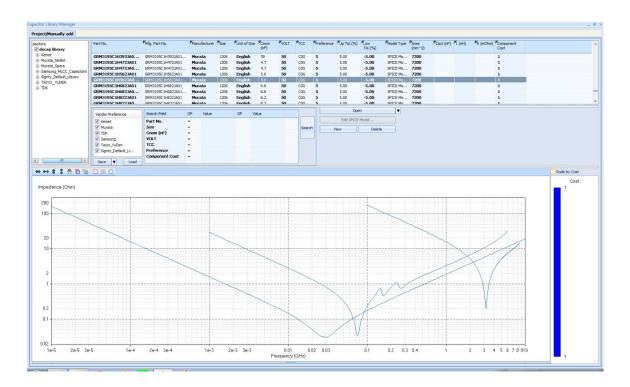

The ASI installation includes thousands of decoupling capacitor models from multiple vendors. Many are measurement-based S-parameters, and these models vary widely in bandwidth. The responses of a few models are shown below as an example.

The simulation frequency range should not extend past the bandwidth of these models; otherwise PowerSI will have to extrapolate model response. Since this extrapolation may or may not be accurate, PowerSI will now warn the user if simulation bandwidth exceeds any S-parameter model's bandwidth. If it is necessary to use this model, it is recommended to lower the simulation bandwidth to match the capacitor model's bandwidth.

A more robust methodology is to use capacitor models built from SPICE elements, such as the Kemet, Murata (net list), and TDK libraries. These models should have valid response from DC to any frequency range appropriate for PowerSI.

### **Trace-to-Via Transitions (Fillets)**

IC package and PCB layout tools have functions to add small transition shapes to the trace-via junctions. These very small shapes can cause difficulties for the shape meshing algorithms. It is highly recommended that these fillets not be added until simulation is complete. If they are present, though, convert them to pads with the Pad <==> Shape Conversion option.

| Max pad   | hape Conversion                                                                                           | Min shape          |                   | 1 | mm |

|-----------|-----------------------------------------------------------------------------------------------------------|--------------------|-------------------|---|----|

| Apply to: | Power/Ground nets                                                                                         | ✓ Signal nets      |                   |   |    |

| solid     | processing,<br>larger than the Max pad siz<br>shapes smaller than the Min<br>gon pads with holes are alwa | shape size (when r | not empty) are co |   |    |

**Shapes Before Conversion**

Shapes After Conversion

### Ports

Net-based ports are automated with the Generate Port(s) wizard. It is most common to use a net-based approach until a more distributed, per-pin approach is mandated. Increasing the number of ports further complicates time-domain simulation, so the general recommendation is to use net-based ports if possible.

### **Port Reference Impedance**

The original Touchstone format only allowed one reference impedance for all ports. Newer formats allow multiple reference impedances. The Network Parameters Options page allows independent settings for power and signal ports reference impedance.

In general, a small reference impedance for PDN ports can yield better results in Broadband SPICE's model conversion process. The idea is to choose a reference impedance near the impedance of the design under test (DUT). For PDN, this is typically a small value. There is no "one" correct/best choice for all situations, but **1 Ohm** and 0.1 Ohm are common choices.

| File 🙆 🚖                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>File Manager<br>Save Options<br>Hotkeys<br>Layout                                                                                                 | Change the 'Network Parameters' options in PowerSI Port Reference Impedance                                                                                                                                                                                                                                                                                                                                                 |

| Grid and Unit<br>View<br>Processing<br>Trace<br>Error Checking<br>3D Layout View                                                                             | Power Nets 1 Ohm<br>Signal Nets 50 Ohm<br>Note: non-uniform port impedance is not support by some third party tools                                                                                                                                                                                                                                                                                                         |

| Display<br>Quality<br>Simulation (Basic) (<br>General<br>Net and Coupling<br>[Network Parameters]<br>Special Void<br>Report<br>Simulation (Advanced) (       | Default Output Format for Network Parameters         ✓ Touchstone 1.0       Frequency unit         ☐ Touchstone 2.0       ✓         ✓ BNP       The BNP format is a binary format that includes the design information, and enables lossless data compression and data encryption. If adaptive frequency sweep is used in the PowerSI simulation, the output file can be very compact comparing with the Touchstone format. |

| Electric Models<br>Field Domain<br>Mesh<br>Reference Handling<br>Nets and Shapes<br>Special Handling<br>Resonance<br>Setting<br>3D FEM<br>Frequency Settings | Auto Save Network Parameters Partial Results Auto save partial results                                                                                                                                                                                                                                                                                                                                                      |

### **Simulation Frequencies**

PowerSI has an **adaptive** sampling algorithm that automatically solves the response between the specified starting and ending frequencies. It is highly recommended to use the Adaptive Frequency Sweep (AFS).

| Starting Freq. | Ending Freq.      | Sweeping Mode | Freq. Increment | Points/Decade |

|----------------|-------------------|---------------|-----------------|---------------|

| Hz             | 10 GHz            | Adaptive      | [               |               |

|                |                   |               |                 |               |

|                |                   |               |                 |               |

|                |                   |               |                 |               |

|                |                   |               |                 |               |

|                | equency Ranges in |               |                 | -             |

Note in the above picture a **Starting Frequency of 0 Hz**. This is a unique feature of the adaptive algorithm. Because field solvers become unstable as they are pushed toward DC, the first frequency that is actually calculated is 1kHz. The AFS algorithm extrapolates results below 1kHz to DC.

While 1kHz is very stable, in general it is not recommended to choose starting frequencies below 1kHz. **Do not choose 1Hz!** The starting frequency MUST be 0Hz to enable the AFS extrapolation.

To choose ending frequency, many users apply: Fmax = 0.35 / rise time

For more information on the derivation of this formula, please see: https://en.wikipedia.org/wiki/Rise time

To further improve the low-frequency accuracy, in the Field Domain Options window, enable **Calculate DC point as reference**. This will run Cadence Sigrity PowerDC<sup> $^{\text{M}}$ </sup> as a part of the PowerSI simulation to very accurately calculate the S-parameters' DC point.

Note: this option is not recommended for PCBs with large bulk decaps included in the PDN. Large bulk decaps cause low-frequency resonances that can be difficult to merge with PowerDC data. For those situations, if this option is desired it is recommended to disable the bulk decap and put a port at its location instead.

#### **PowerDC Option**

Calculate DC point as reference

### **Simulation Options – BNP Format**

Sigrity's Broadband Network Parameter (BNP) format was created to overcome the limitations of the original Touchstone format. One of the main reasons S-parameters can fail in time-domain simulation is due to extrapolation of data between Touchstone sampled points. These extrapolated points can fail passivity and / or causality, resulting in a non-convergent time-domain result.

BNP has many benefits to improve time-domain convergence. If used with PowerSI Adaptive Frequency Sweep, BNP will store equation-based data that has response at any frequency between the minimum and maximum frequency sweep settings of PowerSI. This completely eliminates extrapolation problems. In addition to being more robust, the BNP file size is also much smaller; the file size savings increases as the number of ports increases. Some SPICE simulators have implemented native support for BNP, including HSPICE.

Note that Sigrity offers a free BNP viewer, and BNP data can be down-converted to sampled Touchstone data.

| Default Output Format for I       | Network Parameters        |                                                                                                          |

|-----------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------|

| Touchstone 1.0 Touchstone 2.0 BNP | Frequency unit            | Hz                                                                                                       |

|                                   | ency sweep is used in the | nformation, and enables lossless data compression and<br>PowerSI simulation, the output file can be very |

### **Simulation Options – CPUs**

PowerSI can utilize multiple CPUs during some phases of the simulation. PowerSI can also utilize multiple computers for distributed simulation. This is mentioned simply to encourage users to allocate as many resources as possible to the simulation.

| Multiple CPU usage                             |        |   |  |

|------------------------------------------------|--------|---|--|

| Maximum number of CPU to use in the simulation | 8      | • |  |

| Simulation Process Priority                    | Normal | - |  |

### **Simulation Options – Special Voids**

Special voids are negative metal shapes that are not included in the simulation. These are very small geometries that can be ignored in an effort to improve simulation time. These adjustments can make simulations more accurate if used correctly or less accurate if used incorrectly. There is not one "correct" setting for special voids.

Without special voids, vias and their "breakout traces" do not have references. The vias are not in a field domain, so their coupling cannot be accurately calculated. At minimum, special void criteria should be set larger than single-ended and power/ground vias' antipad sizes.

The default size of 1.5mm is for IC package applications. Build-up packages with large core vias may need larger criteria. The larger vias and antipads of PCBs require larger special voids settings. It is common for PCBs to set all special void criteria up to 5mm, depending on the size of via antipads being used.

| Change the 'Sp                                                  | pecial Vo     | id' options in PowerSI                                                                                                                         |

|-----------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Exclude special voids fi                                        | rom the si    | mulation                                                                                                                                       |

| Dogleg hole smaller than                                        | 1.5           | mm                                                                                                                                             |

| Thermal hole smaller than                                       | 1.5           | mm                                                                                                                                             |

| Small hole smaller than                                         | 1.5           | mm                                                                                                                                             |

| Via hole smaller than                                           | 1.5           | mm                                                                                                                                             |

|                                                                 |               |                                                                                                                                                |

|                                                                 |               |                                                                                                                                                |

|                                                                 |               | apes that are not included in the simulation since they are too small.<br>Table number to balance the result accuracy and resource usage. Also |

| if you see a few circuit or tr<br>size to cover more circuit no | ace reference | te errors in the run time error log file, try to increase the special void                                                                     |

# Section 2: PowerSI Recommendations for IC Packages

This section will provide recommendations that are specific to IC package designs. Note that Cadence Sigrity XtractIM<sup>™</sup> is dedicated to IC packages and automates most of this section's recommendations. XtractIM also completely automates the S-parameter conversion to SPICE-based models. For most IC package applications, XtractIM is highly recommended instead of the PowerSI + Broadband SPICE flow.

### **BGA Setup**

Most packages are drawn in Allegro APD/SiP without vias to represent the balls – this is the recommended flow. During package model extraction, however, it is usually desired to include the ball parasitics in the package model. Therefore, vias to represent the balls must be added in PowerSI.

There is an automated GUI for this step under **File > Merge > Pseudo PCB**. Select the BGA circuit, enter the ball physical properties, and click OK. Optional: assign the added plane to the GND net and set all GND vias' node contact = 1 in order to connect them to the plane.

|           |             |                    | 1                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-------------|--------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ckt Model | Num of pins | Layer              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BGA       | 529         | Signal \$BOTTOM    | Connection Method-                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DIE       | 537         | Signal\$TOP        | Add solder balls                           | O External M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1CP O Short Circ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |             |                    | Height: 1.0000e+002                        | 2 Radius: 2.500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0e+002 Unit: um                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |