# **Accurate Modelling of PCIe® 3.0** Analog Buffers

PCI

Shivani Sharma Design Engineer II Cadence Design Systems

© 2015 Cadence Design Systems, Inc. All rights reserved. Used by PCI-SIG under license.

### Presentation Disclaimer: All opinions, judgments, recommendations, etc. that are presented herein are the opinions of the presenter of the material and do not necessarily reflect the opinions of the PCI-SIG<sup>®</sup>.

- Problem Statement

- Overview of IBIS-AMI Modeling

- Accurate Modeling of PCIe<sup>®</sup> SerDes IO for 16Gbps or Higher Speeds

- Using Parameterized AMI Blocks

- ✓Using Virtual Reference Design (VRD) Flow for Quick Sign-off

- Conclusion

- Problem Statement

- Overview of IBIS-AMI Modeling

- Accurate Modeling of PCIe SerDes IO for 16Gbps or Higher Speeds

- Using Parameterized AMI Blocks

- ✓ Using Virtual Reference Design (VRD) Flow for Quick Sign-off

- Conclusion

**Problem Statement**

- PCIe 3.0 and other current and future high speed protocols require complex equalization schemes to open the eye at the receiver sampler

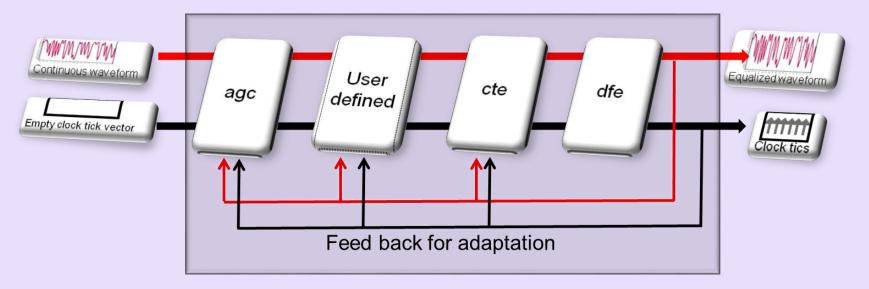

- These equalizers (AGC, CTE, DFE, etc.) interact with each other during adaptation

- Managing this sequence of events can be challenging

- Correlation is even more challenging

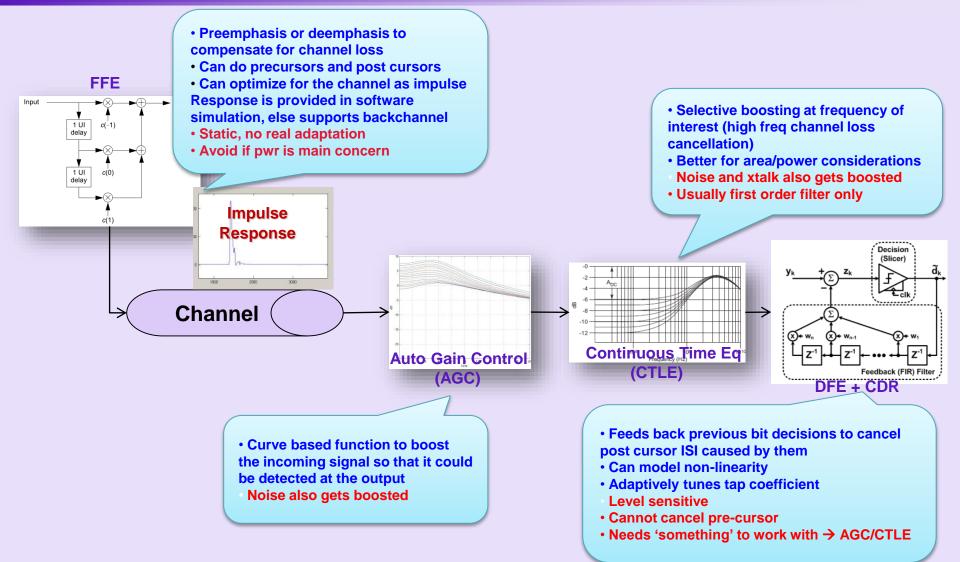

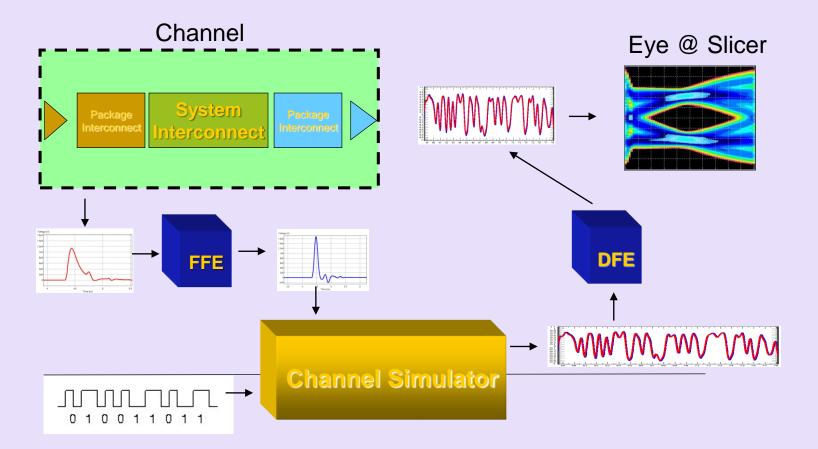

## **Channel Simulation; EQ Basics**

SIG

© 2015 Cadence Design Systems, Inc. All rights reserved. Used by PCI-SIG under license.

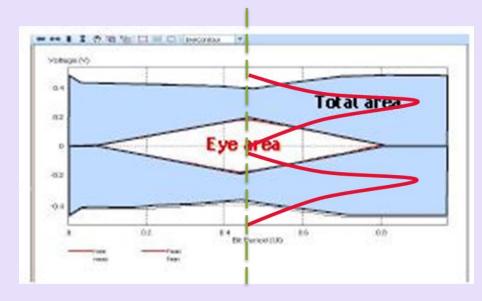

## **Objectives of Equalization**

Maximize SNR

- Done by reducing the area/spread of the PDF

- Auto DFE figures out the peak and tries to maximize the peak

- Focus on the center, works better in xtalk minimization

- ✓ Digitally aware

- CTE follows the DFE

- Analog (indirectly sharpens IR)

- ✓ Cheap/less power/area

- Can amplify noise

- VGA amplifies the target to achieve the target

- Which also amplifies the noise

- Lower dv\_target the better for noise

Lower dv\_target the better for noise

- IF the Rx can detect (Tradeoff)

- Problem Statement

- Overview of IBIS-AMI Modeling

- Accurate Modeling of PCIe SERDES IO for 16Gbps or Higher Speeds

- Using Parameterized AMI Blocks

- ✓ Using Virtual Reference Design (VRD) Flow for Quick Sign-off

- Conclusion

## AMI > Algorithmic Modeling Interface

- Extension made to IBIS in 2007

- Cadence at the forefront of driving AMI through the standardization process

- Enables executable, software-based, algorithmic models to work together with traditional IBIS circuit models

- ✓ Allows deeper access to on-chip technology/secret sauce

- Enables SerDes adaptive equalization algorithms to be modeled and used during channel simulation

- ✓ Fast, accurate and flexible

## **Motivation for AMI**

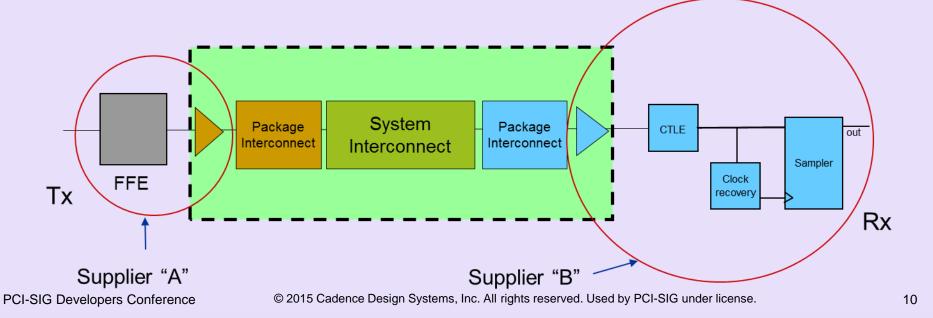

- Interoperability: IBIS-AMI allows plug-and-play simulation compatibility between SerDes models from different suppliers, in a standard commercial EDA format.

- IP Protection: Shared Objects (dlls) are compiled. EDA tool communicates with the dll using the standardized API.

- Flexibility: The Model Maker can use any high level programming language (ex C) to describe the eq at both ends.

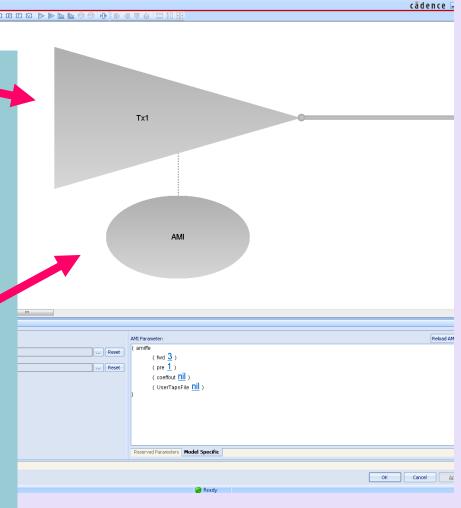

## IBIS-AMI Model Sub-Components

<sup>44</sup> File Edit View Setup Tools Compliance Window Help ] 알 내 키 ▼ ♥ ▼ 18 33 1 19 1 1 1 ▶ ■ 1 35 17 33 18 18 18 18 19 10 ▶ ▶ № № ® ® 카이트 리 파 & 금 취 용

- Circuit part

- ✓ IO buffer stage

- ✓ Voltage swing

- Parasitics

- Spice or traditional IBIS format

- Algorithmic part

✓ On-chip

- Equalization functionality

- ✓ DLL + AMI file

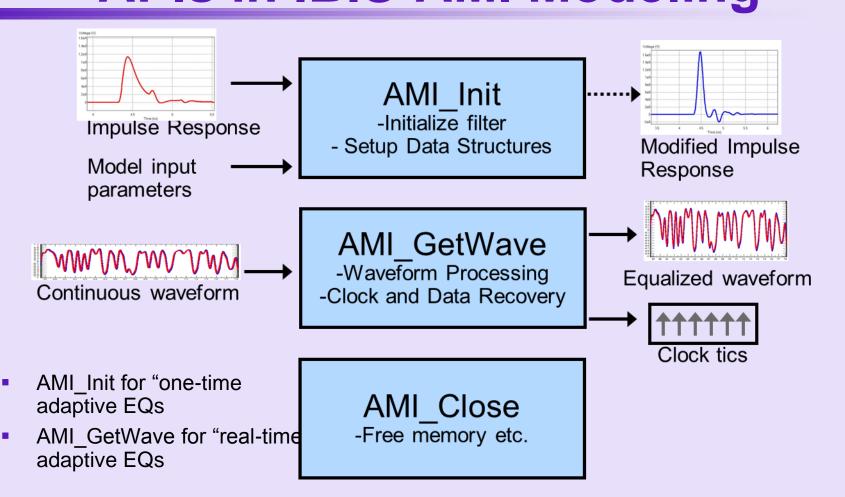

**APIs in IBIS-AMI Modeling**

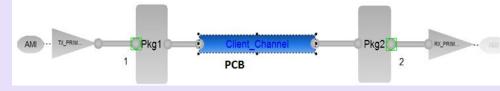

### IBIS-AMI and Channel Simulation

- Problem Statement

- Overview of IBIS-AMI Modeling

- Accurate Modeling of PCIe SerDes IO for 16Gbps or Higher Speeds

- Using Parameterized AMI Blocks

- Using Virtual Reference Design (VRD) Flow for Quick Sign-off

- Conclusion

- SerDes transmitter and receiver modules

- ✓ Transmitter

- FFE

- Edge-boost

- TX matching network

- Receiver

- Rx matching network

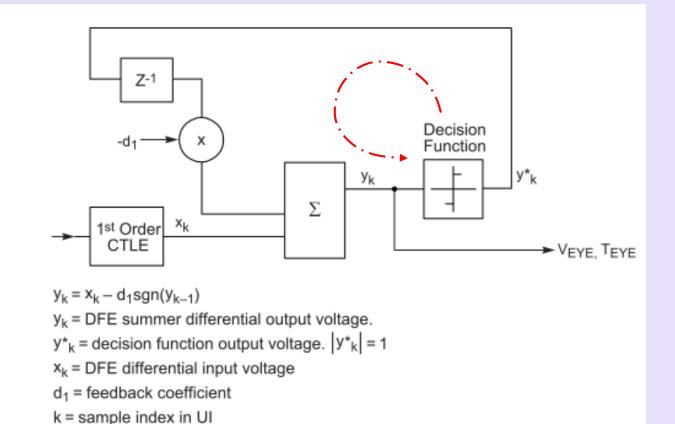

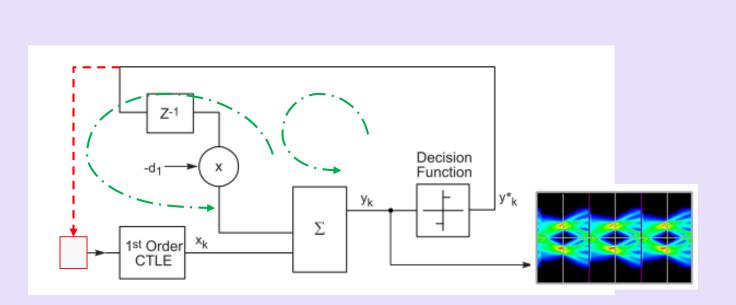

- Continuous-time linear equalizer (CTLE)

- Variable gain amplifier (VGA)

- Decision feedback equalizer (DFE)

- Clock and data recovery (CDR)

### Tx AMI

- FFE is modelled as C code

- Boost circuit characterized by step response

- Tx matching network characterized by step response

### RX AMI

- Tx matching network characterized by step response

- ✓ CTLE, VGA are characterized by step responses

- ✓ DFE, CDR are modelled as C code

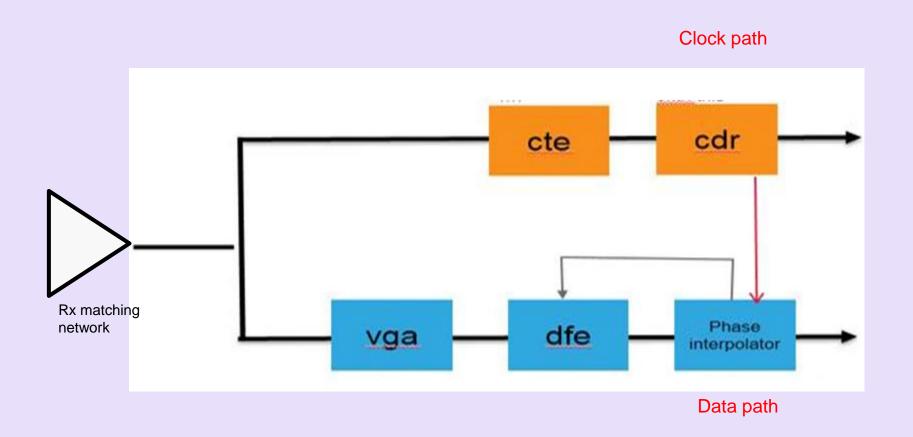

- Data path and a parallel clock path

### Use s-parameters to model matching network in analog portion

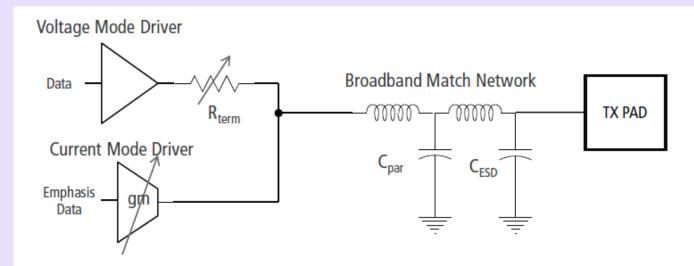

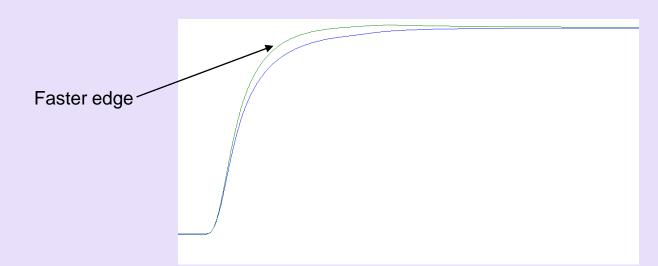

- Boost circuit is implemented at Tx side to improve rise/fall time of the signal

- Boost circuit is a current-mode driver present in parallel with the voltage mode driver module

Fig5: Tx Edge-boost circuit in parallel path

© 2015 Cadence Design Systems, Inc. All rights reserved. Used by PCI-SIG under license.

### • Modeling Boost effects as IR or s-parameters

- Input signal is differentiated and fed to a voltagecontrolled current source. Rise/fall time is improved by pumping extra current at the Tx output node.

- Assuming boost circuit is linear, enable boost and characterize Tx while terminating in reference impedance. (Repeat steps 1 and 2)

# Accurate Modeling of PCle See SERDES IO Using AMI Blocks

- High level of architectural abstraction

- Extremely powerful and flexible

- Capability to model Tx/Rx end to end

- Parameterized blocks

4-0830

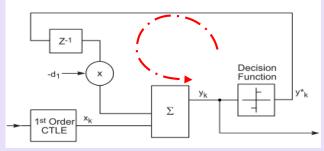

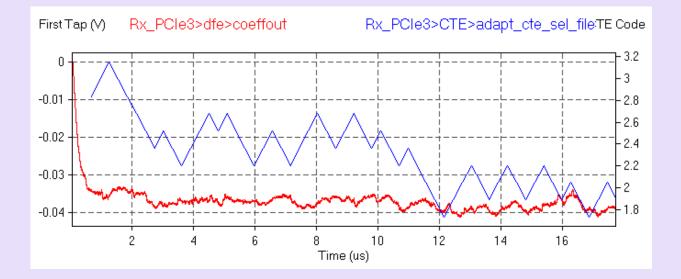

## CTE Adapting with Other Metrics (Ex SNR)

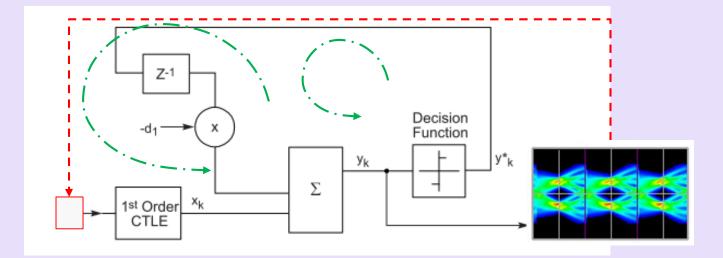

Adaptation can get complex with multiple blocks adapting affecting each other

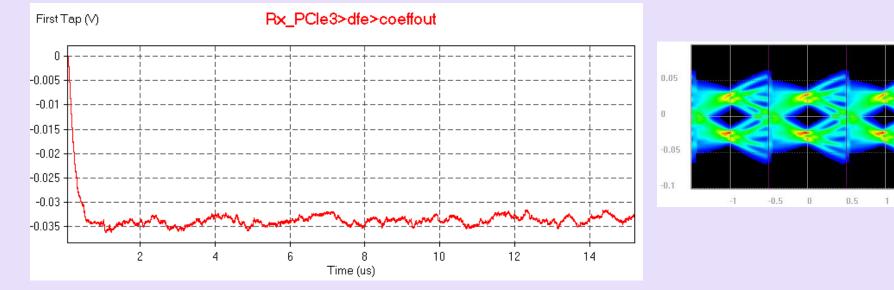

# DFE Only Adaptation at 16Gbps

CTE Adaptation based on SNR

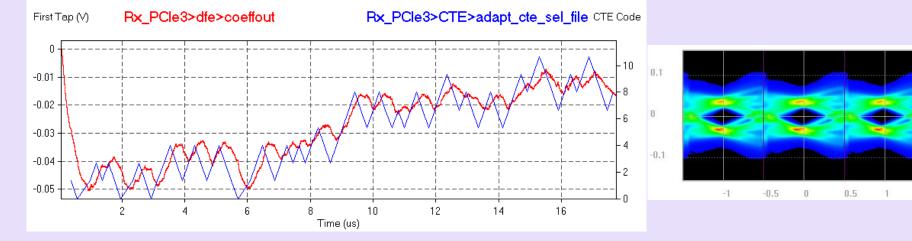

## Adapting CTE May Throw the DFE Off

### CTE Adaptation based on SNR

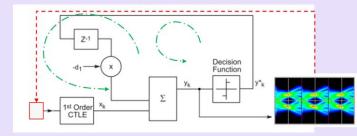

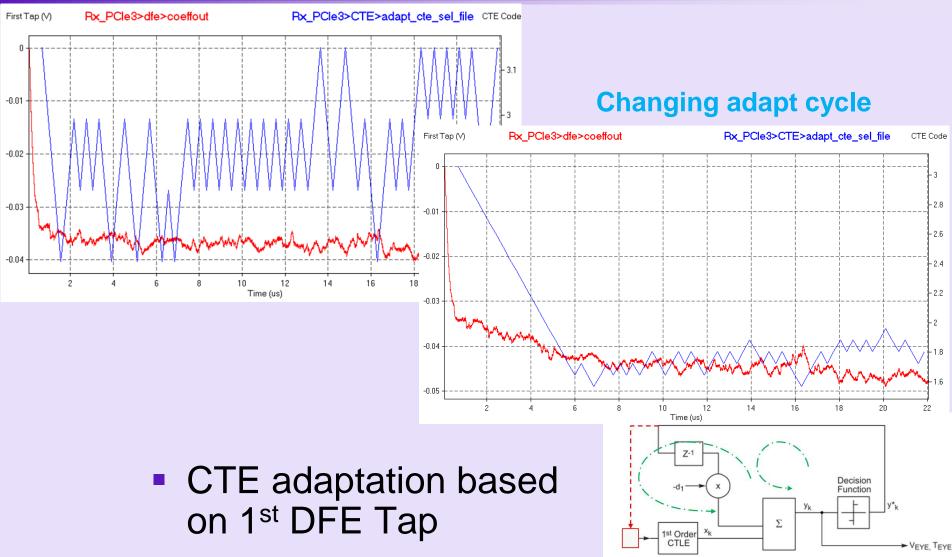

# Changing CTE Adaptation

### Making the adapt cycle slower may be beneficial

# Effects of Changing Constant Adaptation Algorithm for CTE

© 2015 Cadence Design Systems, Inc. All rights reserved. Used by PCI-SIG under license.

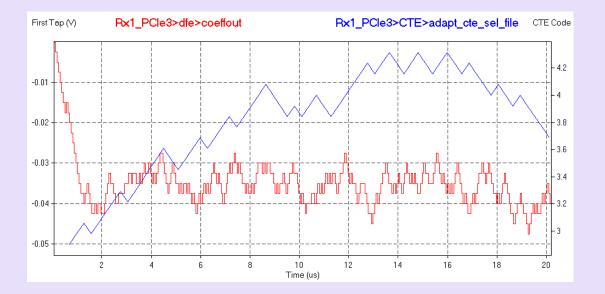

## Digital DFE and Adding Adapting AGC Effects DFE

- Digital DFE only updates after 1024 bits instead of every bit (analog).

- Generally takes longer to finish adapting

# Parallel Clock Path and Data Path

- Problem Statement

- Overview of IBIS-AMI Modeling

- Accurate Modeling of PCIe SerDes IO for 16Gbps or Higher Speeds

- Using Parameterized AMI Blocks

- ✓ Using Virtual Reference Design (VRD)

Flow for Quick Sign-off

- Conclusion

## What's in a VRD (Design-in Kit)?

### A virtual reference design

✓ All the stuff in here:

#### Is modeled here:

Measurement results are replaced with simulation results

### And simulated/ measured here:

## What's in a VRD?

- Parameterized AMI blocks to quickly model various architectures

- Pre-created test-benches to quickly simulate as per compliance

- ✓ Ability to switch channel models

- Ability to quickly transfer PCB/Package model into the test-bench

- Can estimate Package for given nets and Package size

- Run simulations and get compliance reports

| Tools <u>H</u> elp                | cādence                                   |                                                                                                    |                                                                                                      |

|-----------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Virtual Reference Design Platform | Package Layer Estimator<br>DDR Compliance | •                                                                                                  |                                                                                                      |

| Padstack                          | Serdes Compliance with CDN IP M           | odels 🕖 🚺 Check Compliance                                                                         | e                                                                                                    |

| P <u>a</u> d                      | д <b>- х</b>                              | Check Compliance                                                                                   | e Help                                                                                               |

|                                   | Se                                        | erdes Compliance with CDN IP<br>lect Serial Protocol<br>lect Working Directory<br>Launch Testbench | pcie_gen3<br>10_gkr<br>mipi_dphy<br>mipi_mphy<br>pcie_gen1<br>pcie_gen2<br>pcie_gen3<br>pon<br>usb_2 |

#### Choose compliance item

|                    | 1                          |                 |                   |                     | 1                             |                                          |          |                                      |                                |          |           |  |  |

|--------------------|----------------------------|-----------------|-------------------|---------------------|-------------------------------|------------------------------------------|----------|--------------------------------------|--------------------------------|----------|-----------|--|--|

| No.                | Parameter Symbol           |                 |                   |                     |                               | 1                                        |          |                                      |                                |          |           |  |  |

| Channel            | Tolerancing                | g Eye Mask V    | Values (table 4-2 | 27 in PCI Expres    | s Base s                      | spec.)                                   |          |                                      |                                |          |           |  |  |

| 1                  | Eye Height                 |                 |                   |                     | V <sub>RX-CH-EH</sub>         |                                          |          |                                      |                                |          |           |  |  |

| 2                  | Eye Width at Zero Crossing |                 |                   |                     | T <sub>RX-CH-EW</sub>         |                                          |          |                                      |                                |          |           |  |  |

| 3                  |                            |                 |                   |                     |                               | T <sub>RX-DS-OFFSET</sub>                |          | Pkg2                                 | RX_PRIM                        |          |           |  |  |

| 4                  |                            |                 |                   |                     |                               | V <sub>RX-DFE-COEFF</sub>                |          | 2                                    |                                |          |           |  |  |

| 5                  |                            |                 |                   |                     |                               |                                          | <b>V</b> | 2                                    |                                |          |           |  |  |

| Differen           | tial Insertio              | n Loss (figure  | e 4-66 in PCI Ex  | press Base spec     | .)                            |                                          |          |                                      |                                |          |           |  |  |

| 6                  | i Insertion Loss           |                 |                   |                     | SDD21                         |                                          |          |                                      |                                |          |           |  |  |

| Differen           | tial Return                | Loss (figure 4  | -56 in PCI Exp    | ress Base spec.)    |                               |                                          |          |                                      |                                |          |           |  |  |

| 7                  | Tx Return Loss             |                 |                   | RL - Tx             |                               | <b>V</b>                                 |          |                                      |                                |          |           |  |  |

| 8                  | Rx Return Loss             |                 |                   |                     | RL - Rx                       |                                          |          |                                      |                                |          |           |  |  |

| Stressed           | /Swept Jitte               | er Test (figure | e 4-74 in PCI Ex  | press Base spec     | .)                            | Channel Tolerancin                       | g Eye Ma | ask Values                           |                                |          |           |  |  |

| 9                  | Stressed/Swept Jitter      |                 |                   |                     |                               | Item                                     |          | Value                                | Simulation Re                  | esults   | Pass/Fail |  |  |

|                    |                            |                 |                   |                     | •                             | Eye Height                               |          | 25 mV                                | V <sub>RX-CH-EH (mV)</sub>     | 100.821  | Pass      |  |  |

|                    |                            |                 |                   |                     |                               | Eye Width at Zero Crossing               |          | 0.3 UI                               | T <sub>RX-CH-EW (UI)</sub>     | 0.425    | Pass      |  |  |

| me: Client_Channel |                            |                 |                   |                     | Peak EH Offset from UI Center |                                          | ±0.1 UI  | T <sub>RX-DS-OFFSET (UI)</sub>       | -0.031                         | Pass     |           |  |  |

| 1. Port            | Connect To                 | Block Name      | Conn. Port        |                     |                               | Range for DFE d <sub>1</sub> Coefficient |          | ±30 mV                               | V <sub>RX-DFE-COEFF (mV)</sub> |          |           |  |  |

|                    |                            | Pkg1            | pkg_to_pcb        | Edit Layout Linkage | 2                             | Eye Mask                                 |          |                                      | Eye Mas                        | <u>k</u> | Pass      |  |  |

|                    | •••                        | Pkg2            | PCB               | Edit Layout Linkage |                               | Differential Insertion Loss              |          |                                      |                                |          |           |  |  |

|                    |                            |                 |                   |                     |                               | Item                                     |          | Value                                | Simulation Results             |          | Pass/Fail |  |  |

|                    |                            |                 |                   |                     |                               |                                          |          | Breakout Channel Only                | <u>SDD21 - Br</u>              | eakout   | Fail      |  |  |

|                    |                            |                 |                   |                     |                               | Insertion Loss                           |          | Breakout + Short Calibration Channel | SDD21 - Short                  |          | Fail      |  |  |

|                    |                            |                 |                   |                     |                               |                                          |          | Breakout + Long Calibration Channel  | <u>SDD21 - I</u>               | Long     | Pass      |  |  |

|                    |                            |                 |                   |                     |                               | Differential Return                      | Loss     |                                      |                                |          |           |  |  |

|                    |                            |                 |                   |                     |                               | Item                                     |          | Value                                | Simulation R                   | esults   | Pass/Fail |  |  |

|                    |                            |                 |                   |                     |                               | Tx Return Loss                           |          |                                      | <u>RL - T</u>                  | x        | Pass      |  |  |

|                    |                            |                 |                   |                     | Rx Return Loss                |                                          |          | RL - R                               | x                              | Pass     |           |  |  |

© 2015 Cadence Design Systems, Inc. All rights reserved. Used by PCI-SIG under license.

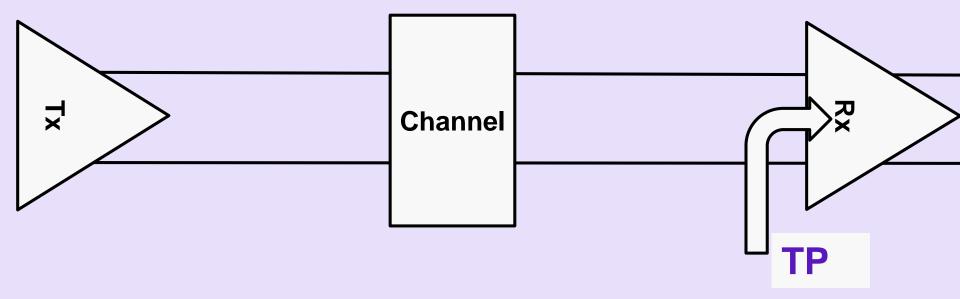

**Correlation Techniques**

Three level of correlations

SIG

Block by block correlations against transistor level simulations

Adaption tests against behavioral simulations

Tx to Rx link simulations and correlations against Hardware lab measurements

#### Design

- ✓ 16Gbps serial link-PCIe 4.0

- ✓ 16 FinFET technology node

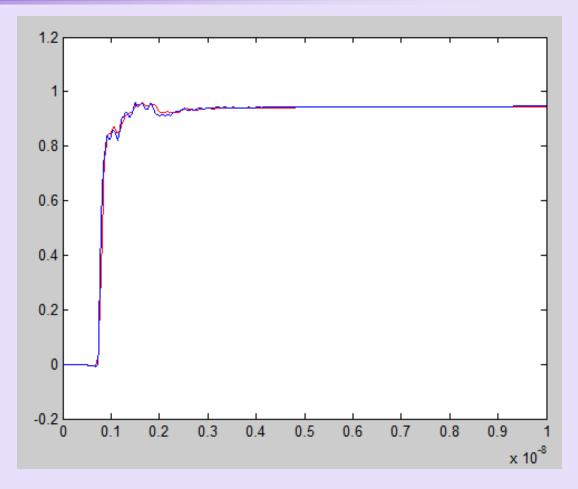

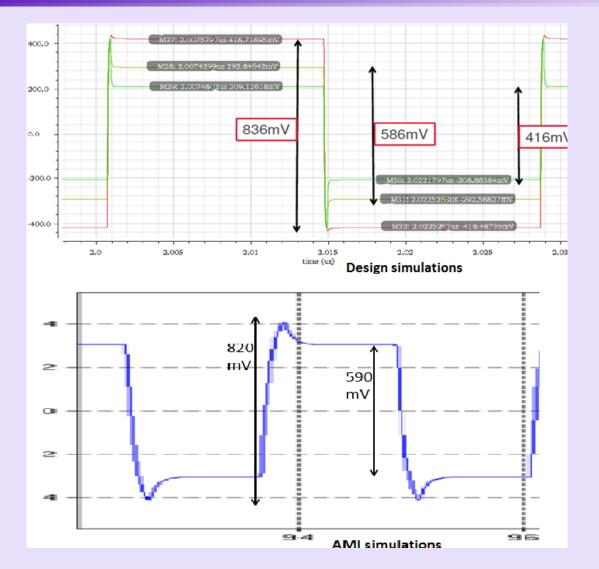

## **Correlation Results - 1**

#### Testing Analog portion - Step response at TP

**Red-Using S-params Blue-Design simulation**

# **Correlation Results - 2**

Testing preemphasis and boost

PCI

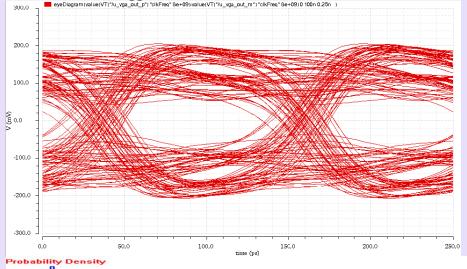

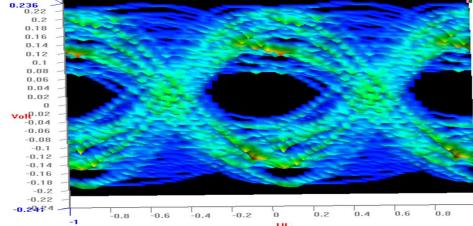

## **Correlation Results - 3**

#### Modelling non-linear VGA

0.061 0.236 0.2

#### **Design Simulation**

Eye Amplitude:392mV Eye Height:117mV Jitterpp:0.35UI 800 bits

#### Model simulation

Eye Amplitude:409mV Eye Height:115mV Jitterpp:0.37UI 100,000 bits

SIG

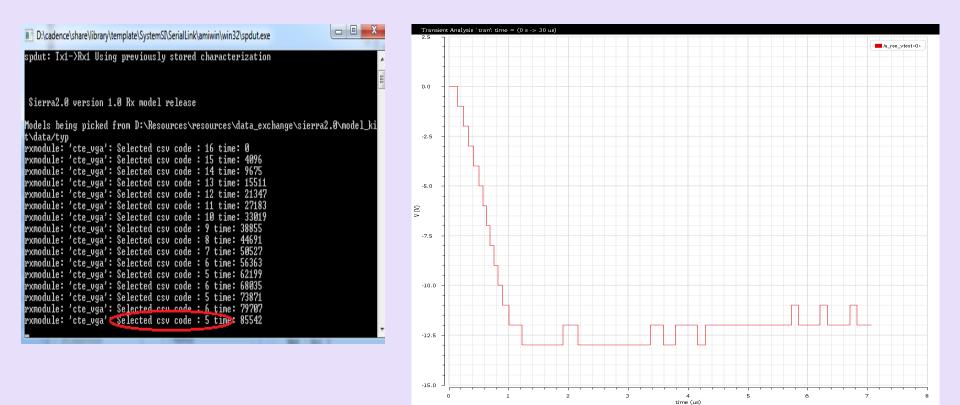

## **Correlation Results - 4**

### VGA adaptation

### ✓ VGA codes 0 to 16 for different VGA settings

- Problem Statement

- Overview of IBIS-AMI Modeling

- Accurate Modeling of PCIe SerDes IO for 16Gbps or Higher Speeds

✓ Our methodology

- Using Virtual Reference Design (VRD) Flow for Quick Sign-off

- Conclusion

- Need parameterized AMI blocks

- To quickly build AMI models to mimic hardware

- Allow electrical engineer designer to create AMI models who knows little programming

- Need a flow that allows rapid building of testbenches to cover various correlations at level of:

- Transistor level simulations

- Architecture level simulations

- Hardware lab measurements

- http://www.eda.org/ibis/

- Eric Naviasky, "Defining a New High-Speed, Multi-Protocol SerDes Architecture for Advanced Nodes" <a href="http://ip.cadence.com/knowledgecenter/resources/knowdip-wp>">http://ip.cadence.com/knowledgecenter/resources/knowdip-wp></a>

PCI

## **Acknowledgements**

- Taranjit Kukal

- Ritabrata Bhattacharya

- Steve Williams

- Eric Naviasky

- Ken Willis

- Kumar Keshavan

- Ambrish Varma

- Jasleen Ahuja

# Thank you for attending the PCI-SIG Developers Conference 2015.

### For more information please go to www.pcisig.com