cādence

##

METHODOLOGY FOR ANALYZING AND QUANTIFYING DESIGN STYLE CHANGES AND COMPLEXITY USING TOPOLOGICAL PATTERNS JASON CAIN<sup>1</sup>, YA-CHIEH LAI<sup>2</sup>, FRANK GENNARI<sup>2</sup>, JASON SWEIS<sup>2</sup> <sup>1</sup>ADVANCED MICRO DEVICES, <sup>2</sup>CADENCE DESIGN SYSTEMS

**TOPOLOGICAL PATTERN DESCRIPTION**

LAYOUT PATTERN EXTRACTION

TOPOLOGICAL LAYOUT COMPARISON

SUMMARY

2 | SPIE ADVANCED LITHOGRAPHY | FEBRUARY 24, 2016

## INTRODUCTION

- Pattern matching engines have been available in the IC physical design ecosystem for over a decade.

- ▲ The use of pattern matching to augment design-rule checking (DRC) in the physical verification flow has been widely adopted.

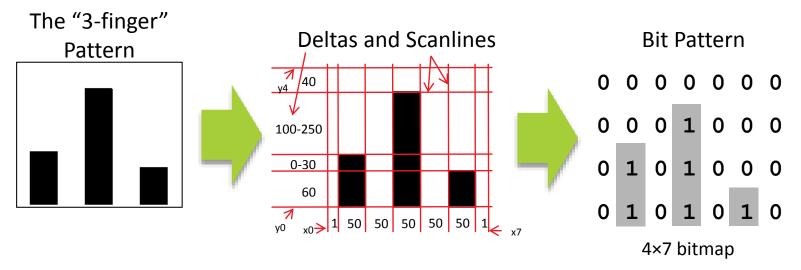

- Early pattern matching engines used a three-value logic (TVL) method for describing patterns.

- The more recent introduction of topological-based pattern matching engines has opened a range of new applications for layout analysis.

## TOPOLOGICAL PATTERN DESCRIPTION

##

- A powerful tool for characterizing and comparing physical designs

- Compact form for describing patterns

- Can be independent of physical dimensions

## TOPOLOGICAL PATTERNS CAN BE USED FOR ANALYSIS

- 1. Understand usage of patterns in your designs (with locations)

- 2. Identify common cases (which must yield well) and outliers/edge cases

- 3. Identify what is new/different in an incoming design

#### 5 | SPIE ADVANCED LITHOGRAPHY | FEBRUARY 24, 2016

## LAYOUT PATTERN EXTRACTION

##

cādence

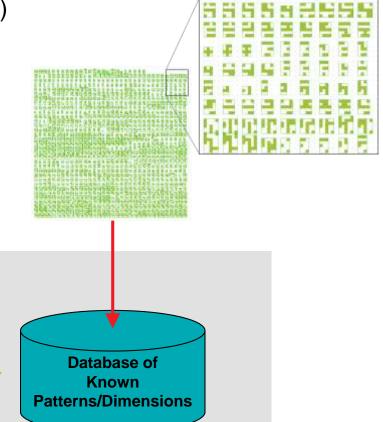

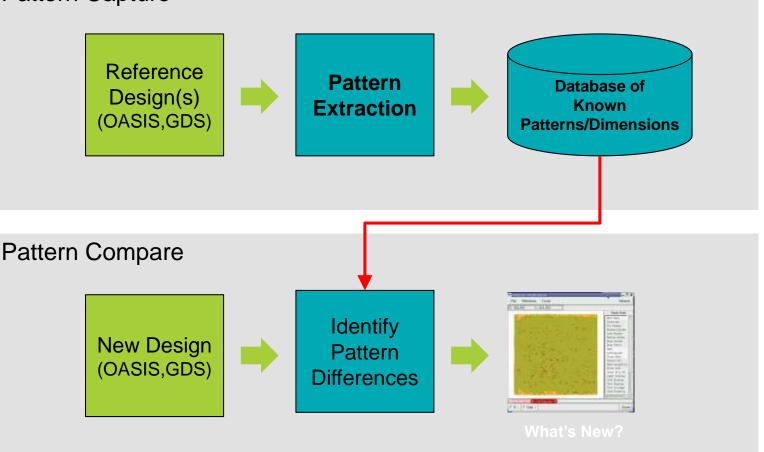

- 1. Systematically scan a window across entire design (choice of window size is important!)

- In every window, break-down and identify <u>every</u> pattern and sub-pattern that exists in that design (with <u>dimensions</u>)

- 3. Store a full catalog of all patterns with dimensions

▶ In our experiments, full chip 1X Metal layers captured in < 8 hours w/ 32 CPUs

Pattern

**Extraction**

6 | SPIE ADVANCED LITHOGRAPHY | FEBRUARY 24, 2016

Reference

Design(s)

(OASIS,GDS)

Pattern Capture

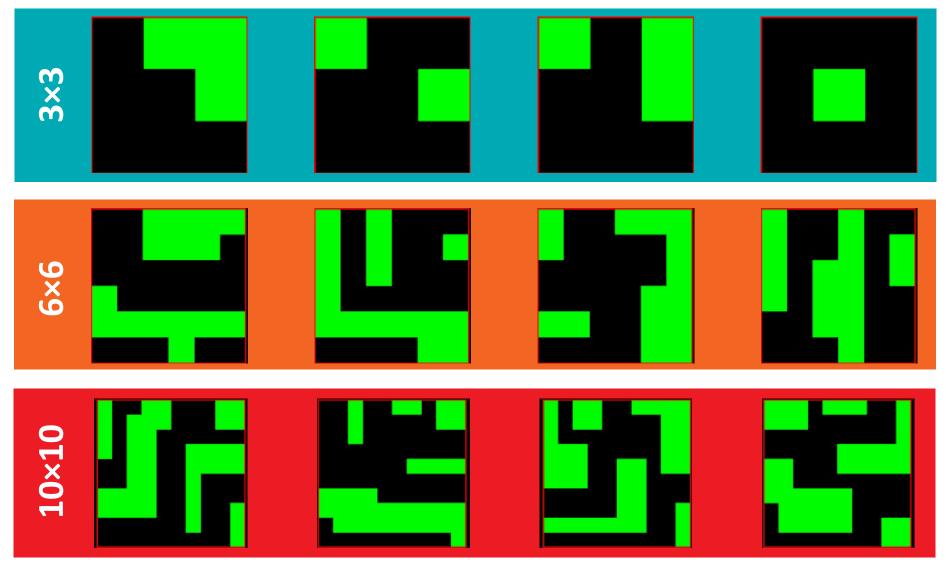

## **TOPOLOGICAL PATTERN EXAMPLES FOR MX LAYERS** 14NM DIGITAL LOGIC – WINDOW SIZE = 3 METAL PITCHES

7 | SPIE ADVANCED LITHOGRAPHY | FEBRUARY 24, 2016

## cādence

## PATTERN EXTRACTION FOR 14NM DIGITAL LOGIC 1X METAL LAYERS, WINDOW SIZE = 3 METAL PITCHES, INEXACT MATCHES

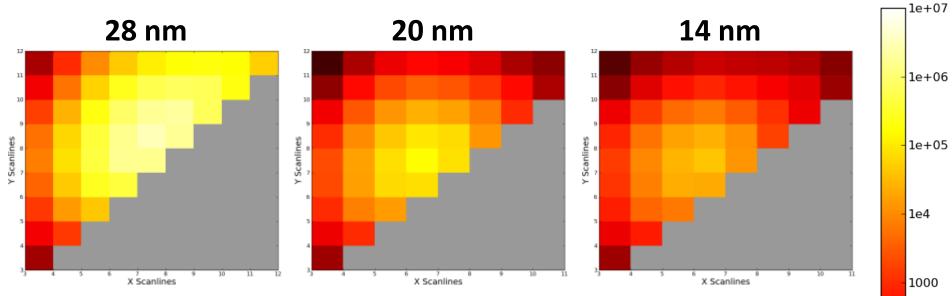

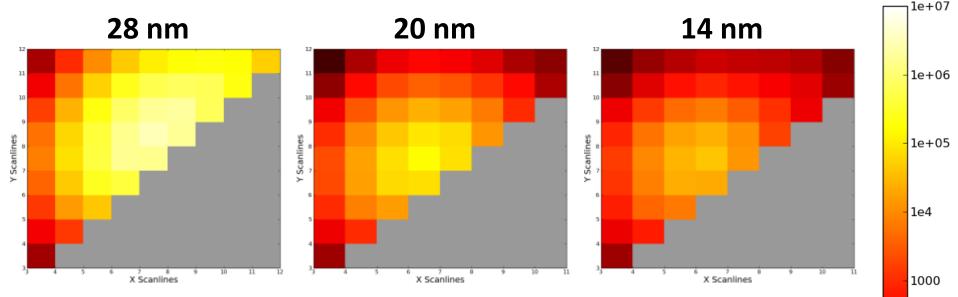

## EVOLUTION OF DESIGN TOPOLOGICAL COMPLEXITY AMDIA 1X METAL LAYERS, WINDOW = 3 METAL PITCHES, INEXACT MATCHES AMDIA

100

10

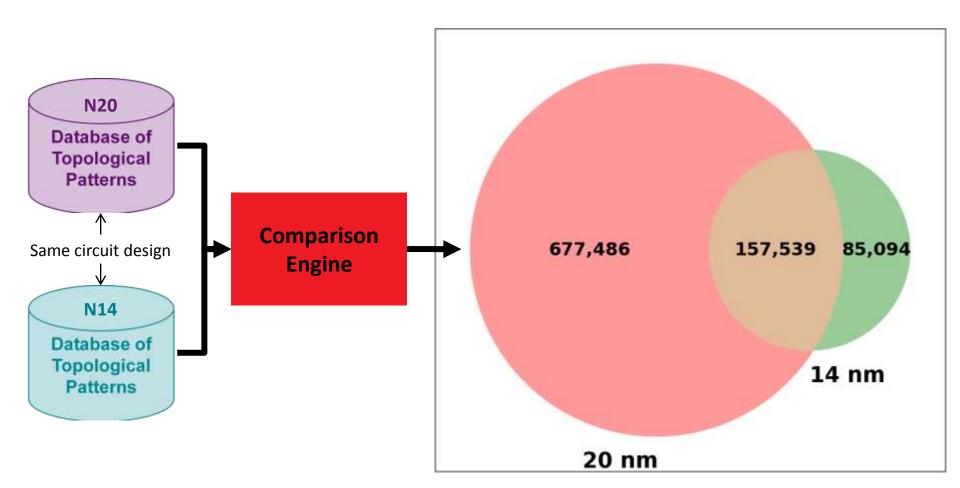

- ▲ The same circuit was implemented in 28, 20, and 14 nm technologies.

- Pattern extraction was run on each and the number of unique topologies was counted.

| Note the use of a log scale. | Technology Node | Total Unique Patterns |

|------------------------------|-----------------|-----------------------|

|                              | 28 nm           | 20,718,038            |

|                              | 20 nm           | 835,017               |

|                              | 14 nm           | 242,617               |

## EVOLUTION OF DESIGN TOPOLOGICAL COMPLEXITY 1X METAL LAYERS, WINDOW = 3 METAL PITCHES, INEXACT MATCHES

- ▲ An order of magnitude decrease in the design complexity (as measured by the number of unique topologies) of 1x metal layers from 28nm to 20nm.

- Shift to double patterning

- Some metal routing complexity shifted to local interconnect

- Additional decrease of ~4× from 20nm to 14nm despite the fact that 1x metal design rules are very similar.

- Shift to FinFET devices and impact of increased regularity of front end

100

10

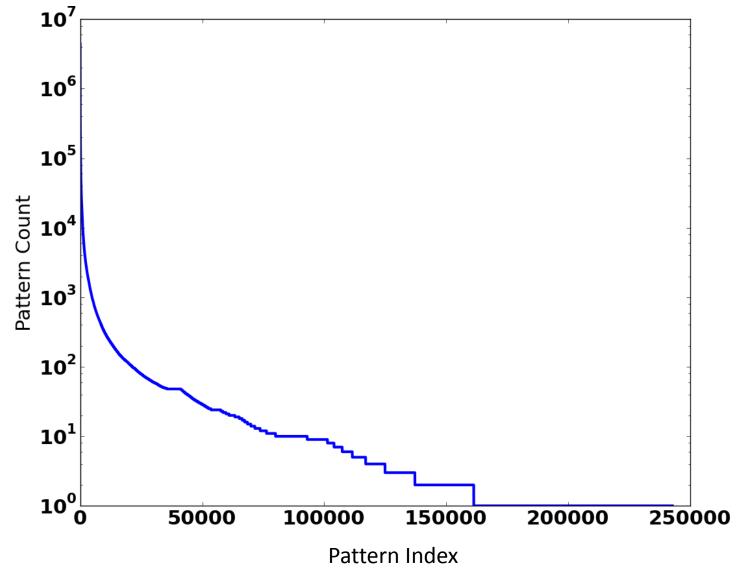

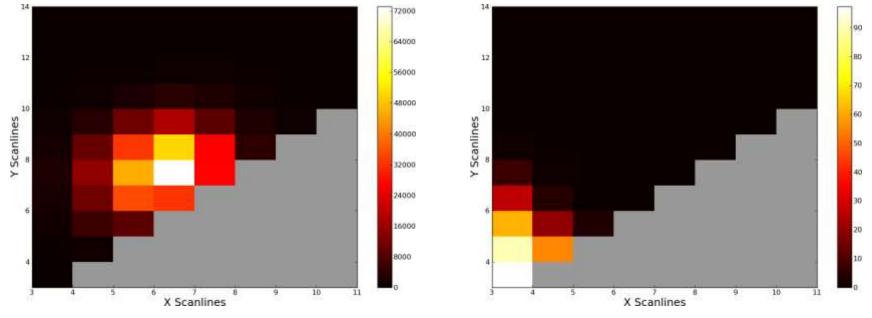

## DISTRIBUTION OF TOPOLOGY COUNTS 14NM DIGITAL BLOCK, 1X METAL LAYERS

## cādence<sup>°</sup>

## PATTERN SPACE SIZE

| X | Y  | Total Possible | Reduced Space* |

|---|----|----------------|----------------|

| 3 | 3  | 512            | 38 (7%)        |

| 3 | 4  | 4,096          | 299 (7%)       |

| 3 | 5  | 32,768         | 1,716 (5%)     |

| 3 | 6  | 262,144        | 9,044 (3%)     |

| 3 | 7  | 2,097,152      | 49,610 (2%)    |

| 3 | 8  | 16,777,216     | 267,390 (2%)   |

| 3 | 9  | 134,217,728    | 1,452,652 (1%) |

| 3 | 10 | 1,073,741,824  | 7,864,304 (1%) |

| 4 | 4  | 65,536         | 1,900 (3%)     |

| 4 | 5  | 1,048,576      | 43,428 (4%)    |

| 4 | 6  | 16,777,216     | 479,491 (3%)   |

| 4 | 7  | 268,435,456    | 5,202,792 (2%) |

| 5 | 5  | 33,554,432     | 500,948 (1%)   |

The number of possible patterns in each topological family grows very rapidly with topological complexity.

\*Reduced space removes duplicates due to rotation or mirroring and non-physical patterns.

## cādence

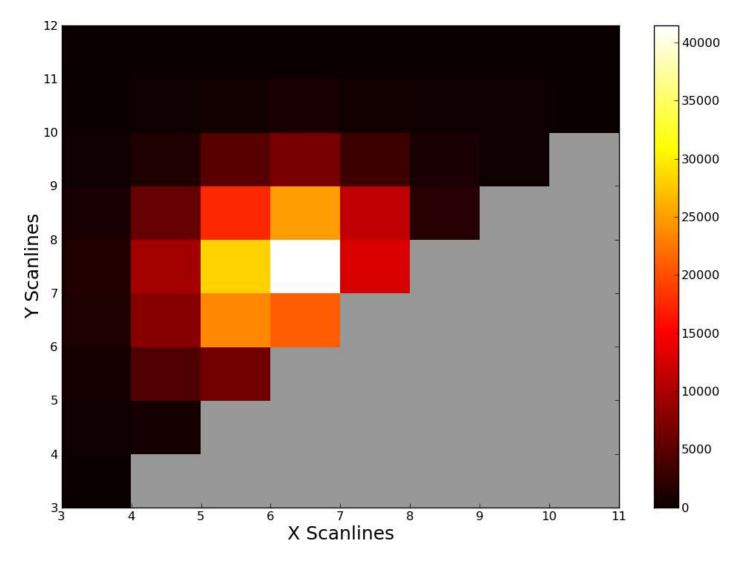

## PATTERN SPACE COVERAGE 1X METAL LAYERS, WINDOW = 3 METAL PITCHES, EXACT MATCHES

Pattern Space Coverage [%]

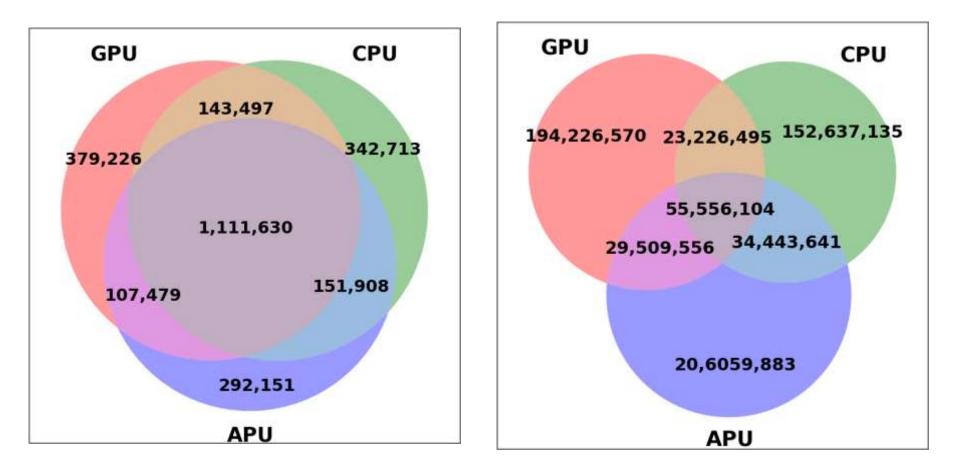

### 14nm APU (CPU + GPU + Northbridge etc.) product design

Pattern Counts

- Despite the highest raw count of unique patterns occurring for pattern topologies in the 6×7 family the coverage of the total pattern space is quite low in that region.

- ▲ Pattern coverage near 100% for basic topologies (3×3) but drops off quickly.

## **IDENTIFICATION OF LAYOUT DIFFERENCES**

#### Ianh overlay.oas / merged\_layouts And Mundae lectron March File Windows Tools from Patro X: 434.980 Y: 401.300 marlus.me Door Data leleit fall Use cases lage firsts 40 and Rollin Identify regions where customer has 1. modified sensitive IP 2. Give OPC engineers regions that overlay.oas need more analysis Close Data Select Cell Feed forward monitoring points to 3. Open merged\_lay Close Cell process teams and FA Clear Orig Hlt Layer Display 4. Give entire team an indication of Cell Display Text Display how difficult a new tape-out will be, Text on Layer Inst Property especially ramping up a new OA: overlay.oas: 99 process ■ Oas : F G Done

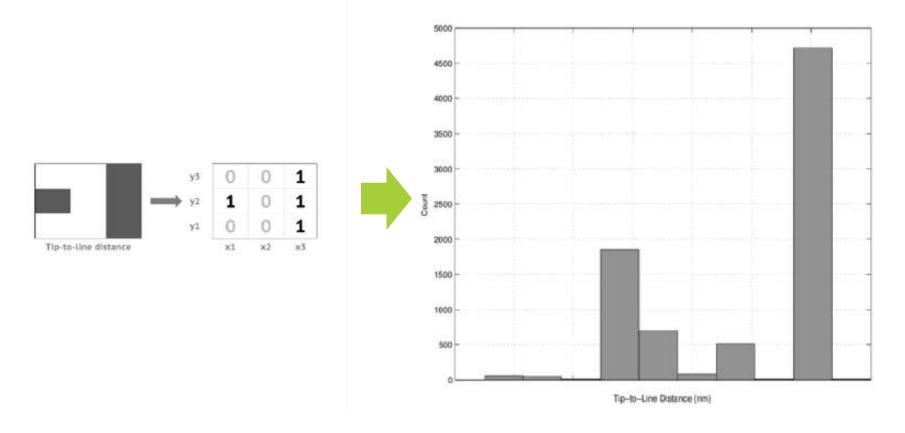

## How do we define what is "new"?

- 1. Topologically Different: Patterns that have never been seen before

- 2. <u>Dimensionally Different:</u> Patterns whose dimensions are outside the range of what has been seen before

## cādence

## HOW CAN WE IDENTIFY WHAT IS "NEW" IN AN INCOMING DESIGN THAT WE HAVE NEVER SEEN BEFORE?

Pattern Capture

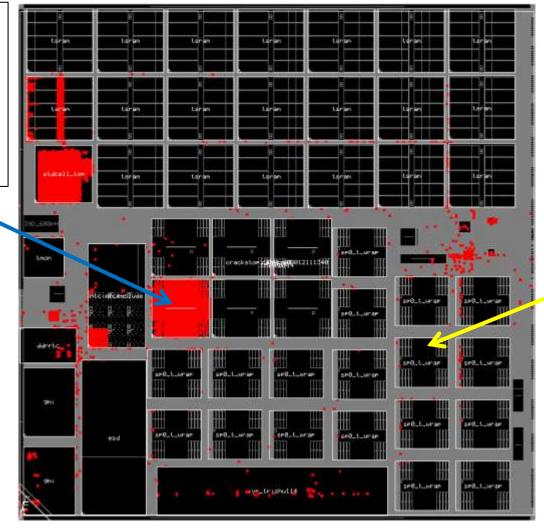

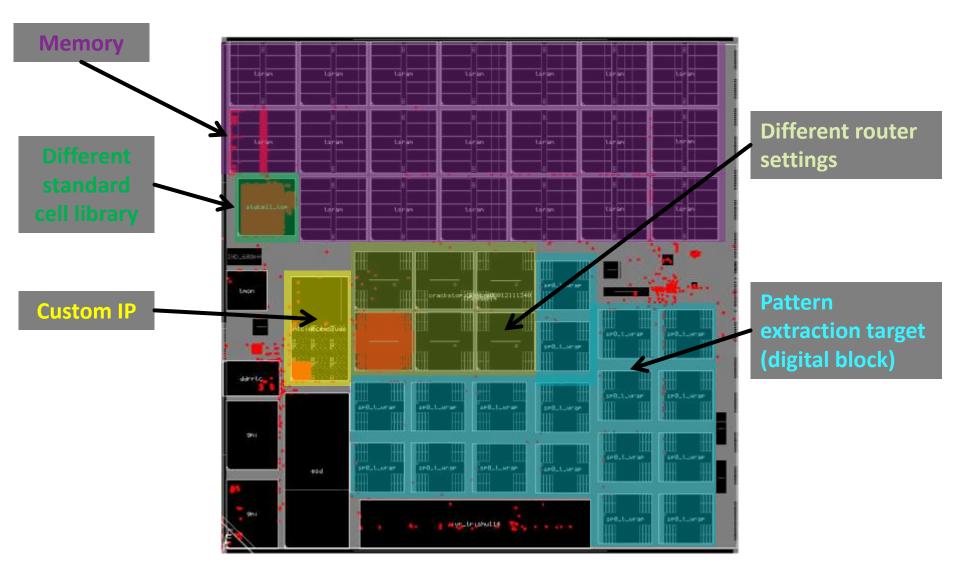

## AUTOMATIC IDENTIFICATION OF REPRESENTATIVE LAYOUT DIFFERENCES

Each red point is a representative pattern present only in new design

Pattern extraction target (digital block)

## cādence<sup>°</sup>

## AUTOMATIC IDENTIFICATION OF REPRESENTATIVE LAYOUT DIFFERENCES

## cādence<sup>°</sup>

## **TOPOLOGICAL DESIGN COMPARISON** 1X METAL LAYERS, WINDOW SIZE = 3 METAL PITCHES, INEXACT MATCHES

cādence

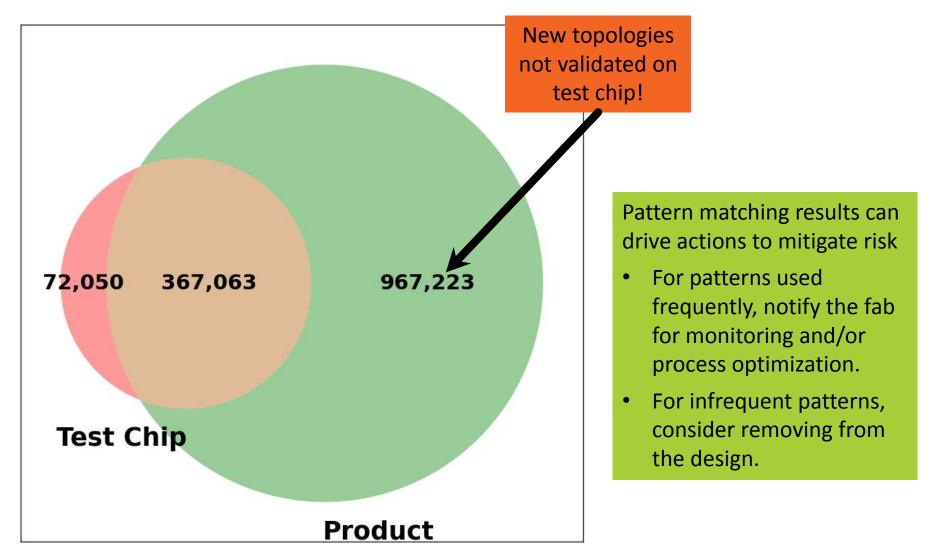

## COMPARISON OF TEST CHIP TO PRODUCT TOPOLOGIES AMD

Once patterns captured, comparisons performed in < 1 hour</p>

19 | SPIE ADVANCED LITHOGRAPHY | FEBRUARY 24, 2016

## COMPARISON OF PRODUCT DESIGN STYLES 1X METAL LAYERS, WINDOW SIZE = 3 METAL PITCHES

## **Inexact matching**

## **Exact matching**

## cādence<sup>°</sup>

- Topological pattern analysis provides powerful tools for measuring physical design complexity.

- Pattern extraction can be used to identify all unique pattern topologies (with or without specific dimensions) in a layout.

- Measurable decrease in 1x metal design complexity from 28nm to 20nm to 14nm confirms that layouts are becoming more regular.

- Extracted pattern topologies can be compared between layouts to identify differences and commonalities.

- May be used to identify potential risks and/or drive improved layout regularity.

# AMDJ

## **DISCLAIMER & ATTRIBUTION**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **ATTRIBUTION**

© 2015 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.