Developing secure loT systems as fast as possible

Cadence and Arm Seminar 2018

Petach Tikvah, Israel

Phil Burr, Director, Embedded Portfolio, Arm Bernd Reinkemeier, Senior Technical Executive, Cadence July 2018

cadence®

110

101

100

100

001 101

01

01

01

110

101

### What are today's embedded and IoT challenges?

- Extreme low-power

- Integration complexity

- Many elements

- Logic, memory, flash, mixed signal, RF, power, sensors...

- Long life, in remote location

- Security

- Very low cost

### **Challenges vary across types of devices**

#### Constrained

#### Mainstream

#### Rich IoT nodes & gateways

- Ultra-low-cost, simple sensors

- Often battery powered

- Connecting to gateway or cloud

- Balancing performance and cost

- Moderate data or audio capabilities

- High power efficiency

- High levels of data processing at edge

- Autonomous decision making or machine learning

- Providing gateway to cloud

### Security is a common challenge across all devices

#### Constrained

Mainstream

Rich IoT nodes & gateways

© 2018 Arm Limited

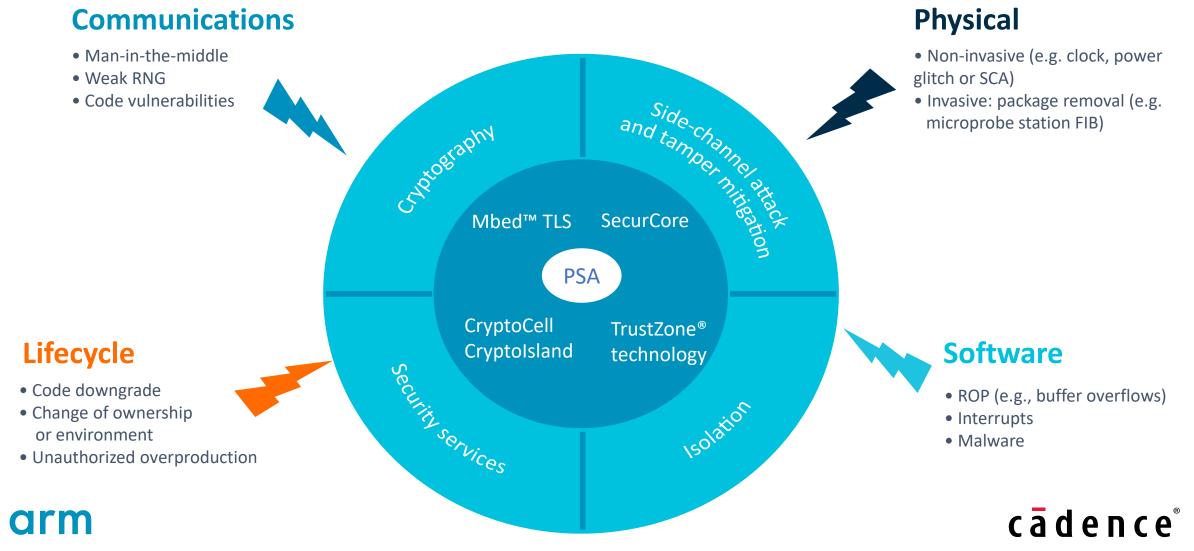

### **Arm's Platform Security Architecture (PSA)**

Consistently design in the right level of security into low-cost IoT devices

cādence<sup>®</sup>

### What are we protecting against? Threat modelling

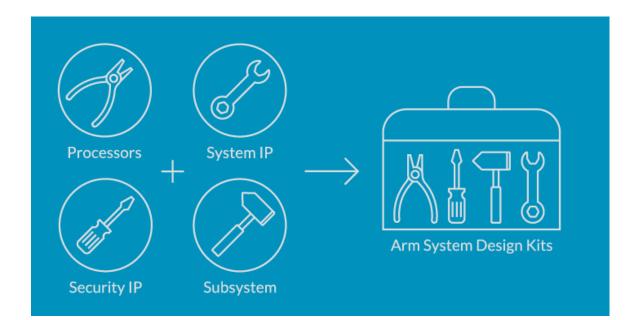

#### **Arm SoC solutions: A complete toolbox for SoC designers**

- Standardized interfaces and architecture, common software development

- Pre-verified and pre-integrated foundation

- Extendable for differentiation and diversity of applications

- Bring your secure SoC to market fast, with lower risk

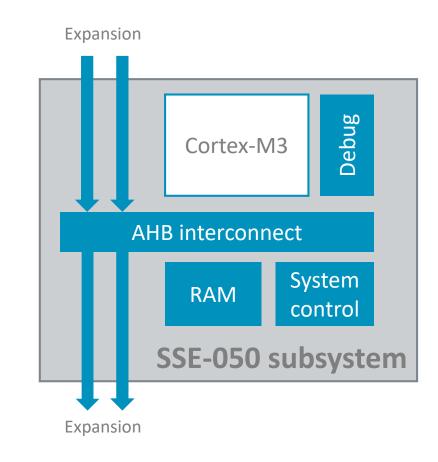

#### There are subsystems for each class of device

Constrained

Mainstream

Rich IoT nodes & gateways

SSE-050 SSE-200 SDK-700

cādence°

#### SSE-050 subsystem (part of SDK-101 / SDK-200)

#### A fast way to start in IoT

Compact

• Based on Cortex-M3

#### Good starting point

#### Software support

- Mbed OS

- Other RTOS

cādence

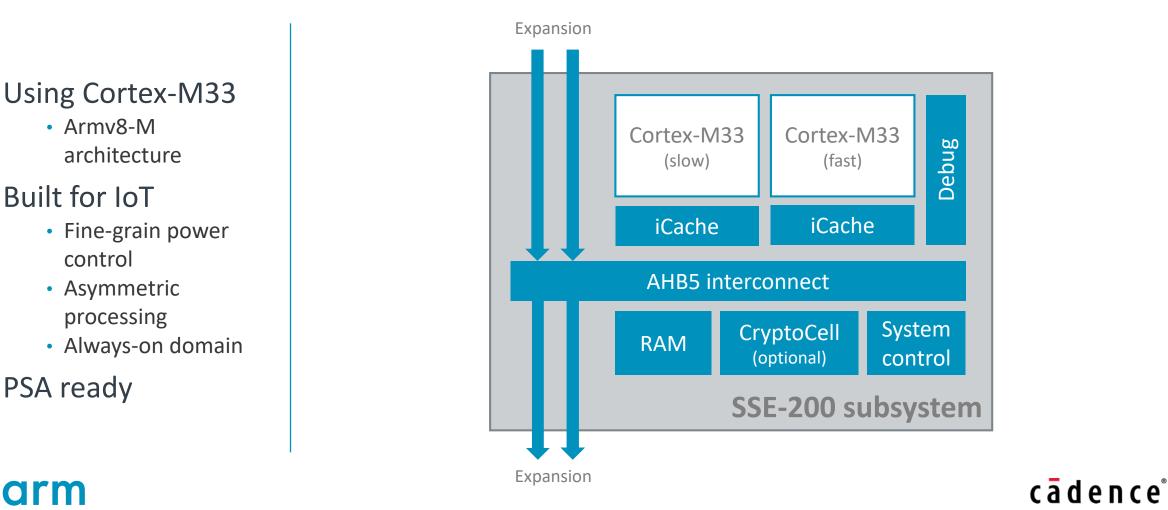

#### SSE-200 subsystem (part of SDK-200)

#### A reference system to build secure systems with TrustZone technology

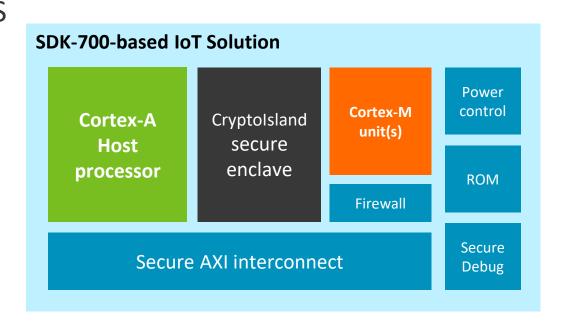

#### **Arm SDK-700 System Design Kit**

A new flexible SoC solution for rich IoT nodes and gateways

• Flexible compute

Arm<sup>®</sup> Cortex<sup>®</sup>-A – performance & rich OS Arm Cortex-M – real-time & highest efficiency

- Secure SoC foundation

Supports Microsoft Azure Sphere

- Built on PSA principles

Secure system architecture

Common software architecture

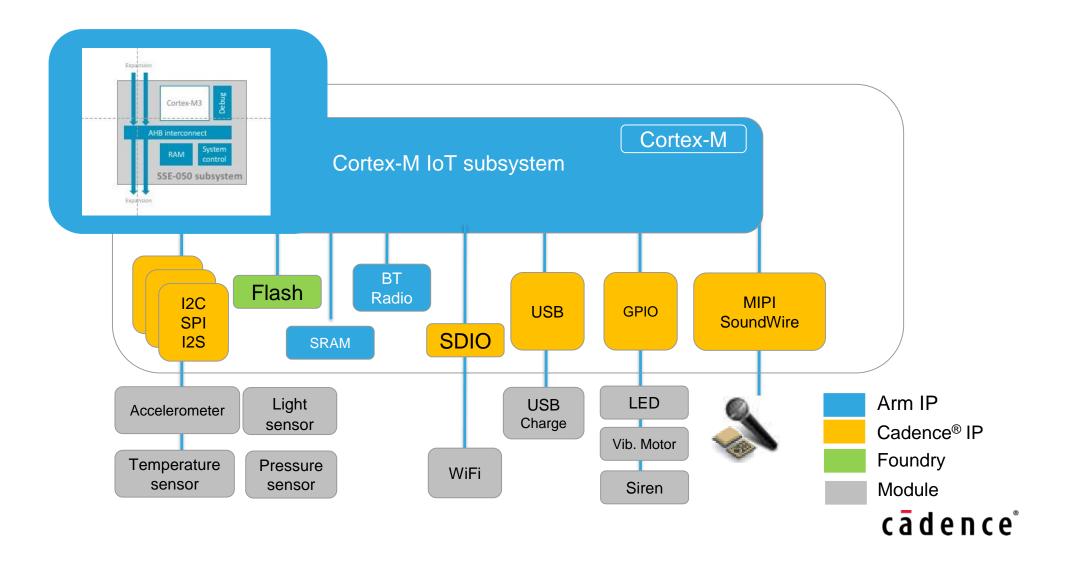

#### **Extending Arm's subsystem with Cadence IoT IP**

arm

# Cadence Rapid Adoption Kit (RAK) for Arm Cortex-M23 and Cortex-M33

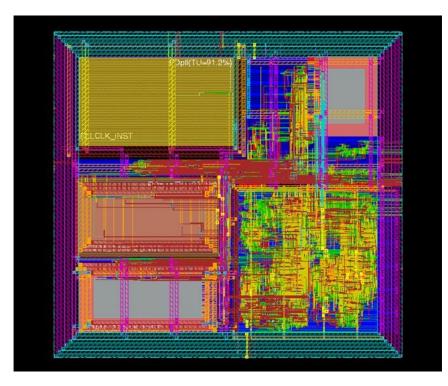

- Quick path to implementation via a full-flow digital and signoff reference methodology that provides optimal power, performance and area (PPA)

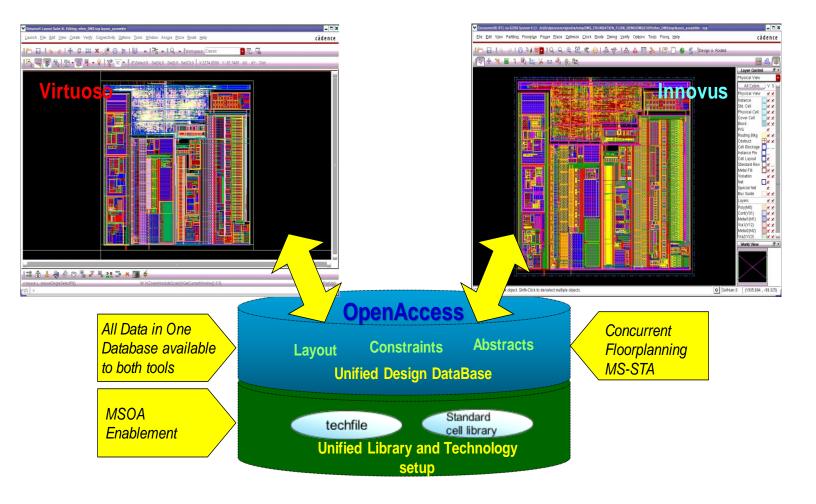

- Achieve fast runtimes and efficient design closure through the integrated Cadence RTL2GDS

- Implement IoT devices using the complete Cadence low-power flow: design, verification, implementation

### For accessing Cadence RAKs, contact your local Cadence office and support AE

### Building a chip yourself? Use Arm DesignStart<sup>™</sup> portal

Fast access to industry-leading processor IP and physical IP – for no upfront fee

- Simple, quick web-based access to Arm IP

- Leading Cortex-M processors and subsystems

- System design kits with pre-verified subsystems for faster development

- Access to Cadence tools, support, and methodologies in Hosted Design Solution chamber

- 1000s of physical IP libraries

- Used in 1000s of SoC designs

designstart.arm.com

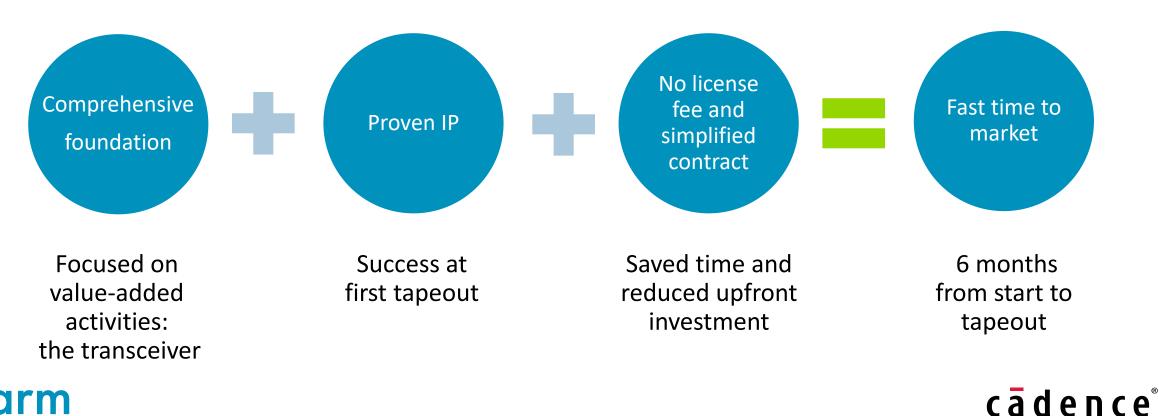

### Case study: Speeding time to market with proven Arm IP

More than connection

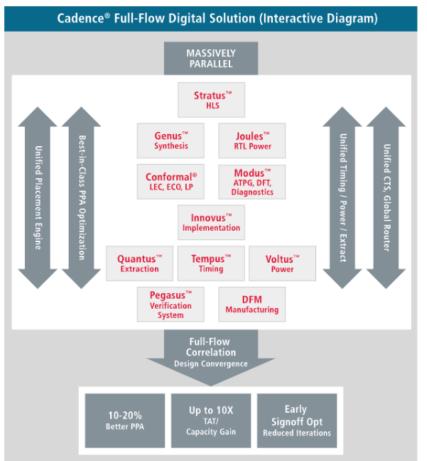

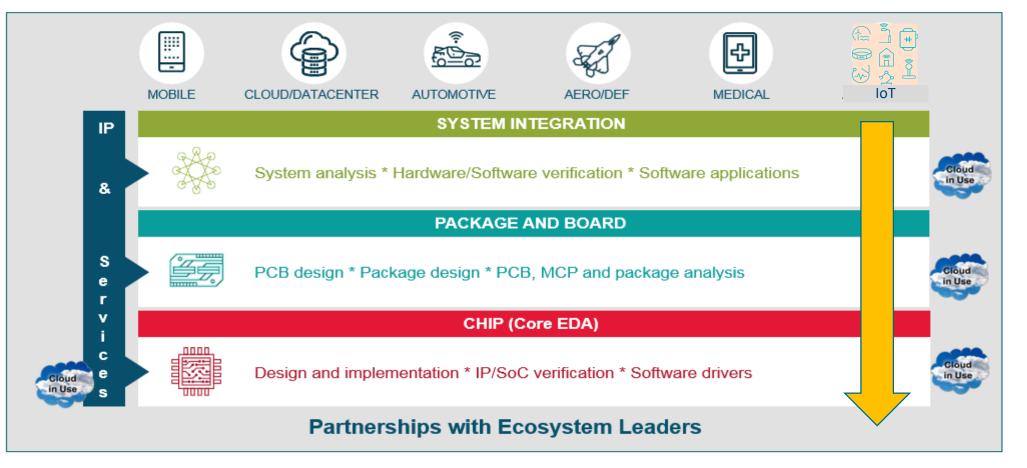

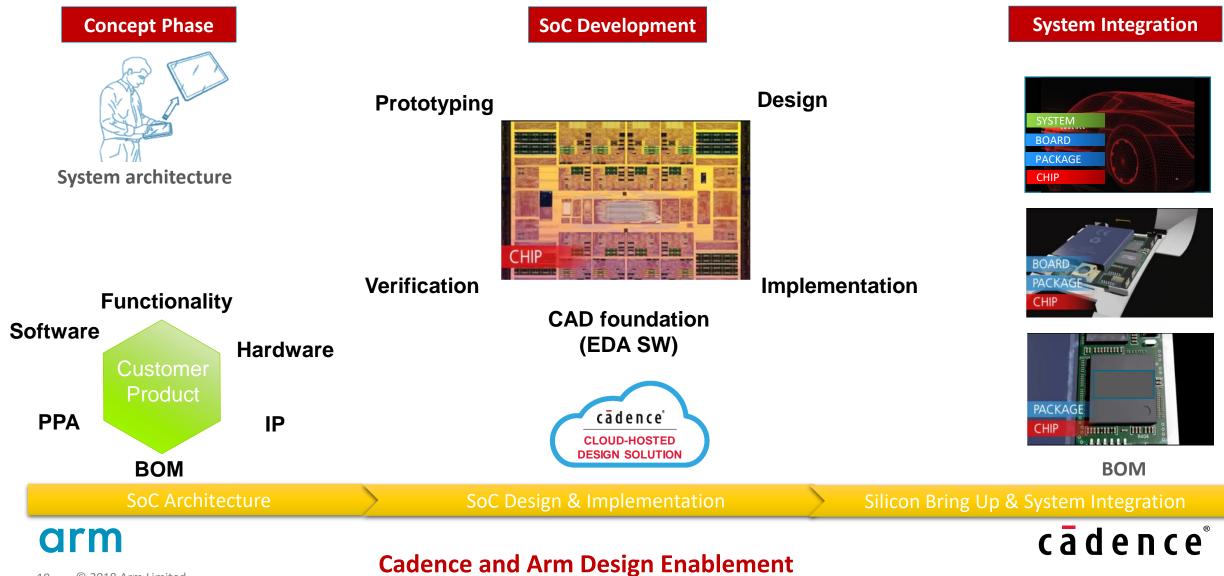

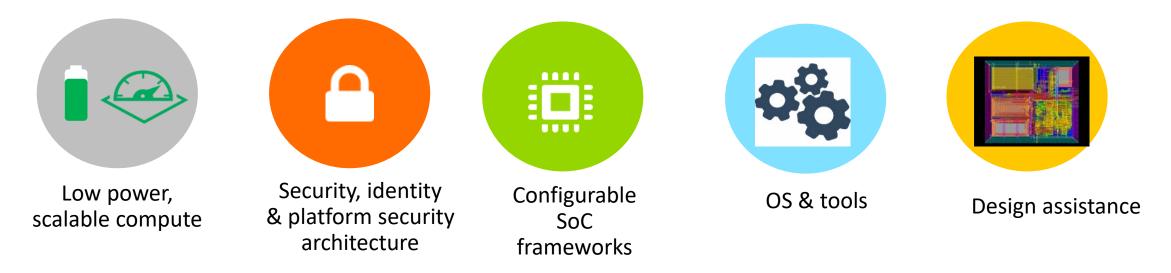

### **Cadence System Design Enablement**

Holistic and scalable design solution for enabling IoT differentiated products

cādence®

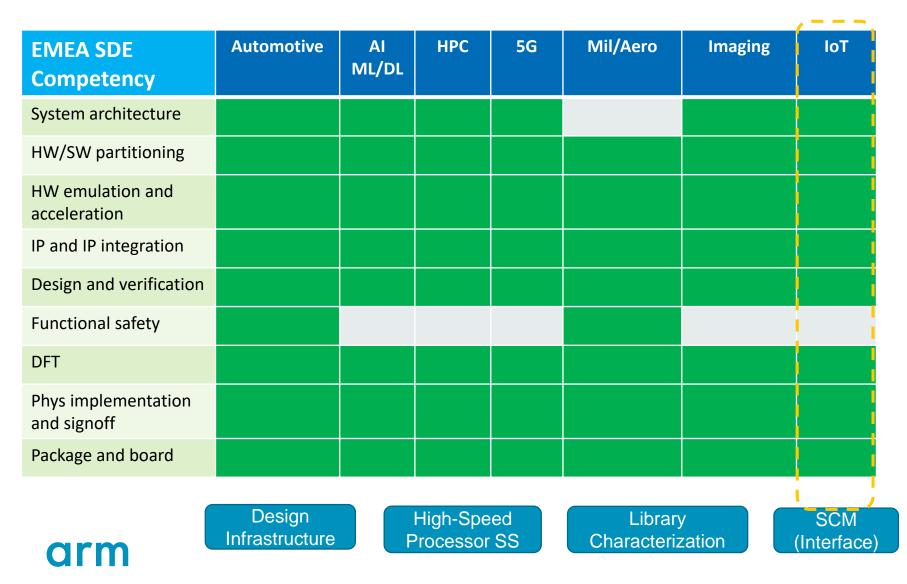

### **Cadence SDE: Vertical markets enablement**

cādence

#### **Reduce complexity, risk, and cost**

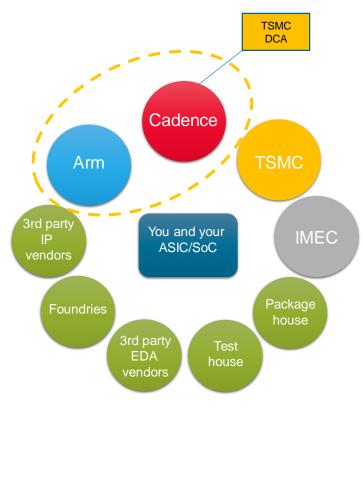

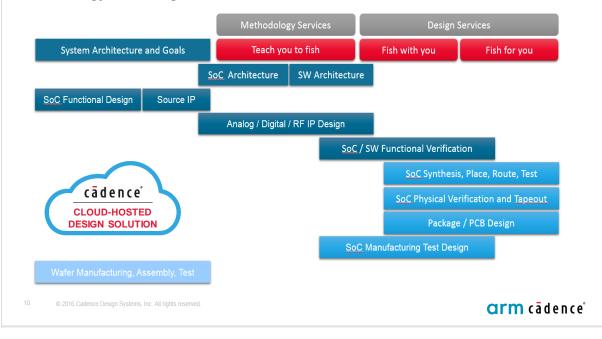

### **Need SoC design help?**

#### Need SoC Design Help?.. Cadence Can Help! Methodology and Design Services

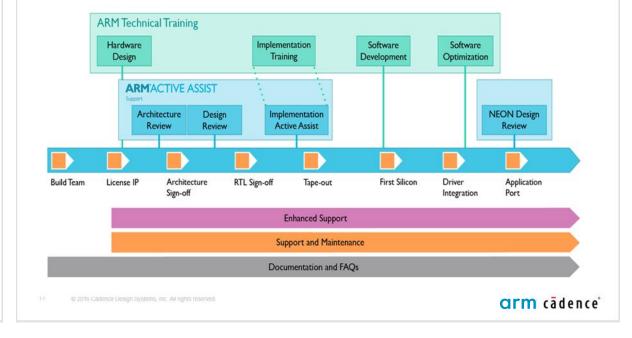

#### Need SoC Design Help?.. ARM Can Help!

The help you need, when you need it

### Some key risks in ASIC/SoC design – Cadence can help you

#### **Risk area**

- Design complexity rising

- RTL-GDSII implementation

- IC-package-board co-design

- Hardware-software coherence

- Analog/mixed to digital interfacing

- IP integration

#### **Cadence offers**

- One of the strongest SoC verification methodology & services teams in the industry

- RTL-GDSII implementation methodology

- 200+ tapeouts in last 5 years, spanning 180nm to 3nm! Many Arm-based designs.

- SI/PI/thermal analysis and optimization

- SoCs stress testing

- Analog/mixed-signal/RF design & verification

- A broad IP portfolio with integration support

c a d e n c e<sup>®</sup>

### There is mixed signal in IoT

Source: 2013 © Semico Research Corp. All Rights Reserved System(s)-on-a-Chip: Changes in SoC Design Methodology

## Reasons for re-spins in analog mixed-signal SoCs

- 1. Logical and functional errors

- 2. Clocking issues

- 3. Analog–digital interfaces

- 4. Crosstalk

- 5. Power management

- 6. Analog circuits

- 7. Yield/reliability

- 8. Timing

- 9. Firmware

- 10. IR drops

### **Cadence solution for mixed signal**

**Cadence Mixed-Signal Flow has produced many thousands of successful tapeouts**

Cadence Mixed-Signal Methodology Guide ISBN: 978-1300035206

arm

# IoT is quicker, easier and more flexible with Arm Cadence design solutions

Arm: System-level solutions to simplify IoT development and deployment: Secure, scalable, configurable, and power efficient

Cadence: Low-power solution, IoT System Design Enablement (IP, software, hardware, methodology, design services), cloud-hosted design solution

**Thank You** Danke Merci 谢谢 ありがとう Gracias **Kiitos** 감사합니다 धन्यवाद תודה

## arm

# arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks